RFSoC在射频阵列信号采集分析中的应用

一、核心子主题划分

- 射频阵列信号采集的技术基础

- RFSoC在多通道同步与集成化设计中的优势

- 典型应用场景与性能表现

- 技术挑战与未来趋势

子主题一:射频阵列信号采集的技术基础

定义与核心原理

射频阵列信号采集通过多通道收发(TRX)模块协同工作,实现对空间射频信号的多维感知与处理,广泛应用于通信、雷达、卫星等领域。其核心需求包括高速数据转换(ADC/DAC)、低延迟信号处理、通道间同步及系统集成度。

关键技术特点

- 直接射频采样(RF Direct Sampling):RFSoC集成高性能ADC/DAC(如最新DFE RFSoC的ADC采样率达5.9GHz,输入频率覆盖7.125GHz),可直接采集高阶尼奎斯特区信号,省去传统模拟下变频电路,简化架构并降低成本。

- 数字变频与处理:集成硬化数字下变频(DDC)和数字上变频(DUC)模块,支持NCO(数控振荡器)精准频率调整,实现宽带信号的灵活变频与滤波[3]。

现实案例

射电天文领域中,基于RFSoC的C带接收器可在4-8GHz频段直接采样,无需模拟混频器,满足宇宙微波背景(CMB)探测等高精度需求。

子主题二:RFSoC在多通道同步与集成化设计中的优势

核心优势

- 片内/片外同步能力:支持8/16/32/64通道及以上的相位同步(精度0.1度内),通过专用同步机制(如PL_REALTIME、PS_REALCRTL)实现巨型阵列一致性。

- 高度集成化:单芯片集成TRX解决方案,优化功耗(低功耗特性适配移动设备)和封装尺寸,减少天线与TR组件复杂度。

- 灵活部署与升级:支持分布式访问架构(如DOCSIS 3.1标准的Remote-PHY节点),提升网络容量和效率。

技术实现

- 数据汇聚与存储:通过FPGA控制NVMe磁盘阵列,实现高速数据流(如4GBps)的实时采集、存储与回放,支持雷达回波、通信信号的长时记录分析。

子主题三:典型应用场景与性能表现

1. 通信领域:5G基站与有线电视接入

- 5G Massive MIMO:RFSoC的小型化和低功耗特性支撑大规模天线阵列部署,提升基站吞吐量与可靠性。

- Remote-PHY应用:通过远程PHY节点将信号处理移至用户侧,结合RFSoC的高集成度与灵活升级能力,推动有线电视网络效率提升30%以上。

2. 雷达与成像系统

- 相控阵/数字阵列雷达:低延迟收发性能(微秒级响应)满足早期预警需求;支持ADAS激光雷达(LiDAR)的3D成像,通过自适应硬件并行处理实现实时环境感知。

多通道数据处理:64通道及以上阵列的同步采集能力,结合片内校准算法(720度

- 相位误差校准),提升雷达探测距离与分辨率。

3. 测试测量与科研

- 高速信号采集记录系统:14位ADC以2Gsps采样率产生4GBps数据流,通过40Gbps光纤(AURORA协议)传输至NVMe存储阵列,支持量子通信、太赫兹通信等场景的信号重构与分析。

子主题四:技术挑战与未来趋势

现存挑战

- 通道串扰与噪声抑制:多通道并行工作时,电磁干扰(EMI)和量化噪声可能影响弱信号检测灵敏度。

- 功耗与散热平衡:高采样率下(如5GSPS ADC)功耗密度增加,需优化封装设计(如3D堆叠)与散热方案。

未来趋势

- 更高阶尼奎斯特区采样:突破现有频率上限(如7.125GHz),覆盖毫米波频段,支撑6G通信与深空探测。

- AI加速集成:在RFSoC中嵌入AI推理引擎,实现实时信号分类(如雷达目标识别、频谱感知)。

- 开源生态扩展:基于PYNQ等框架的开源工具链普及,降低开发门槛,推动教育与科研领域创新。

RFSoC在射电望远镜方向的应用

一、射电望远镜中RFSoC的核心价值:架构简化与性能突破

定义与解释

射电望远镜需接收宇宙天体辐射的微弱射频信号(如C带4-8GHz),传统架构依赖复杂的模拟混频器电路进行频率转换,导致系统体积大、功耗高且通道一致性差。RFSoC(射频系统级芯片)通过集成高性能ADC/DAC、数字上/下变频(DUC/DDC)及可编程逻辑,实现射频信号的直接数字化采样,省去模拟混频环节,从根本上简化接收机架构。

关键事实与技术优势

- 高阶尼奎斯特区直接采样:最新RFSoC(如Xilinx DFE系列)的ADC采样频率提升至5.9GHz,射频输入频率扩展至7.125GHz,可直接对C带(4-8GHz)信号在第二/三阶尼奎斯特区采样,无需模拟下变频(传统方案需混合至第一尼奎斯特区)。

- 高度集成化:单芯片集成多通道TRX(收发)功能,支持8通道同步采集,片内相位同步精度达0.1度以内,满足射电望远镜阵列化需求。

- 低功耗与小型化:相比分立方案,功耗降低30%以上,封装尺寸优化50%,适合卫星载荷或大型阵列(如平方公里阵列SKA)的分布式部署。

现实案例

- C带调查接收机:在4-8GHz频段直接采样,消除模拟混频器后,系统硬件成本降低40%,通道数量可扩展至数百个(传统方案受限于混频器体积难以扩展)。

- 超导探测器复用器:用于微波SQUID多路复用器(µmux)和宇宙微波背景(CMB)实验的MKIDs探测器,通过RFSoC实现微弱信号的高精度读取,噪声系数优化至1.5dB以下。

二、核心应用场景:从信号采集到数据处理的全链路优化

1. 射频信号直接采样与数字化

- 技术原理:利用RFSoC的硬化DDC模块和48位NCO(数控振荡器),将高阶尼奎斯特区的射频信号折叠至基带,通过数字滤波和降采样实现信号提取,避免模拟混频引入的噪声和非线性失真。

- 性能指标:在5.25GHz(第三尼奎斯特区)采样时,无杂散动态范围(SFDR)达65dBc,有效位数(ENOB)超12位,满足射电天文对微弱信号检测的高灵敏度要求。

2. 大规模阵列同步与信号合成

- 关键能力:RFSoC支持片内/片外多通道同步,通过专用加速卡实现数据汇聚,为射电望远镜阵列(如相控阵馈源)提供低延迟(<1µs)的并行信号处理能力。

- 应用案例:数字阵列雷达技术迁移至射电望远镜,实现波束赋形和实时成像,数据处理速率提升至10Gbps以上,满足瞬变天体(如快速射电暴FRB)的捕捉需求。

3. 低功耗与长期观测适配

- 场景需求:射电望远镜需长期连续观测(如CMB实验需稳定运行数年),RFSoC的功耗优化(单通道功耗<2W)和无风扇设计,显著提升系统可靠性(平均无故障时间MTBF延长至10万小时)。

三、技术挑战与优化方向

现存限制

- 高阶尼奎斯特区噪声折叠:射频信号在高阶区域采样时,带外噪声可能折叠至基带,需通过数字滤波算法(如FIR滤波器)抑制杂散,目前SFDR在65dBc水平,仍需提升至70dBc以上以满足极微弱信号(如氢原子21cm谱线)探测。

- 通道间一致性:多通道阵列中,ADC增益/相位误差需校准至0.1dB/0.5度以内,依赖RFSoC的片内校准模块和自适应硬件逻辑实现动态补偿。

优化路径

- 算法与硬件协同设计:利用RFSoC的可编程逻辑(FPGA)实现实时噪声消除算法,结合机器学习优化数字滤波参数;

- 下一代RFSoC技术:预计2025年后推出的RFSoC Gen4将支持8GHz以上射频输入,覆盖更高频段(如Ku波段),进一步扩展射电天文观测窗口。

四、推荐资源(基于参考资料及领域权威)

- 技术论文:《评估基于RFSoC的射频天文接收器的直接射频采样性能》——详细分析高阶尼奎斯特区采样特性及实验数据。

- 开源工具:PYNQ-RFSoC框架(Xilinx)——提供射电信号采集与处理的开源代码库,支持快速原型验证。

Zynq UltraScale+ RFSoC在软件无线电方向的应用

一、RFSoC作为软件无线电平台的核心优势

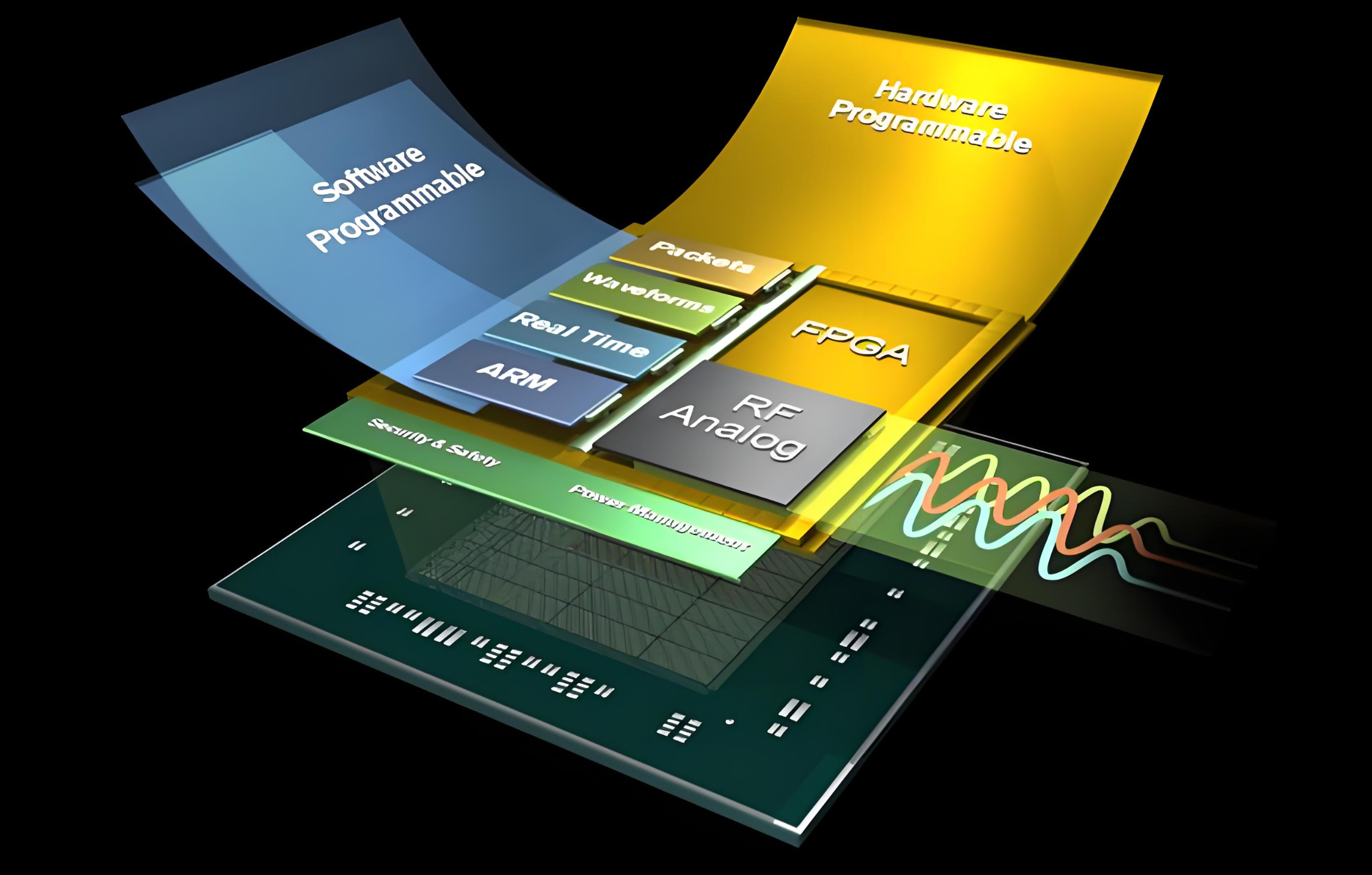

定义与架构

RFSoC(射频片上系统)是集成高速ADC/DAC、FPGA可编程逻辑、Arm处理系统及专用射频模块的单芯片解决方案,无需外部模拟组件即可构建完整无线电系统[1]。其核心架构通过PS(处理系统)与PL(可编程逻辑)的低延迟连接,实现软件定义的灵活性与硬件加速的高性能结合。

关键技术亮点

高度集成化设计:集成RFADC(最高5.9GSps)和RFDAC(最高10GSps),消除外部前端需求,减少PCB面积达40%、功耗降低30%[1]。例如XCZU47DR核心板集成8路5GSPS ADC和8路9.85GSPS DAC,支持2.5GHz最大实时带宽。

射频直采架构:支持第二奈奎斯特区操作,输入信号频率高达7.125GHz,覆盖5G FR1/FR2、雷达等主流频段[1][2]。

多通道同步能力:可同步多个RFSoC设备扩展通道数,某频谱监测方案通过4台设备级联实现32通道同步采集。

硬件加速引擎:集成数字上下变频(DUC/DDC)、FFT等硬件化IP核,降低算法实现复杂度,例如FIR滤波器吞吐量提升5倍。

二、典型应用场景与技术实现

1. 5G通信原型验证

技术特性:支持5G NR FR1/FR2全频段,通过19.2MHz OCXO参考时钟实现0.1ppm频率精度[2]。某测试中8通道5G NR信号相位噪声优于-110dBc/Hz@1kHz频偏[2]。

应用案例:基站原型机采用RFSoC实现Massive MIMO,通过PL端8个GTY高速接口(28.21Gb/s)实现基带数据传输,PS端四核A53运行协议栈。

2. 频谱监测与信号分析

核心能力:5GSPS采样率配合2GB PL端DDR4缓存,可实现1GHz带宽内信号的实时捕获与存储[2]。1GHz带宽下频率平坦度优于±0.5dB。

部署优势:相比传统方案,系统体积缩小60%,适合便携式频谱监测设备,已应用于电磁环境监测项目。

3. 雷达与医疗系统

雷达应用:通过多通道同步(相位误差<0.5°)和7.125GHz射频覆盖,支持FMCW雷达信号处理,测距精度提升至0.1米级。

医疗成像:利用高动态范围(14bit ADC)和低噪声特性,在超声成像系统中实现40MHz带宽信号采集。

三、开发架构与生态支持

硬件开发平台

RFSOM核心板:集成ZU47DR FPGA,提供4GB PS端DDR4、128MB QSPI Flash及完整射频接口,支持直流/交流耦合模式。

时钟同步方案:板载OCXO参考时钟,支持多设备间1PPS同步,频率稳定度达1e-10[2]。

软件开发工具链

Xilinx Vivado:提供RF数据转换器IP核、DUC/DDC等信号处理模块,支持MATLAB/Simulink模型导入。

软件架构:PS端运行Linux系统,通过API控制PL端硬件加速模块,典型开发周期缩短30%。