MEMS与CMOS的3D集成技术研究进展

随着物联网、人工智能和5G/6G通信的快速发展,传统二维集成技术面临性能瓶颈和物理限制。MEMS与CMOS的3D集成技术作为"超越摩尔"的重要发展方向,通过垂直堆叠和异质集成,实现了性能提升、尺寸缩减、功能增强的综合优势。这种集成方式将传感、处理、通信等功能在三维空间内有机融合,为下一代智能微系统奠定了技术基础。

一、3D集成的核心价值与挑战

1.1 技术优势分析

3D集成技术相比传统2D集成具有显著优势:

-

性能提升:缩短互连长度,降低寄生效应,提升信号传输速度

-

功能密度:单位面积内集成更多功能,实现真正的系统级芯片

-

异质兼容:允许不同工艺节点的芯片优化组合

-

功耗优化:减少长距离互连的功耗损失

1.2 主要技术挑战

| 挑战类型 | 具体问题 | 影响程度 |

|---|---|---|

| 热管理 | 功率密度增加,散热困难 | 高 |

| 应力控制 | 材料热膨胀系数不匹配 | 高 |

| 工艺兼容 | MEMS与CMOS工艺温度冲突 | 中 |

| 测试难度 | 堆叠后测试访问性差 | 中 |

| 成本控制 | 额外工艺步骤增加成本 | 高 |

二、主流3D集成技术方案

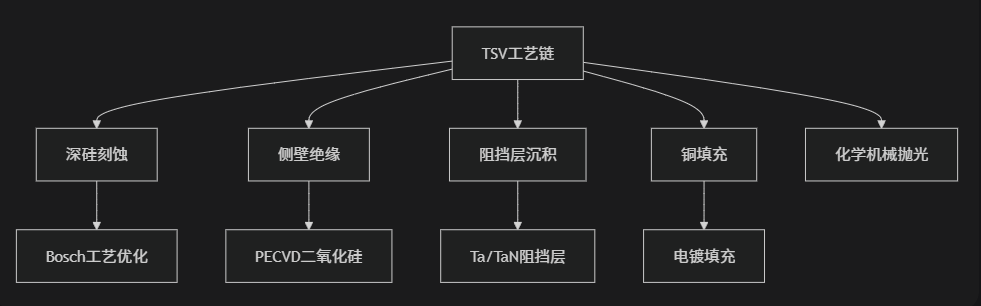

2.1 硅通孔技术

TSV是实现3D集成的核心技术,其工艺演进主要体现在:

关键技术参数进展:

-

孔径尺寸:从早期的50μm缩减至当前的1-5μm

-

深宽比:从5:1提升至20:1甚至更高

-

绝缘层:SiO₂厚度100-500nm,漏电流<1nA/cm²

-

填充材料:从多晶硅转向铜,电阻率降至2μΩ·cm

工艺优化重点:

2.2 单片3D集成

单片集成在同一晶圆上依次制造CMOS和MEMS,关键技术突破包括:

低温工艺开发:

-

CMOS先工艺:标准CMOS工艺完成后,最高温度限制在450℃以下

-

MEMS后工艺:采用低温沉积、刻蚀技术,避免影响前道器件

-

牺牲层材料:开发低温分解的聚合物牺牲层

典型工艺流程:

-

标准CMOS工艺完成

-

低温氧化物沉积作为保护层

-

MEMS结构层沉积与图形化

-

牺牲层释放(干法或湿法)

-

晶圆级封装完成

2.3 晶圆级键合技术

晶圆键合分为直接键合、中介层键合等不同技术路线:

直接键合进展:

-

表面预处理:CMP粗糙度<0.5nm

-

键合温度:从400℃以上降至室温键合

-

键合强度:达到体硅强度的80%以上

-

对准精度:<1μm(先进设备可达200nm)

中介层键合优势:

-

允许不同尺寸晶圆集成

-

提供额外的布线资源

-

缓解热应力问题

三、关键制造工艺突破

3.1 深反应离子刻蚀优化

TSV刻蚀工艺的持续改进:

Bosch工艺参数优化:

-

钝化时间:1-3秒,保证侧壁垂直度

-

刻蚀时间:2-5秒,控制刻蚀速率

-

SF₆/C₄F₈气体比例:精确控制侧壁形貌

-

温度控制:-20℃至-100℃低温刻蚀减少扇形缺陷

先进刻蚀技术:

-

Cryogenic DRIE:-100℃低温刻蚀,改善侧壁粗糙度

-

激光刻蚀:用于高深宽比TSV制备

-

电化学刻蚀:制备多孔硅牺牲层

3.2 铜填充技术突破

TSV铜填充的质量直接影响互连可靠性:

电化学沉积优化:

-

添加剂配方:加速剂、抑制剂、整平剂协同作用

-

电流密度:0.5-2 ASD,避免空洞形成

-

温度控制:25±1℃,保证填充均匀性

-

搅拌条件:优化对流保证离子补充

填充质量检测:

-

X射线检测:发现内部空洞缺陷

-

声学显微镜:检测界面分层

-

电阻测试:评估通孔导电性能

3.3 晶圆减薄与处理

晶圆减薄是3D集成的必要步骤:

减薄工艺组合:

-

粗磨:从775μm减至100μm

-

精磨:达到目标厚度±2μm

-

抛光:消除损伤层,粗糙度<5nm

-

湿法刻蚀:进一步减薄至15-50μm

薄晶圆处理:

-

临时键合:使用热滑移胶或激光释放胶

-

载体选择:玻璃、硅载体优化选择

-

解键合:热滑移、紫外激光或机械剥离

四、技术挑战与解决方案

4.1 热管理策略

3D集成的热密度问题需要创新解决方案:

热分析模型:

-

有限元分析:预测热点分布和温度梯度

-

热阻网络:建立等效热路模型

-

测试验证:红外热像仪实际测量

散热技术进展:

-

微流道集成:在硅中介层中制造冷却通道

-

导热通孔:高密度TSV阵列促进垂直散热

-

热界面材料:纳米银胶、石墨烯等高导热材料

4.2 应力管理与可靠性

不同材料热膨胀系数失配导致应力问题:

应力优化设计:

-

结构补偿:设计应力释放结构

-

材料选择:优化匹配热膨胀系数

-

工艺控制:降低工艺温度波动

可靠性测试:

-

热循环测试:-55℃至125℃,1000次循环

-

高温存储:150℃下1000小时寿命测试

-

机械测试:振动、冲击、拉力测试

4.3 电学性能优化

3D集成的电学特性需要特别关注:

信号完整性:

-

串扰控制:屏蔽TSV布局,减少耦合

-

阻抗匹配:优化传输线特性阻抗

-

电源完整性:分布式去耦电容设计

测试策略:

-

在片测试:晶圆级参数测试

-

堆叠测试:分层测试访问设计

-

系统测试:完整功能性能验证

五、典型应用案例

5.1 惯性测量单元

IMU的3D集成实现突破性进展:

技术特点:

-

结构:MEMS加速度计/陀螺仪+ASIC处理器3D堆叠

-

尺寸:相比2D集成减小60%以上

-

性能:串扰降低,噪声性能提升

-

应用:无人机导航、自动驾驶

实现方案:

-

TSV直径:3μm

-

堆叠层数:3-5层

-

互连密度:>10000 TSVs/cm²

5.2 光学MEMS系统

微镜阵列与驱动电路的3D集成:

技术突破:

-

单片集成:CMOS驱动与微镜同片制造

-

光学窗口:晶圆级光学封装

-

控制精度:数字控制精度提升至16位

-

应用领域:LiDAR、光学通信

5.3 射频MEMS器件

RF MEMS与CMOS的3D集成推动5G发展:

性能提升:

-

工作频率:提升至毫米波频段

-

插入损耗:降低0.5-1dB

-

隔离度:改善10-15dB

-

功率处理:提高功率容量

六、未来发展趋势

6.1 异质集成扩展

超越MEMS+CMOS的集成范畴:

-

光子集成:硅光器件与电子器件融合

-

生物芯片:微流控与传感处理集成

-

功率器件:GaN、SiC与硅基电路集成

6.2 先进互连技术

下一代互连技术研发方向:

混合键合:

-

铜-铜直接键合:无需凸点,间距<5μm

-

介质键合:SiO₂-SiON混合键合

-

低温工艺:<200℃实现高强度键合

无线互连:

-

近场耦合:芯片间电容耦合传输

-

毫米波通信:片上天线无线连接

-

光互连:硅光波导片间连接

6.3 设计方法学创新

应对3D集成复杂度的设计变革:

-

协同设计:MEMS与CMOS设计流程融合

-

热感知布局:早期热分析指导布局

-

测试架构:内置自测试和诊断功能

-

可靠性设计:从设计阶段考虑寿命预测

结语:迈向智能微系统时代

MEMS与CMOS的3D集成技术正在经历从实验室研究到产业化应用的关键转折。随着工艺技术的成熟和设计方法的完善,3D集成将成为高性能微系统的主流技术路线。未来,我们有望看到更多创新应用在人工智能、量子计算、生物医疗等前沿领域涌现。

这一技术发展不仅需要工艺工程师的持续创新,更需要设计、测试、封装等多领域的协同推进。只有通过全产业链的共同努力,才能充分发挥3D集成的技术潜力,开启智能微系统的新纪元。