FSMC-灵活的静态存储控制器

文章目录

- 1. FSMC的整体结构划分

- 2. 什么是Subbank?

- 3. 片选引脚NE[4:1]与Subbank的对应关系

- 3.1 NOR/PSRAM 地址映射

- 外部存储器总线宽度(8/16 位)与内部寄存器的 32 位访问

- 一、NOR/PSRAM 控制寄存器为何必须按32位访问?

- 二、FSMC 外部存储器总线宽度(8/16位)与内部寄存器的32位访问不冲突

- 三、总结:“内部32位寄存器”与“外部8/16位总线”的协同逻辑

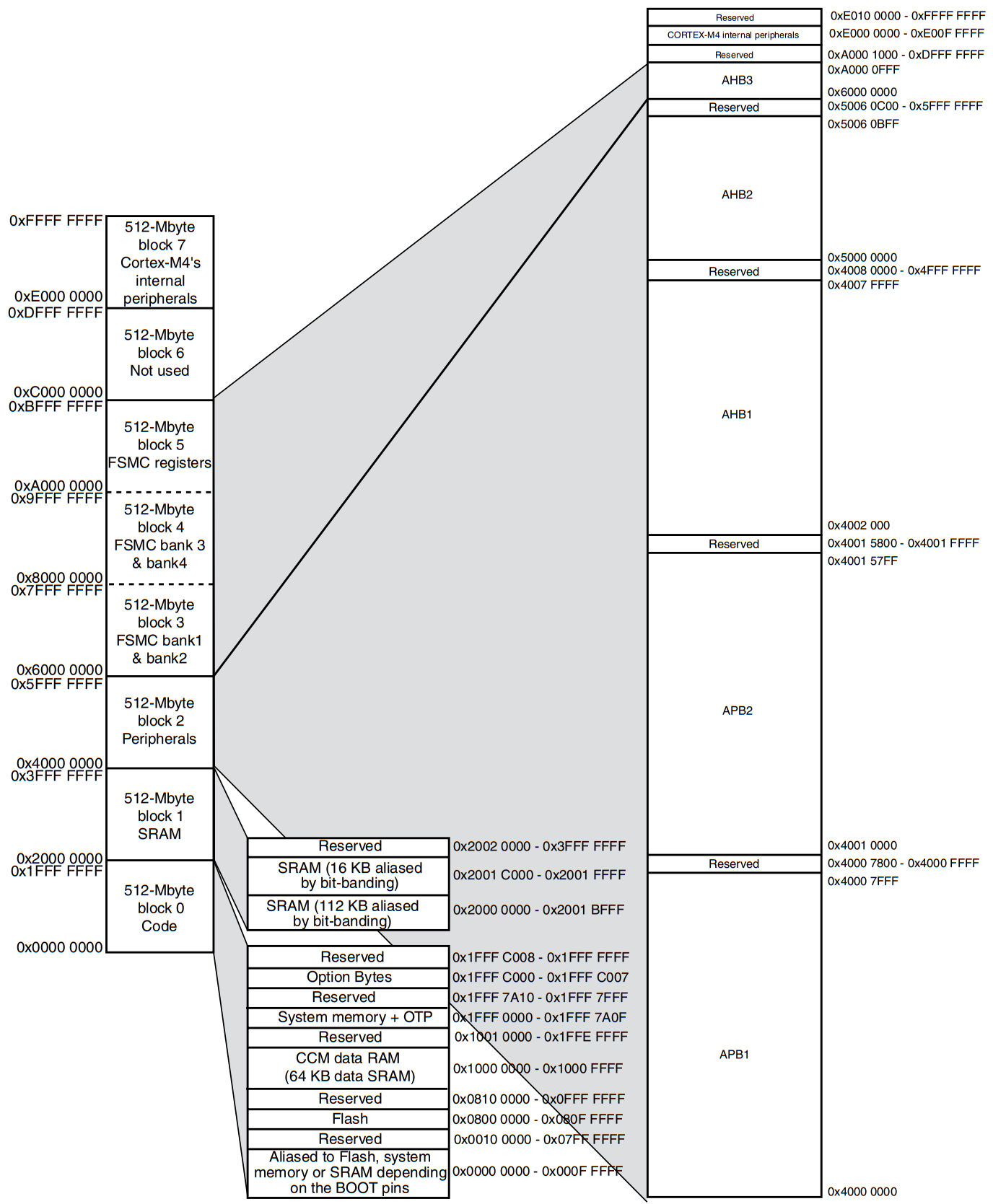

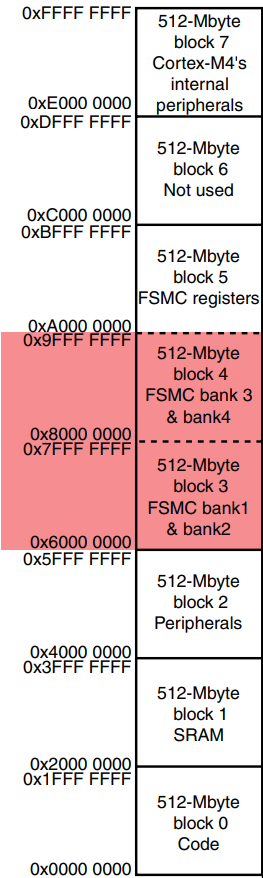

512M * 8Block = 4G

8BLock = 2^3次方,故3bit可以代表一个block

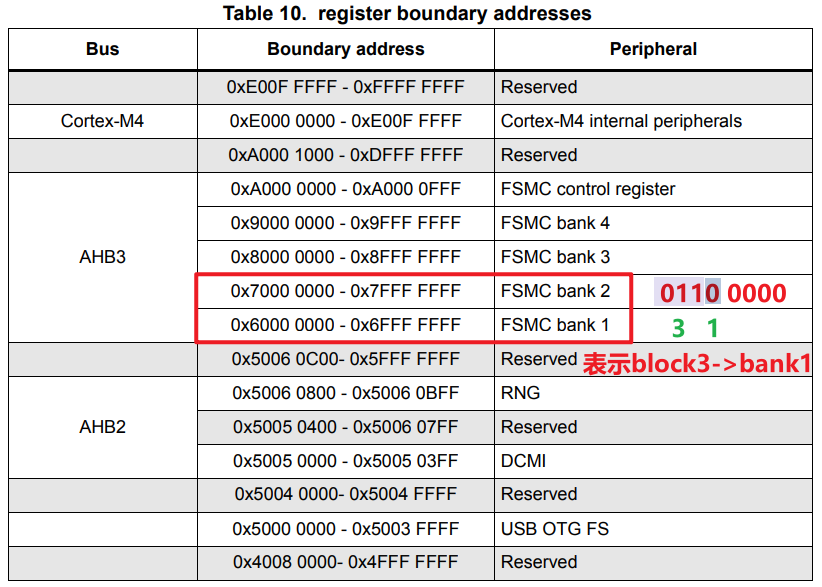

例如:block1 = 00100000,取前三位001 表示 block1,取第四位表示 block1中的bank1(0->bank1,1->bank2)

问:0x68000000 位于哪个块?

Block3 包括 bank1 和 bank2,bank1又分为 FSMC bank1 NOR/PSRAM 1、 FSMC bank1 NOR/PSRAM 2、 FSMC bank1 NOR/PSRAM 3、 FSMC bank1 NOR/PSRAM 4,用于片选外设

1. FSMC的整体结构划分

STM32F407的FSMC(灵活静态存储控制器)根据所连接的存储器类型,划分为4个独立的Bank(存储块),功能如下:

- Bank 1:专门用于连接NOR闪存或PSRAM,内部包含4个Subbank;

- Bank 2 和 Bank 3:用于连接NAND闪存(两者支持不同的数据宽度配置);

- Bank 4:用于连接PC卡设备(兼容ATA协议)。

2. 什么是Subbank?

在FSMC的Bank 1(NOR/PSRAM控制器)中,为了支持同时连接多个并行的NOR闪存或PSRAM设备,内部划分了4个独立的Subbank(子存储体)。

每个Subbank的核心特点:

- 拥有独立的地址空间(每个Subbank占用64MB地址范围);

- 拥有独立的片选信号控制,可单独选中或 deselected 对应的外部设备;

- 可独立配置时序参数(如读写时序、数据宽度等),适应不同规格的NOR/PSRAM设备。

Bank 1中的4个Subbank具体为:

- FSMC Bank1 NOR/PSRAM 1(即Subbank 1);

- FSMC Bank1 NOR/PSRAM 2(即Subbank 2);

- FSMC Bank1 NOR/PSRAM 3(即Subbank 3);

- FSMC Bank1 NOR/PSRAM 4(即Subbank 4)。

3. 片选引脚NE[4:1]与Subbank的对应关系

FSMC通过片选引脚(NE,即NAND Enable的缩写)控制外部设备的选中状态。其中,与Bank 1的4个Subbank对应的片选引脚关系为:

- NE1引脚 → 对应 Subbank 1;

- NE2引脚 → 对应 Subbank 2;

- NE3引脚 → 对应 Subbank 3;

- NE4引脚 → 对应 Subbank 4。

即NE引脚编号与Subbank编号直接一一对应,通过控制NE1~NE4的高低电平(低电平有效),可单独选中对应的Subbank,进而操作该Subbank所连接的外部NOR/PSRAM设备。

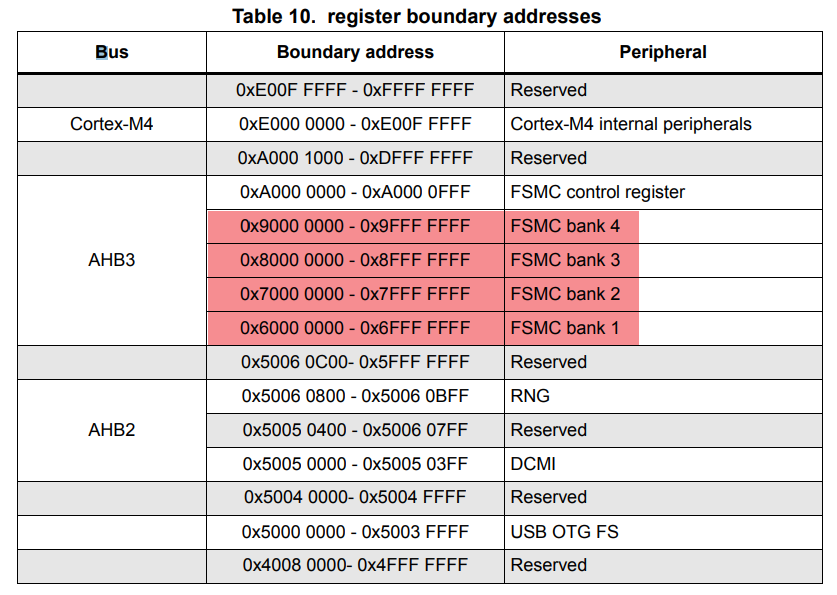

3.1 NOR/PSRAM 地址映射

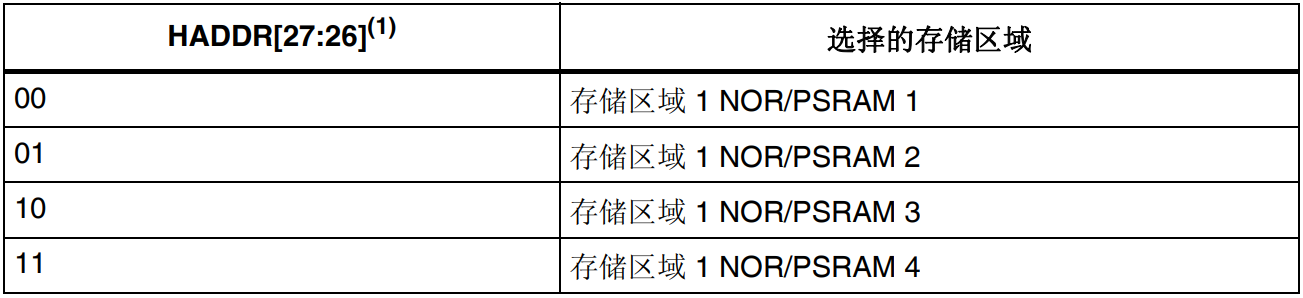

HADDR[27:26] 位用于从下表中所示的四个存储区域之中选择其中一个存储区域。

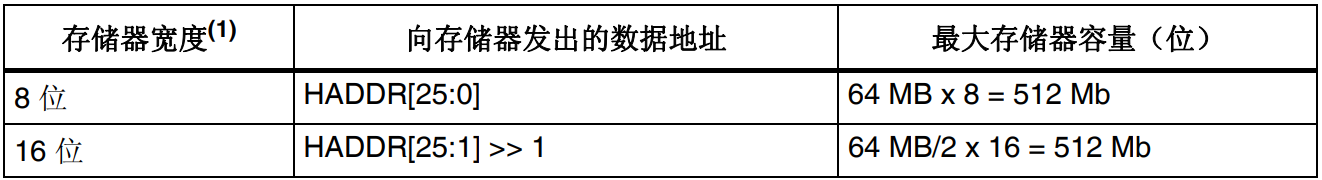

HADDR[25:0] 包含外部存储器地址。由于 HADDR 为字节地址,而存储器按字寻址,所以根据存储器数据宽度不同,实际向存储器发送的地址也将有所不同,如下表所示。

如果外部存储器的宽度为 16 位, FSMC 将使用内部的 HADDR[25:1] 地址来作为对外部存储器的寻址地址FSMC_A[24:00]。

无论外部存储器的宽度为 16 位还是 8 位, FSMC_A[0] 都应连接到外部存储器地址 A[0]。

外部存储器总线宽度(8/16 位)与内部寄存器的 32 位访问

要理解“NOR/PSRAM 控制寄存器必须按32位访问”的规定,需从 STM32 内部总线架构 和 寄存器硬件设计 两个层面分析,同时区分“内部寄存器访问”与“外部存储器总线宽度”的不同逻辑:

一、NOR/PSRAM 控制寄存器为何必须按32位访问?

STM32 的 FSMC 控制寄存器属于芯片内部的外设寄存器,其访问受 ARM Cortex-M 内核的 AHB 总线架构 强制约束:

-

地址对齐要求:

所有 STM32 外设寄存器的地址必须是 4字节对齐(即地址的最低两位为 0,能被 4 整除)。例如,FSMC 的 NOR 控制寄存器FSMC_BCR1地址为0x40011000(末两位为 00),FSMC_BCR2为0x40011004,以此类推。

这种对齐是硬件强制的——若用非对齐地址(如0x40011001)访问,会触发 HardFault 异常 导致系统崩溃。 -

总线位宽与访问效率:

STM32 的 AHB 系统总线是 32位(4字节)宽,寄存器设计为 32位 是为了匹配总线位宽,最大化传输效率。即使某些寄存器实际有效位不足32位(如仅用低16位),硬件仍要求以32位方式访问(通过uint32_t指针操作),编译器会自动处理数据截断(如仅保留低16位)。

二、FSMC 外部存储器总线宽度(8/16位)与内部寄存器的32位访问不冲突

“FSMC 对外部存储器的寻址总线宽度可以是8位或16位”描述的是 外部总线接口,与“内部寄存器的32位访问”属于两个独立的层级,核心差异在于:

-

地址空间与总线层级不同:

- 内部寄存器:位于 STM32 芯片内的

0x40000000~0x5FFFFfff地址段(AHB/APB 外设区),由 AHB 总线直接访问,需遵循 32位 对齐规则。 - 外部存储器:位于芯片外的扩展地址空间(如 NOR Flash 对应

0x60000000~0x63FFFFFF,PSRAM 对应0x68000000~0x6BFFFFFF),由 FSMC 硬件将内部 AHB 事务转换为外部总线信号(如 8位/16位 数据总线、地址线)。

- 内部寄存器:位于 STM32 芯片内的

-

位宽转换由 FSMC 硬件自动处理:

FSMC 作为“桥梁”,会将内部 32位 AHB 事务转换为外部 8位/16位 存储器的访问:- 若外部是 16位 存储器(如多数 NOR Flash):FSMC 会将内部 32位 写操作拆分为两个 16位 写事务;读操作则自动合并 16位 数据为 32位(无用位丢弃)。

- 若外部是 8位 存储器(如某些 SRAM):FSMC 会将内部 32位 操作拆分为四个 8位 事务,通过

NBL[1:0](字节选择信号)控制具体字节。

三、总结:“内部32位寄存器”与“外部8/16位总线”的协同逻辑

- 内部寄存器32位访问:是 ARM Cortex-M 总线架构的强制要求(地址4字节对齐 + 32位数据总线),保证硬件稳定性与传输效率。

- 外部总线8/16位宽度:是 FSMC 对不同外部设备的兼容性设计,由 FSMC 硬件自动处理位宽转换,无需软件干预。

两者看似“矛盾”,实则是 “内部总线标准化”与“外部设备兼容化” 的分层设计,既满足了芯片内部的高效性,又适配了外部设备的多样性。