数电基础:常见的CMOS门电路

目录

一、与非门

(1)NMOS作为逻辑元实现

(2)为什么不用PMOS作为逻辑元?

二、或非门

(1)用NMOS作为逻辑元实现

(2)为什么不用PMOS作为逻辑元?

三、设计原则的总结:NMOS主导、PMOS互补

四、漏极开路输出门电路(OD门)

(1)普通的CMOS元件输出直连的问题

(2)上拉电阻R对电源的保护启示

(3)真正工程上的OD门

1.线与功能

2.电平转换功能

五、三相输出门

(1)为什么需要高阻态输出

(2)设计思路与结构分析

(3)为什么使能端要采取低电平有效?

(4)为什么信号端也要加非门?

在上篇文章中,我们理解了CMOS反相器作为最非门的原理,我们知道由于在数字电路中的电平是限制在GND~VCC范围内的,所以想要给NMOS输入高电平则需要让NMOS本身接地才能体现电压差;想要给PMOS输入低电平则需要让PMOS接VCC才能体现栅极负压。于是我们在数字电路中有个原则是:NMOS一般需要接地使用、而PMOS则一般需要接电源正极使用。

而这也刚好体现了MOS管的反相输出作用:输入输出电平必定会一高一低。所以以后只要是由MOS管构成的电路都会自带非逻辑,如果想要再次逆转,则需要在后面串联一个CMOS反相器。

一、与非门

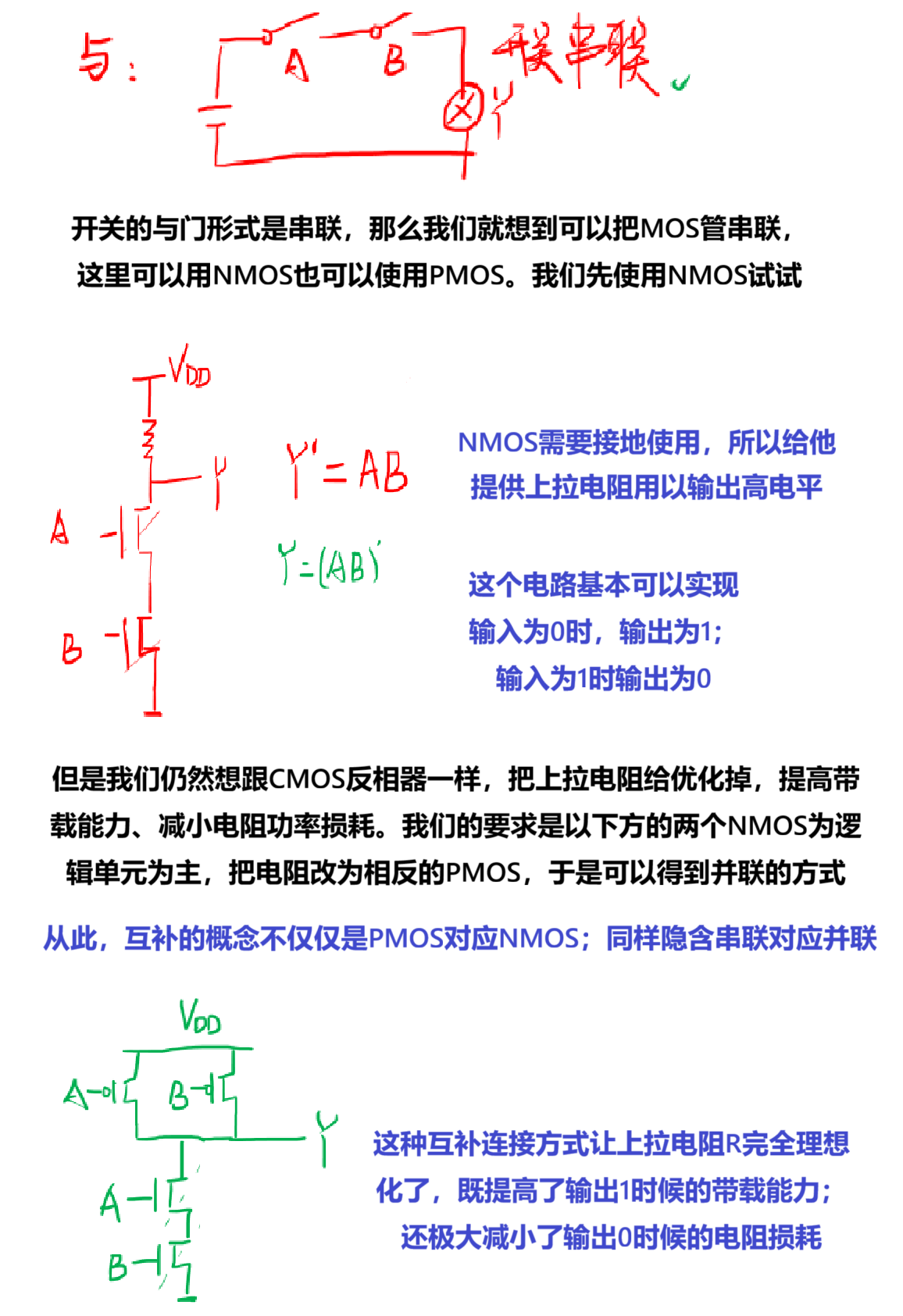

(1)NMOS作为逻辑元实现

既然知道了MOS管自带非逻辑,那么与非门我们其实只用实现与门即可。

(2)为什么不用PMOS作为逻辑元?

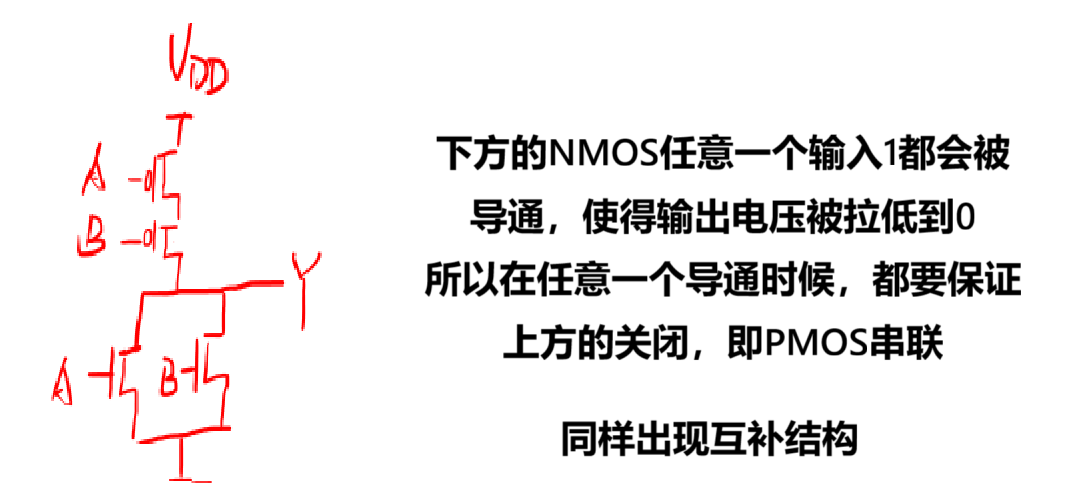

在看到书上用NMOS作为与、或、非逻辑的时候,我曾产生了一个疑问:为什么不能用PMOS呢?

即比如与非门,把上面的PMOS并联改为PMOS串联;下方的NMOS串联改为NMOS并联。从结构上看仍然可以实现与非逻辑。其中与逻辑用PMOS实现,非逻辑由CMOS反相器天然实现。

但是我们要考虑响应速度的问题。

在我这种设计中:

输出电平从1->0,由NMOS管接地实现;输出电平从0->1,由PMOS接高电平实现。但是接地时候是并联,接VCC时候是串联,要通过两个PMOS管,意味着上拉过程会慢于下拉过程。同时由于PMOS空穴载流子的特性,传导比NMOS慢,这种设计相当于把PMOS慢的特性给叠加放大了。

而原本的设计:

输出电平从0->1时,仅通过并联的PMOS上拉,整个过程只有一次传导;输出电平从1->0的时候,则需要通过两个串联的NMOS管,看似下拉时间要比上拉的路径长。但由于NMOS的载流子是电子,传导速度远高于空穴,即使下拉要通过两个NMOS管,时间也会比上拉快。

无论哪种设计方式,都是上拉时间要慢于下拉时间。不过PMOS串联这种方式上拉时间会更慢。

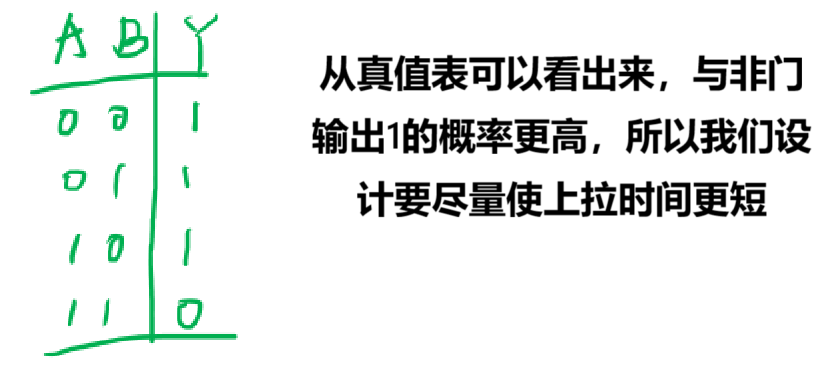

最后在数字电路的与非逻辑中,1的活跃度通常是高于0的。

即从0->1的跳变会多于从1->0的跳变。在原理图中表现为更多是需要PMOS导通,NMOS截止的上拉能力。综合来看,原先的涉及上拉路程只有我的设计的一半,所以上拉速度更快,整体效率更高。

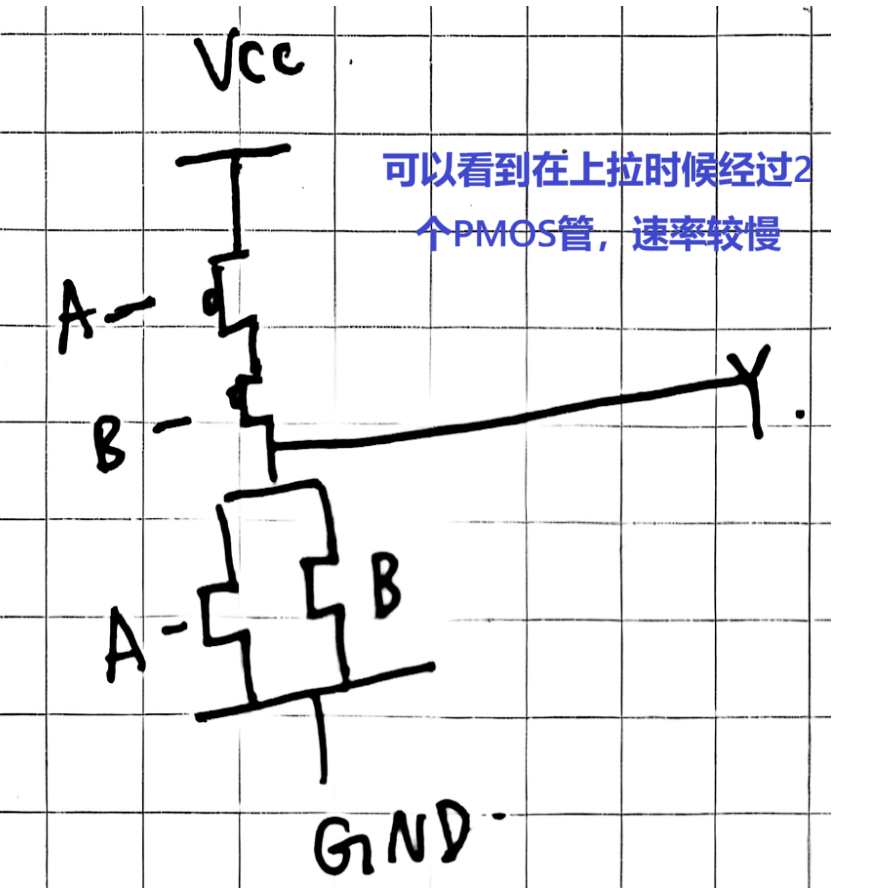

二、或非门

(1)用NMOS作为逻辑元实现

和与非门类似,我们先用NMOS实现或逻辑,即并联。

(2)为什么不用PMOS作为逻辑元?

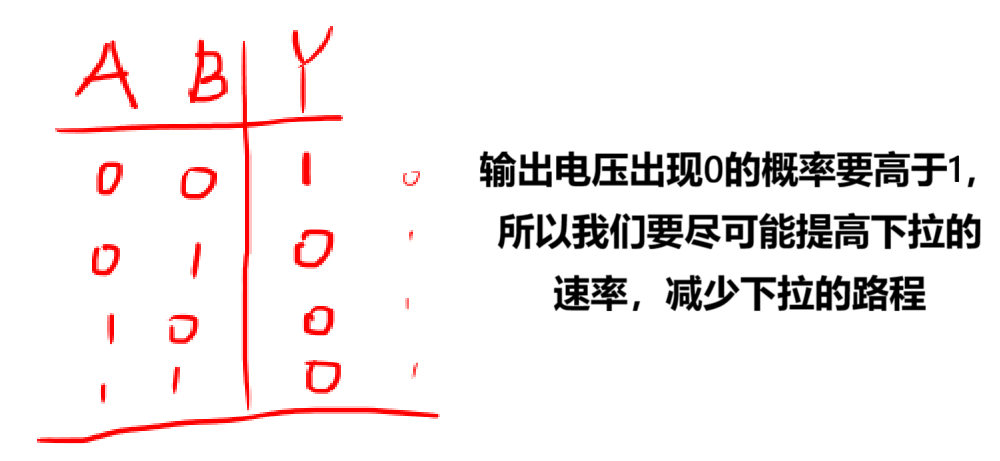

与之前的原因完全一致,从真值表中可以发现输出0的概率高,即从1->0这种下拉次数比

从0->1的上拉次数多。所以要减少NMOS下拉的路程,即并联NMOS。

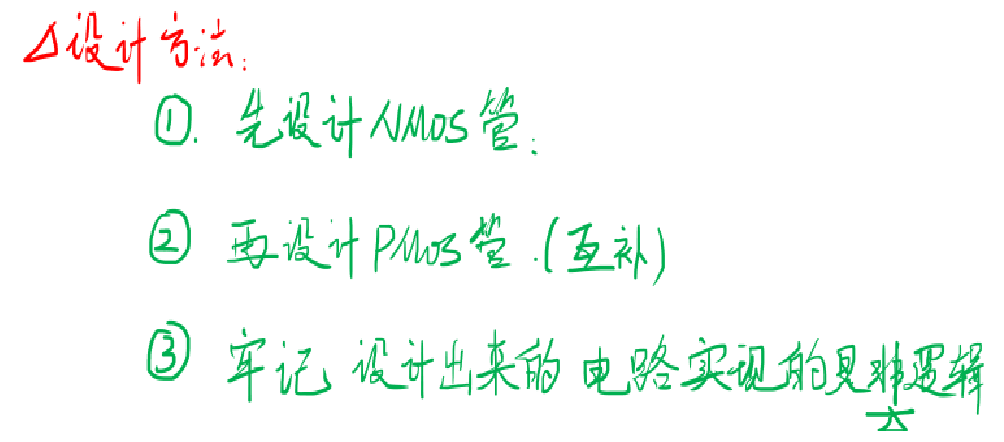

三、设计原则的总结:NMOS主导、PMOS互补

通过上面的讨论,我们明白了与非门中,需要提高上拉速度而减少PMOS的级联,所以多采用PMOS并联;而在或非门中,更需要提高下拉速度而减少NMOS的级联,多采取NMOS并联的方式。

这两种情况从NMOS的视角看过去,会发现:NMOS的串并联逻辑直接就是与、或逻辑。所以以后在设计逻辑电路的时候,可以直接从NMOS的视角出发,然后根据互补原则把PMOS补上去。这可以作为一个规则使用,可以极大程度减少我们思考的过程,提高设计效率。

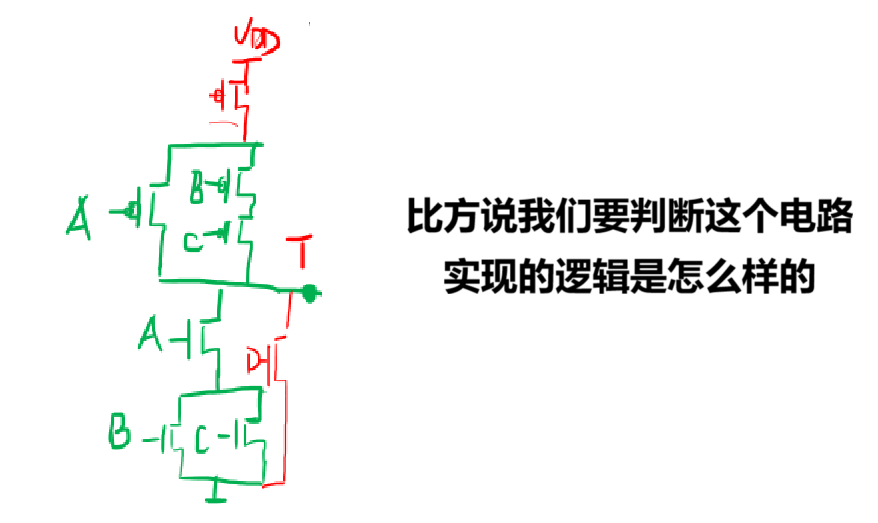

我们从NMOS的视角看过去,[A串联(B和C并联)]并联D,就能直接分析出逻辑是:[A&(B|C)]|D

简单而高效,不用再去分析各种情况画真值表了。

四、漏极开路输出门电路(OD门)

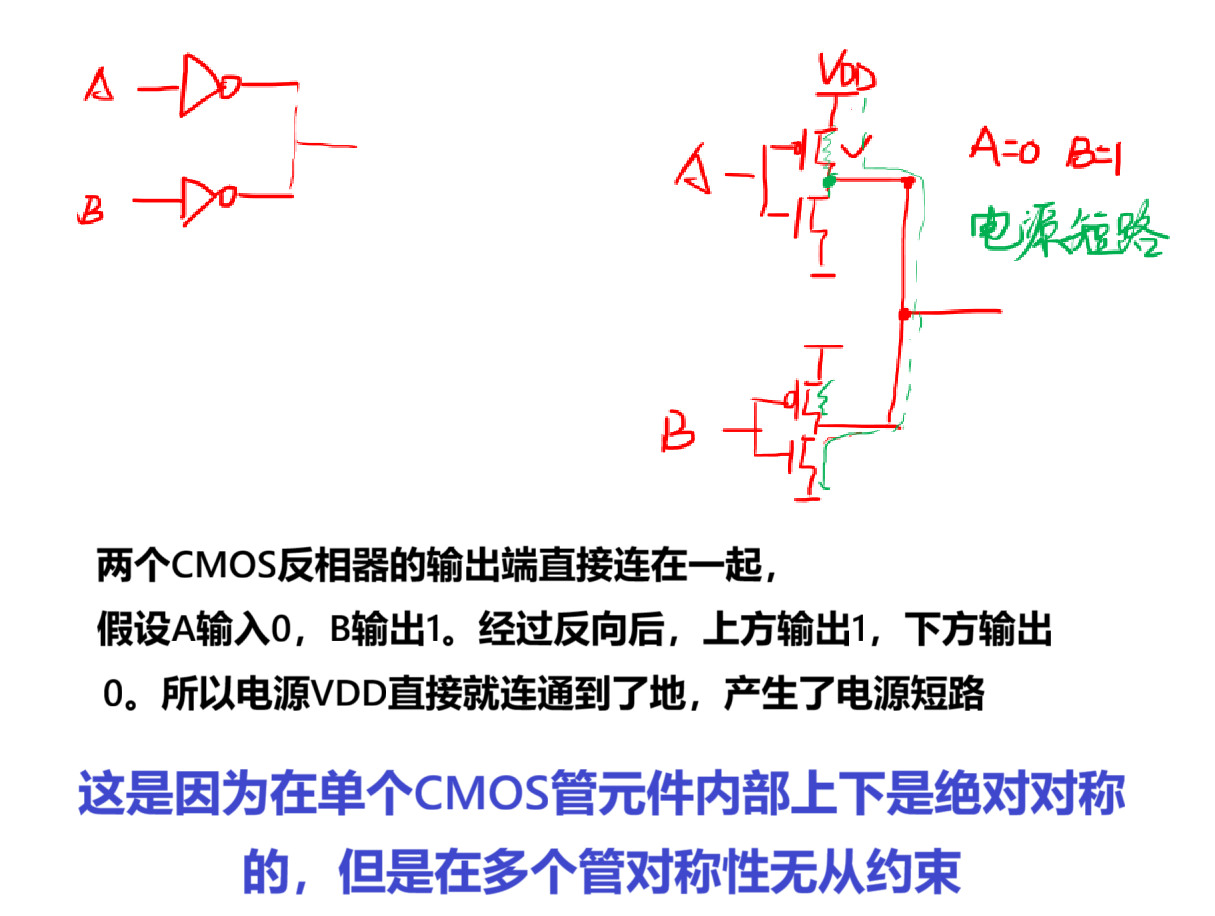

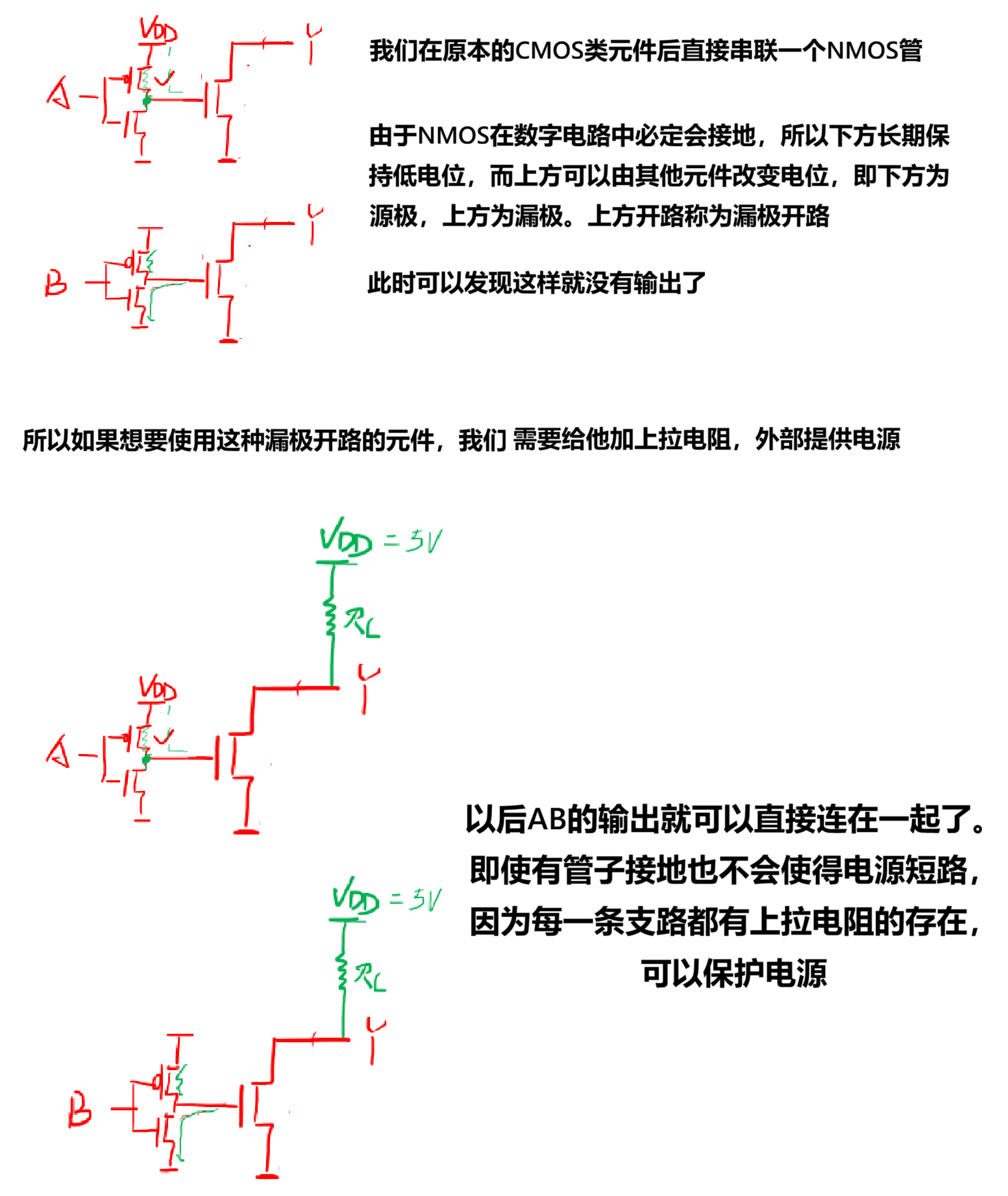

(1)普通的CMOS元件输出直连的问题

普通的与非门、或非门以及非门已经了解的差不多了,我们知道他们都是由NMOS、PMOS两种元件互补组成的,但是他们面临一个问题:不能把多个门电路的输出端连到一起。

(2)上拉电阻R对电源的保护启示

最后,由于反相器的作用,原本的与非门就退化成了单纯的与门。

最后,由于反相器的作用,原本的与非门就退化成了单纯的与门。

(3)真正工程上的OD门

我们上面的电路基本实现了隔离,能避免电源短路的问题。但是由于会额外增加一个NMOS管。而在集成电路工艺中,每个地方节省一点所带来的成本节约是非常可观的,更关键的是省去了这个NMOS的空间,让芯片的集成度大幅提高。

所以OD门是在我们的设计思路上直接把普通的CMOS逻辑元件的PMOS和上拉电源部分给删去了,对外直接就体现原本思路中的串联NMOS结构。而且这样输出逻辑和原本的与非门、或非门是一致的。

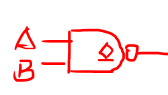

我们对这样直接在普通CMOS逻辑单元上直接删除PMOS部分的电路称为OD门电路。可以用下面的图形表示(在原本图形上加上菱形符号即可)

1.线与功能

由于上拉电阻的存在,避免了电源短路的问题。所以各种OD门的输出可以直接相连,并且产生的是与功能。这是因为在Y1、Y2处只要有任意一个输出0,就意味着内部的NMOS导通了,强烈的下拉会把输出限制在0V;而全部输出1时候NMOS截止,输出的Y就是上拉电阻提供的。

不过这里的与功能仅仅是指这个节点,而对原先电路的逻辑功能完全无影响。

2.电平转换功能

由于这里把PMOS部分删除后,用户自己加上拉电阻和电源。所以对于输出端具体输出多高的电位也是可以自定义的。比如在原先的逻辑电路中是3.3V的高电平,使得OD门这里导通,然后源漏之间的输出电压和以前并无关系,他是直接由VDD决定的。

最后提一句:在NMOS这里看似有上拉电阻和接地两种状态同时施加,无法判断源极本身是什么电位,进而无法与左边的输出电压产生关系而实现开关作用。但实际上由于接地的影响力是远大于上拉电阻的(上拉电阻的阻值很大,电流小),所以体现为低电平,进而可以由左边的栅极电压形成电压差。

五、三相输出门

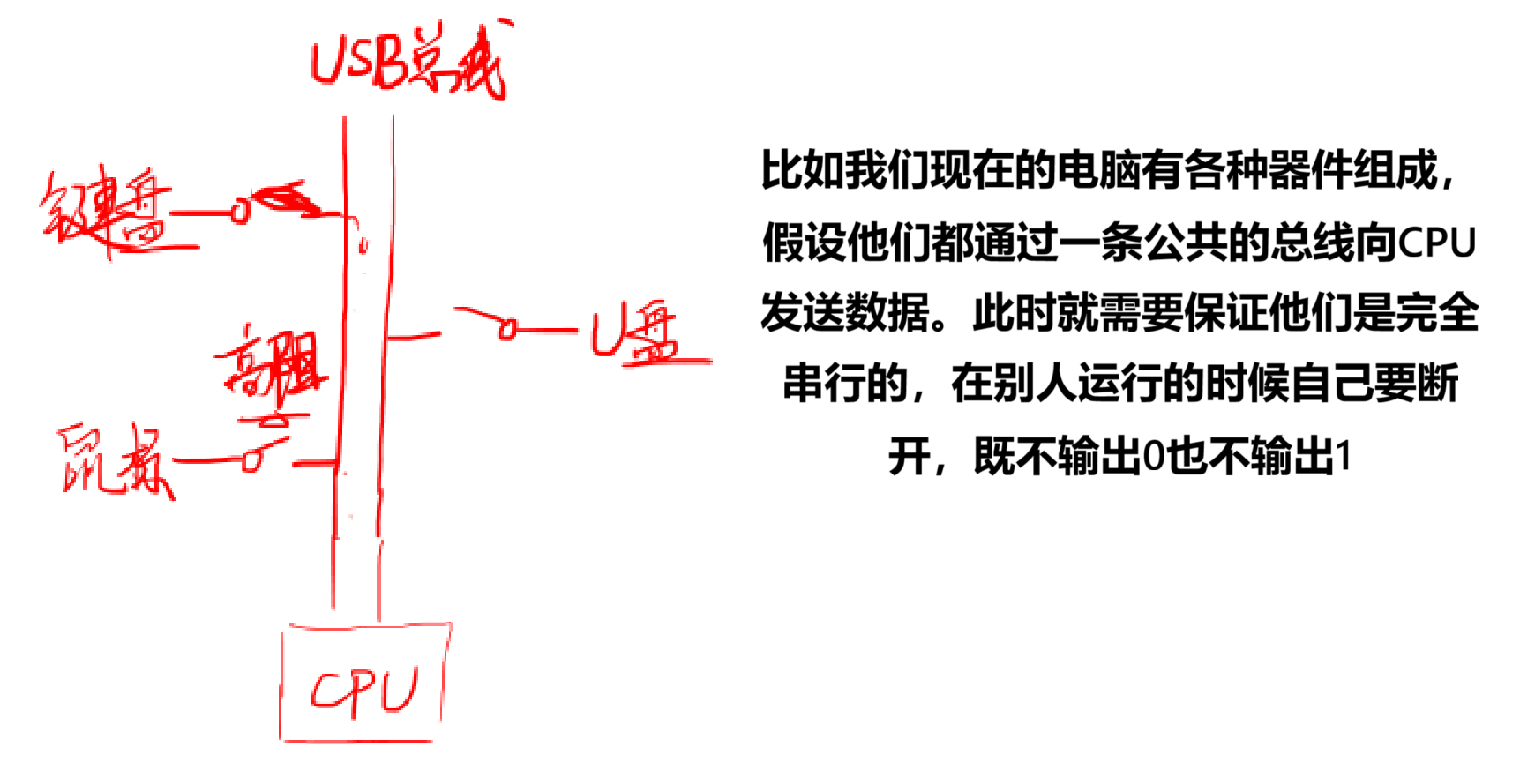

(1)为什么需要高阻态输出

在数字电路的世界里,不是非1即0的,还会有一种高阻态。我们对即可以输出0、1信号还能选择性输出高阻态开路的电路结构称为三相输出门电路。他常常用于各种元件的使能端,当使能后才能正常输出0、1信号,而在没有使能开始前,整个元件是不工作的。

所以我们就通过三相输出门来控制,当该门处于高阻态时候,器件没有被使能,完全关闭,不会输出0或1,对其他挂载到同一总线的元器件不会有影响。而当该门被使能后,器件开始工作,可以输出0和1信号给CPU。

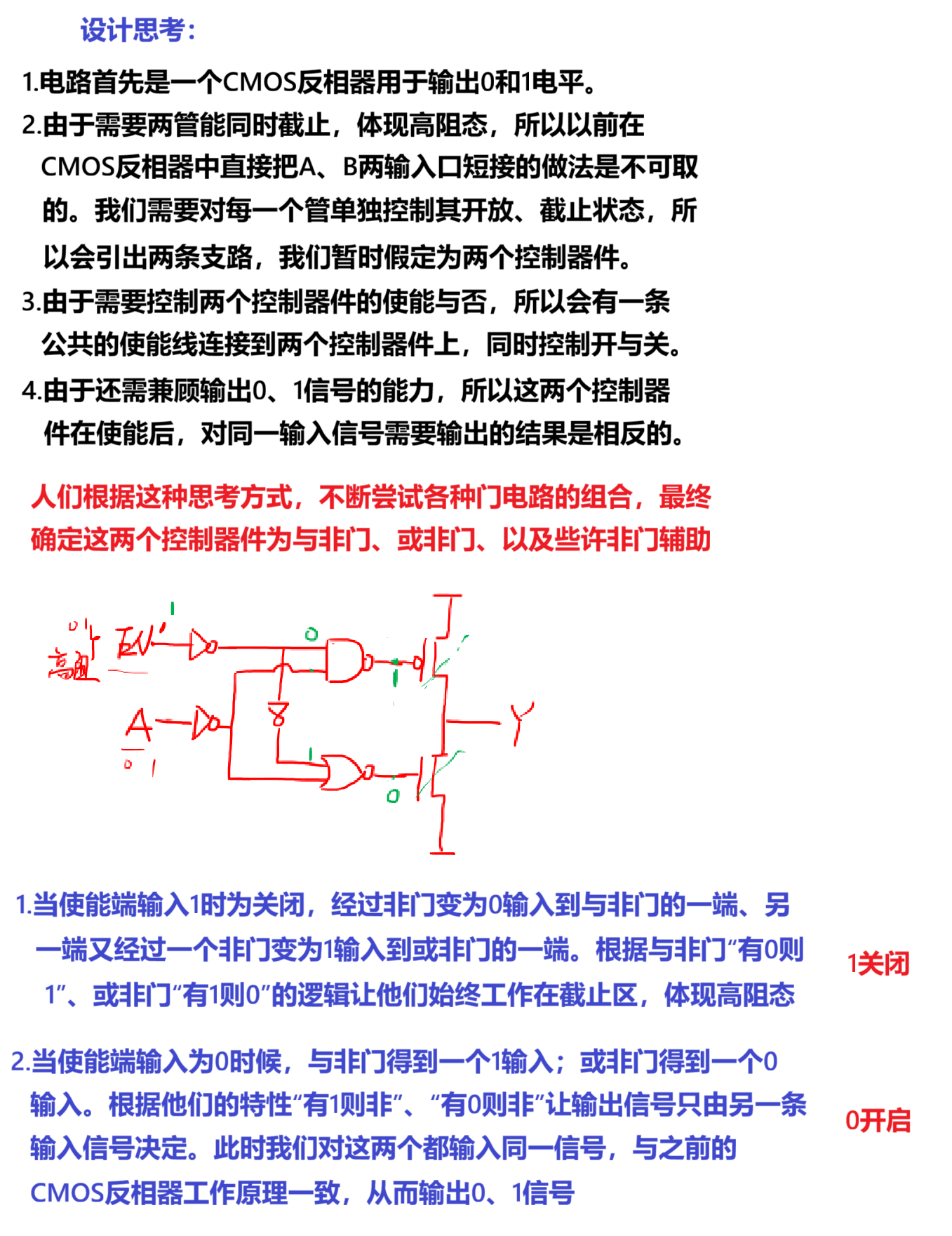

(2)设计思路与结构分析

其中这个EN使能端打了一撇,就表示低电平有效(开启)。如果只写了EN,没有撇,则表示高电平有效。

(3)为什么使能端要采取低电平有效?

在看到这个电路的时候,我就产生了质疑?为什么要多加一个非门,你前面说了集成电路减少一个门电路都是较大的提高,到这里却随意增加了非门?

但后来查阅资料后发现,低电平使能主要是下拉能力强,稳定性好,使能不容易受干扰而使能中断。

若去掉使能端的非门,使能信号变为高电平有效(EN),虽然逻辑上也能工作,但低电平有效有以下关键优势:

- 抗干扰与稳定性:CMOS 电路中,“低电平(0V)” 的噪声容限更大(即对干扰更不敏感),且使能端若意外悬空,通常会被上拉为高电平 —— 低电平有效设计下,悬空时使能无效(输出高阻),可避免误触发;若为高电平有效,悬空会导致误使能,引发总线冲突。

- 功耗优化:CMOS 器件在低电平时功耗极低(静态电流几乎为 0),低电平有效设计可降低系统待机功耗。

(4)为什么信号端也要加非门?

若去掉信号路径的非门,三态门的逻辑会从反相” 变为同相缓冲”,这违背了 **“三态门是 CMOS 反相器的功能扩展”** 的设计初衷:

- 普通 CMOS 反相器的核心逻辑是 “输入输出反相”;

- 三态门作为反相器的衍生电路,需在保留 “反相逻辑” 的基础上,新增 “高阻态” 功能。若去掉非门,逻辑功能会从 “反相三态门” 变为 “同相缓冲三态门”,虽然功能可行,但不符合该电路作为 **“反相器扩展”** 的设计定位,也会破坏数字系统中逻辑门的一致性(比如与非门、或非门的逻辑延续性)。

其实简单来说就是本来其他大量电路已经通过反相器等门电路实现好了,只是需要新增高阻态输出功能,则不能违背以前的逻辑。如果你不加非门则会导致原本的逻辑混乱,这里仅仅是为了保证与原架构适配。