Marin说PCB之SI----做信号完整性仿真时需要注意的地方--01

一,首先无论是我们用哪种软件做信号完整性能仿真的时候一般都是会使用相应的EDA软件生成ODB++文件进行仿真,我们来看下在导入到仿真软件中经常遇到的几个问题点。

1,EDA软件生成ODB++文件没有进行去除非功能焊盘,导入到我们的仿真软件中就直接进行信号完整性能仿真了,我们分别从信号的插损,回损,以及信号的TDR曲线这个三个信号性能的曲线图去看下实际的仿真结果的区别

下面这两个图片就可以很清晰地区别出我们导入进来的文件是否已经删除了过孔的非功能焊盘了

保留信号过孔的非功能焊盘:

删除了信号过孔的非功能焊盘:

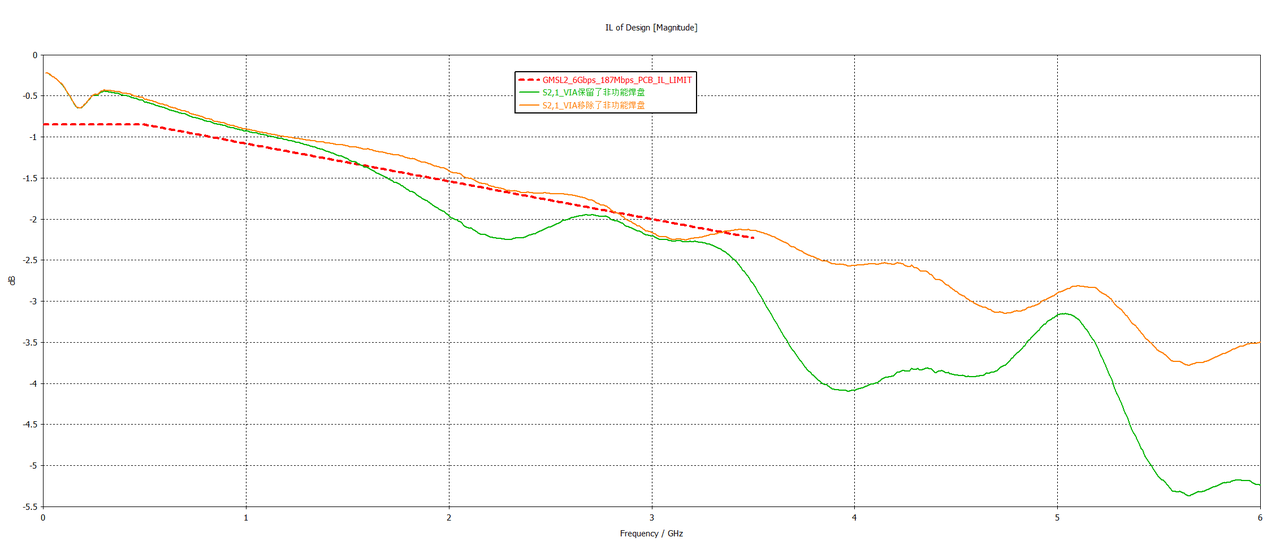

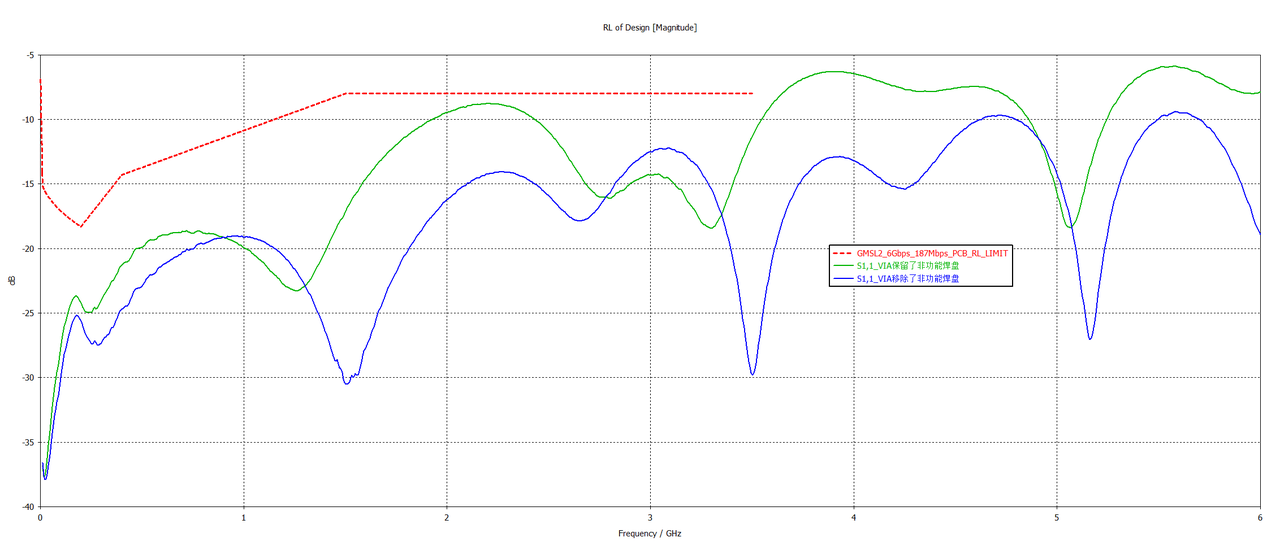

2,插损和回损的仿真结果,找一路GMSL信号进行仿真,例如:RX0_96712_FAKRA_1。

IL:

RL:

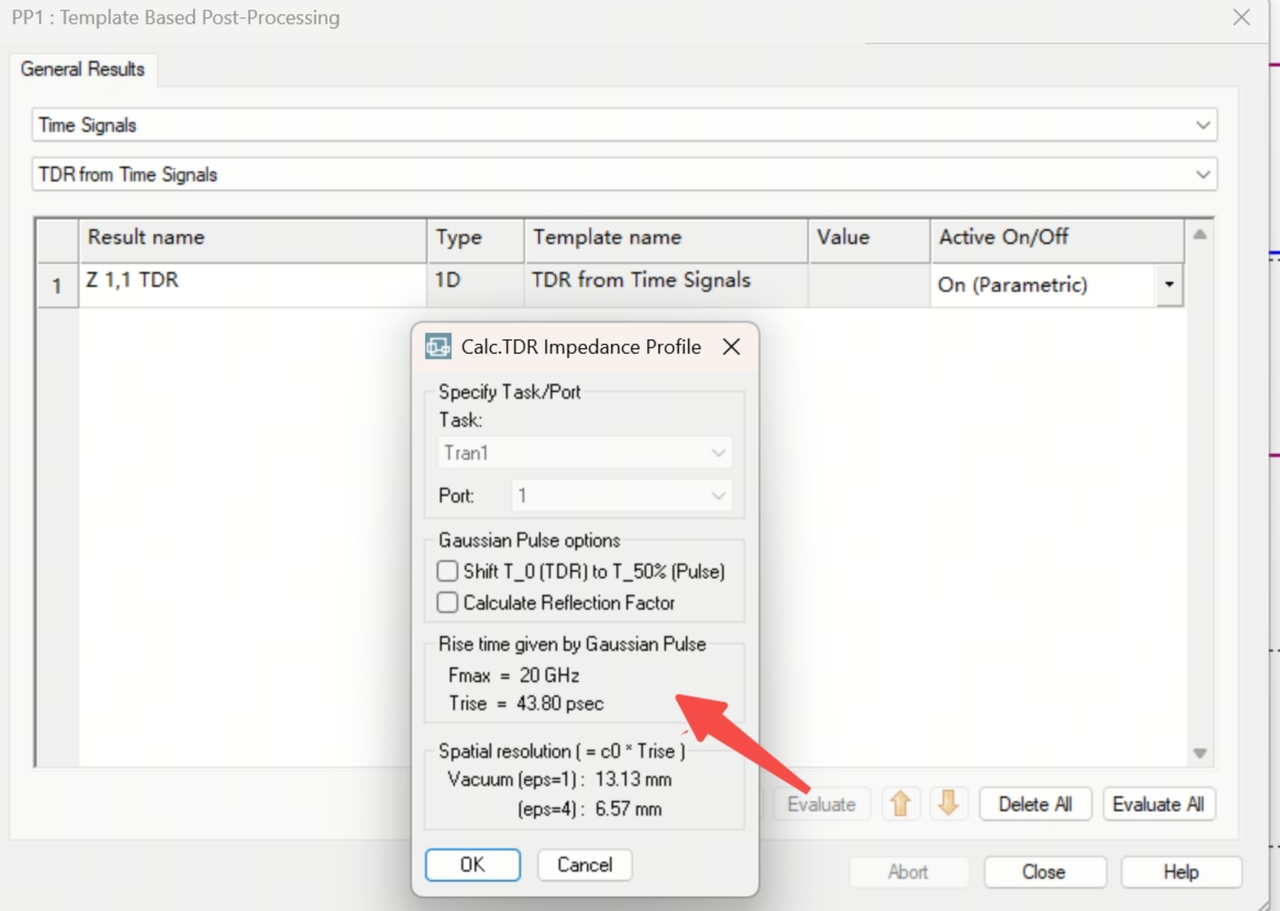

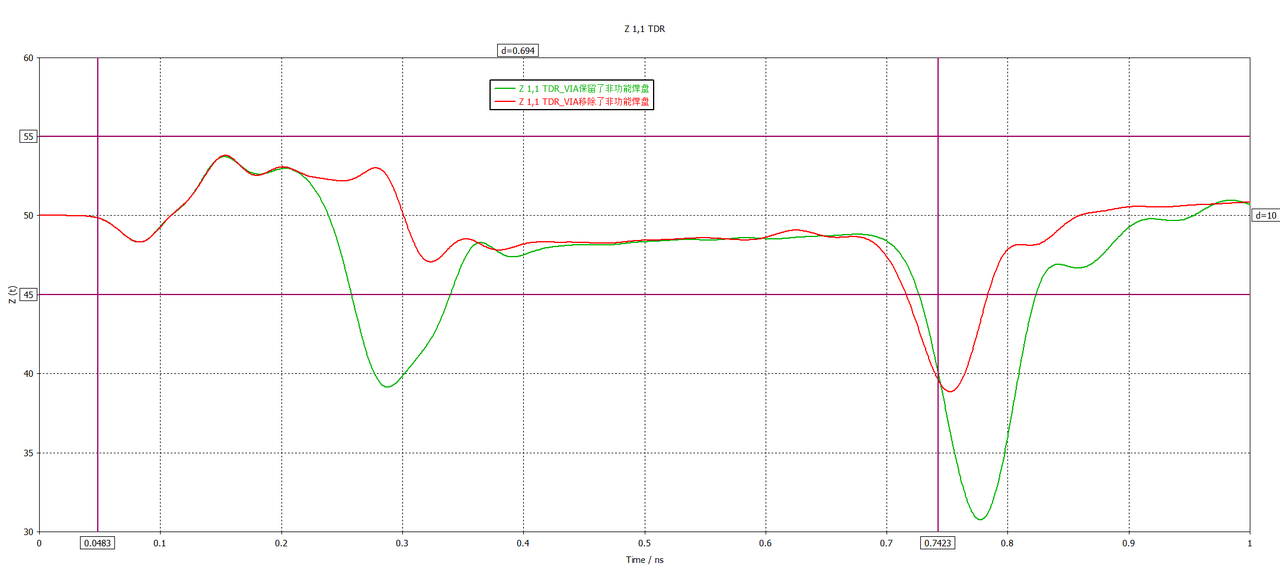

3,TDR仿真的结果比对:

按照激励源的上升时间是48.3PS,这个是软件自带的一个计算公式去算的:

根据公式L=TD/2*V, V的信号在介质中的传播速度,按照6MIL/PS计算。L=2081MIL,带入数据可以得出TD的数值为694PS=0.694NS,按照这两个数据加起来就可以得出末端的时间点为0.0483+0.694=0.7423NS

小编我之前也有我单独的文章讲解过这个知识点:

Marin说PCB之过孔去掉非功能焊盘的优点设计总结 https://blog.csdn.net/weixin_45223454/article/details/131467526?spm=1001.2014.3001.5502

https://blog.csdn.net/weixin_45223454/article/details/131467526?spm=1001.2014.3001.5502

二, 移除非功能焊盘的主要好处?

-

减少阻抗不连续性和信号反射

-

核心好处:非功能焊盘在传输路径上引入了一个多余的电容。这个额外的电容会使局部阻抗降低,形成阻抗凹陷。

-

对于高速信号(特别是>1 Gbps),任何阻抗突变都会引起信号反射,劣化眼图,增加码间干扰。移除焊盘可以使阻抗曲线更平滑,改善信号完整性。

-

-

改善插入损耗

-

由非功能焊盘引入的寄生电容会随频率升高而加剧信号衰减。

-

移除它们可以减少介电损耗和导体损耗,从而在高频段(例如10 GHz以上)获得更好的插入损耗性能。

-

-

减少串扰

-

非功能焊盘增加了相邻过孔或走线之间的平行耦合面积。

-

移除焊盘后,过孔与邻近导体之间的间距增大,从而减小了寄生电容和互感,有助于降低串扰。

-

三,移除非功能焊盘的主要风险与挑战?

-

DFM(可制造性)风险 - 最关键的考量

-

对准公差要求极高:移除非功能焊盘后,过孔与内层铜箔之间的间隙完全依赖于钻孔与内层反焊盘之间的对准精度。

-

层压偏移:PCB在压合和钻孔过程中,各层之间不可避免地存在微小的位置偏移。如果偏移过大,可能导致过孔管身意外接触到本应隔离的平面,造成短路。

-

这要求PCB板厂具有非常先进的设备和严格的工艺控制能力。

-

-

散热加剧,焊接难度增加

-

焊盘具有“热质量”,在焊接时能帮助散热,使焊锡更容易凝固成型。

-

移除非功能焊盘后,特别是对于需要塞孔的Via,过孔的热容量降低,可能导致:

-

焊接时焊锡流失:在回流焊过程中,焊锡可能通过过孔被吸到板子另一面,造成焊点锡少、虚焊。

-

焊接外观不良:尤其是对于波峰焊,可能导致焊点不饱满。

-

-

-

机械强度可能略微下降

-

焊盘对过孔在板内提供了一定的锚定作用。移除后,过孔与介质材料的结合力完全依赖于孔壁与基材的附着力,在极端机械应力下(如弯折)的可靠性可能略有下降(但对于FR-4板材,影响通常很小)。

-

正常我们在发板子给制板厂的时候会有制板要求设计文档上也会要求做这个设置的,或者是正常板厂EQ的时候也会确认下这个问题的。

好了,诸位道友们以上就是本期的所有内容了,我们下期文章不见不散。

--------声明:本文属于小编的原创文章,如需转载请注明来源!