【FPGA】设计流程——Veriolg输入

一、使用的软件

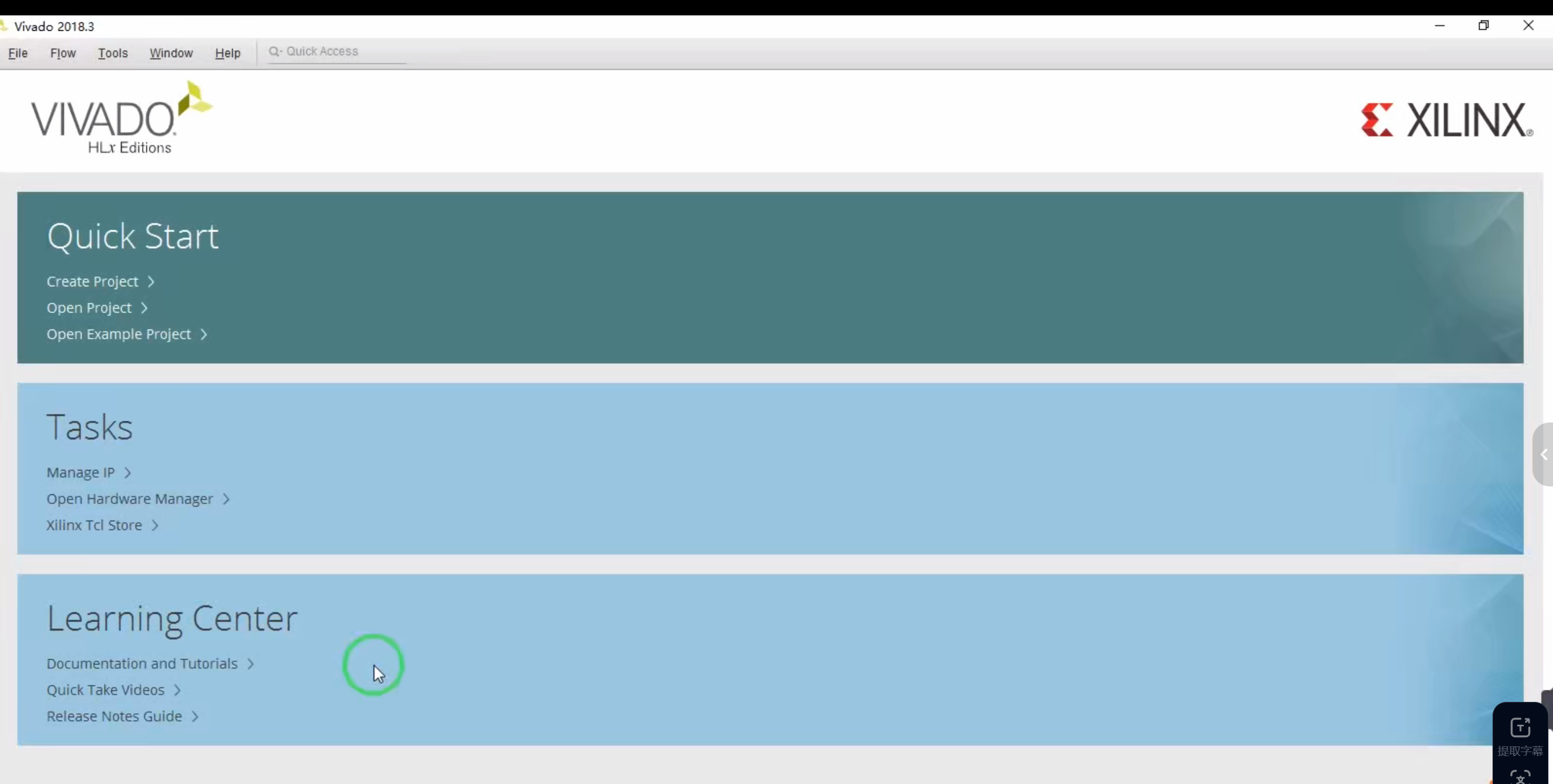

第一栏快速开始

第二栏基本任务

第三栏会提供一些官方的学习资料

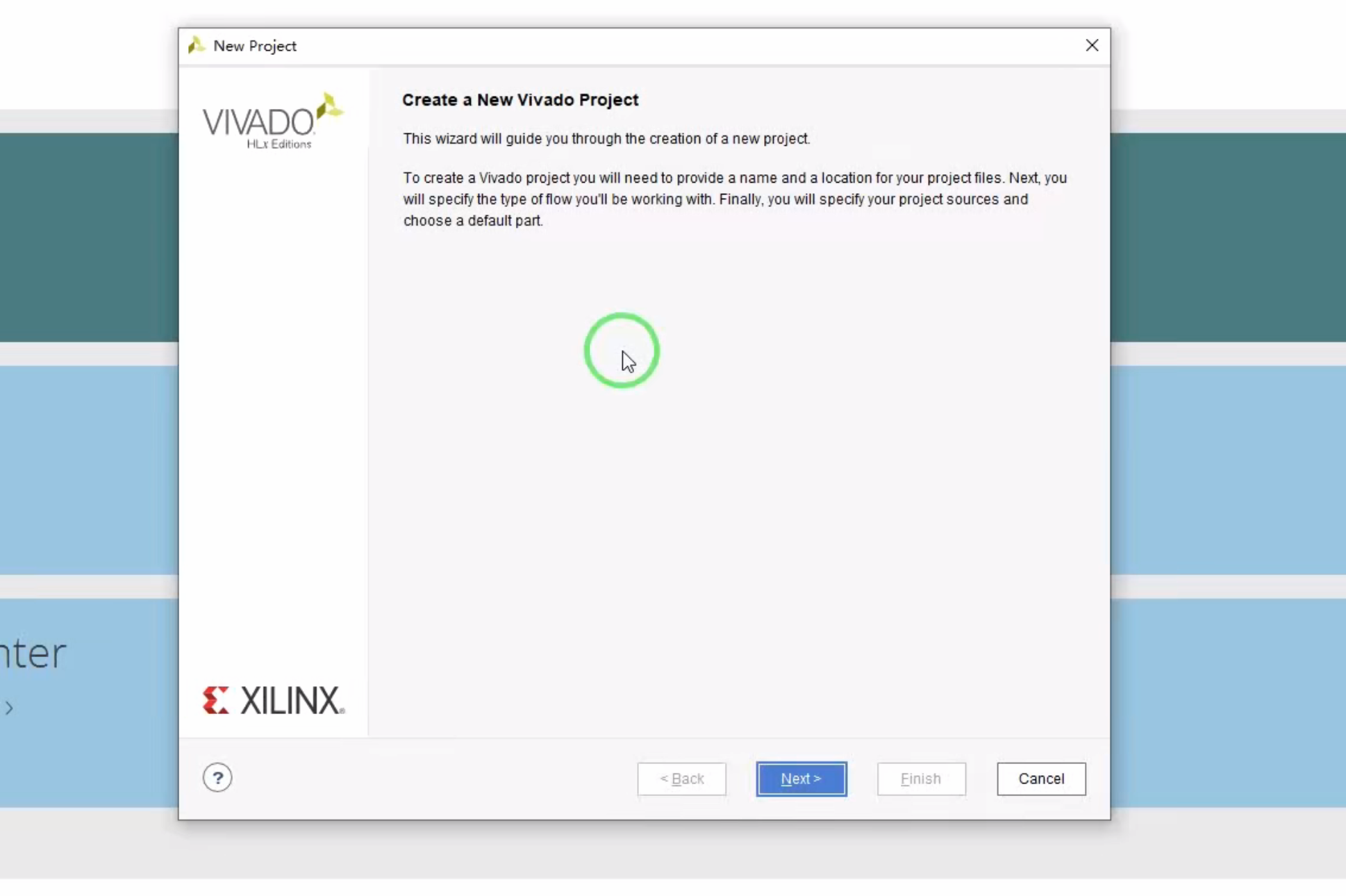

二、创建新工程

点击create project

点击next

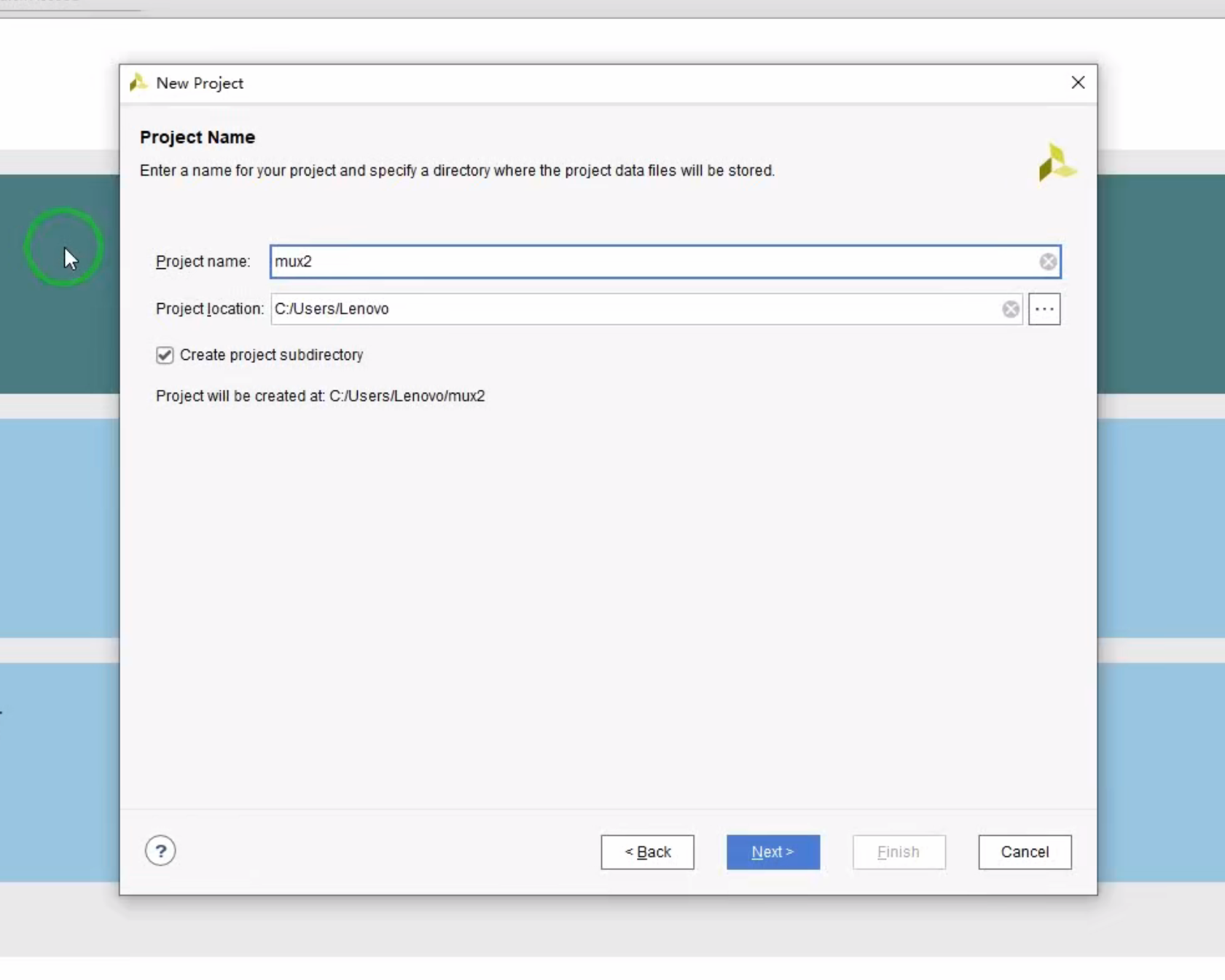

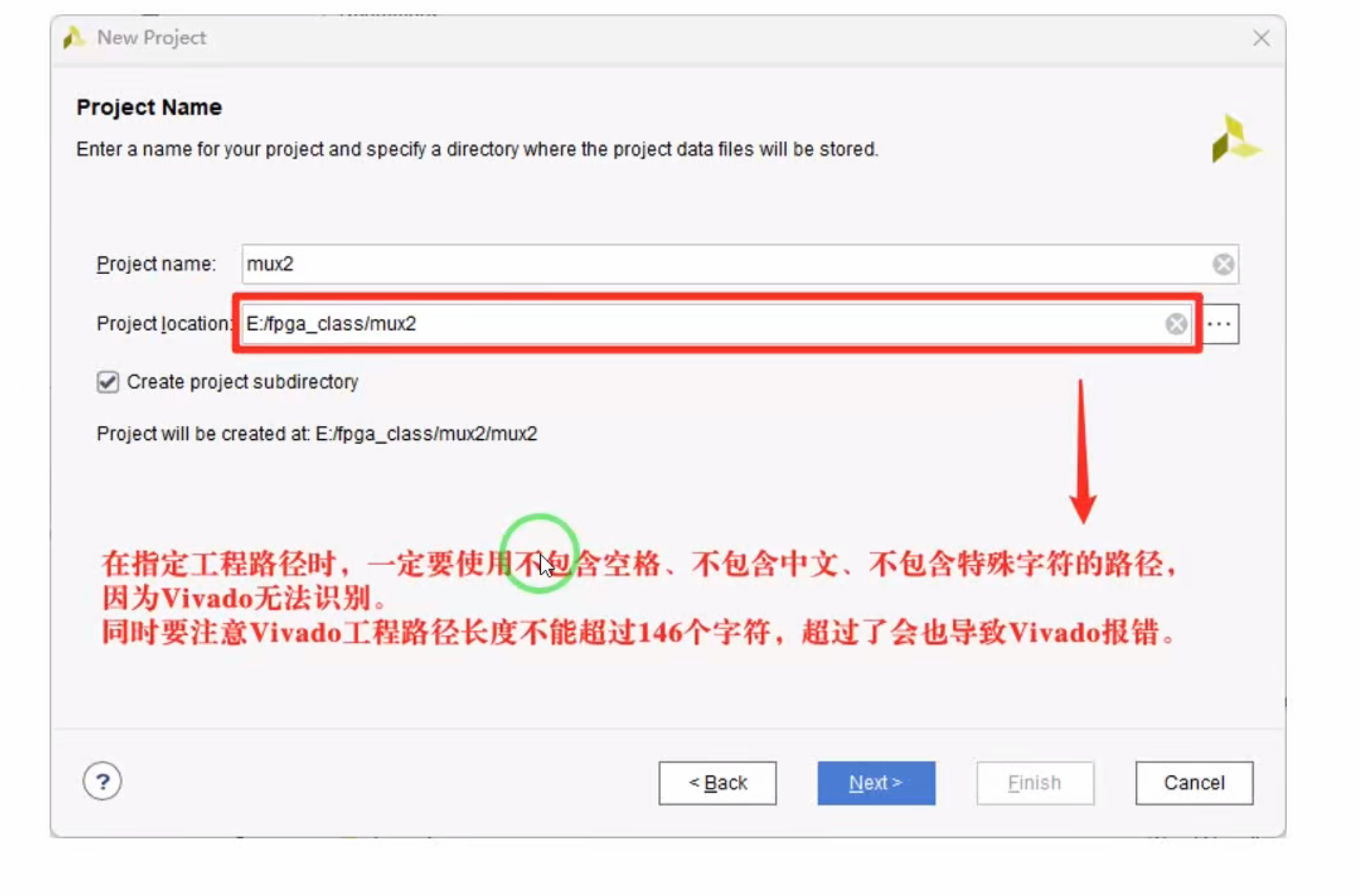

给新工程起名,推荐其具有实际意义

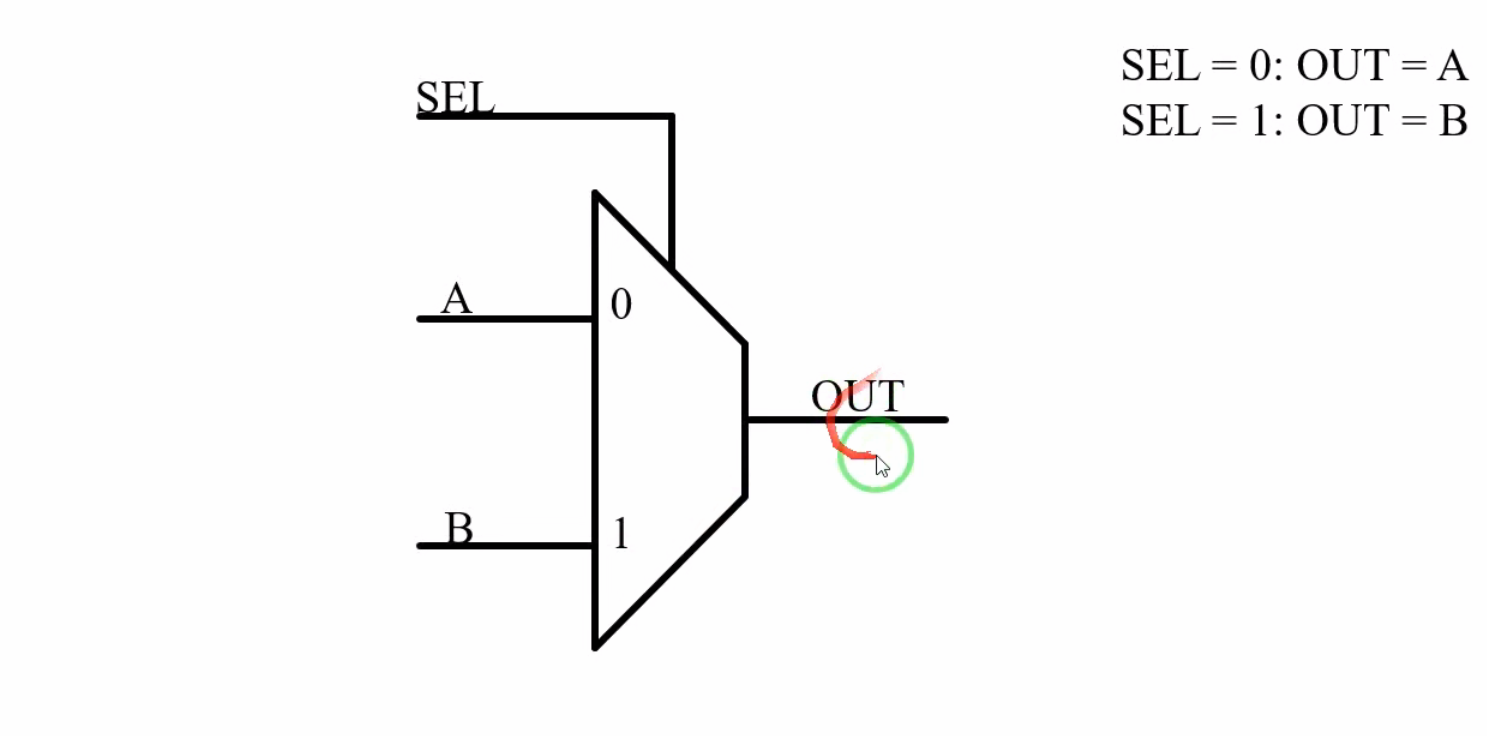

二选一多路器

下面的是路径,勾选下面的选项就会在文件夹下新建一个project name一样的文件夹

注意:

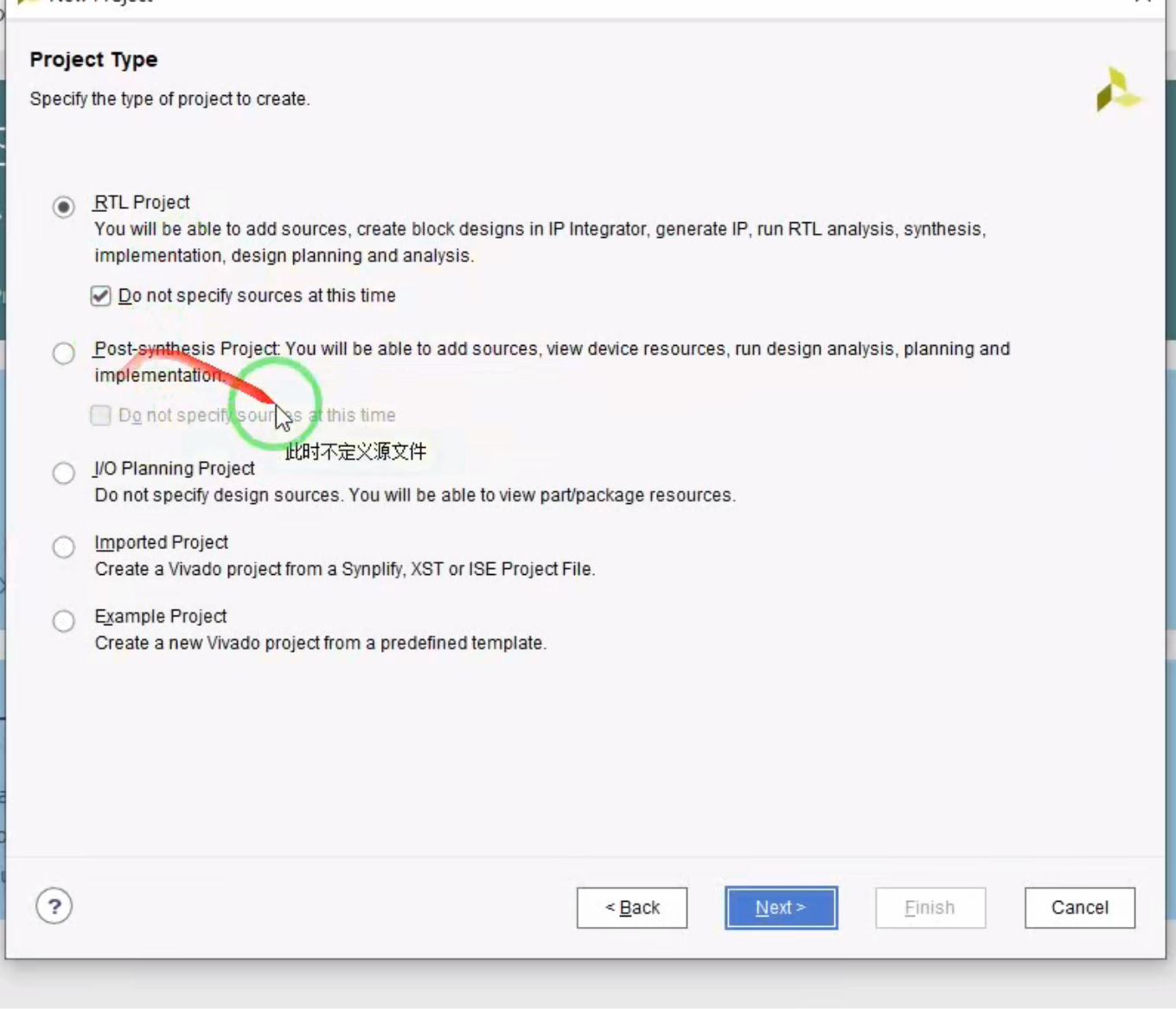

新建工程的类型

勾选第一个对钩,不用添加现有源文件

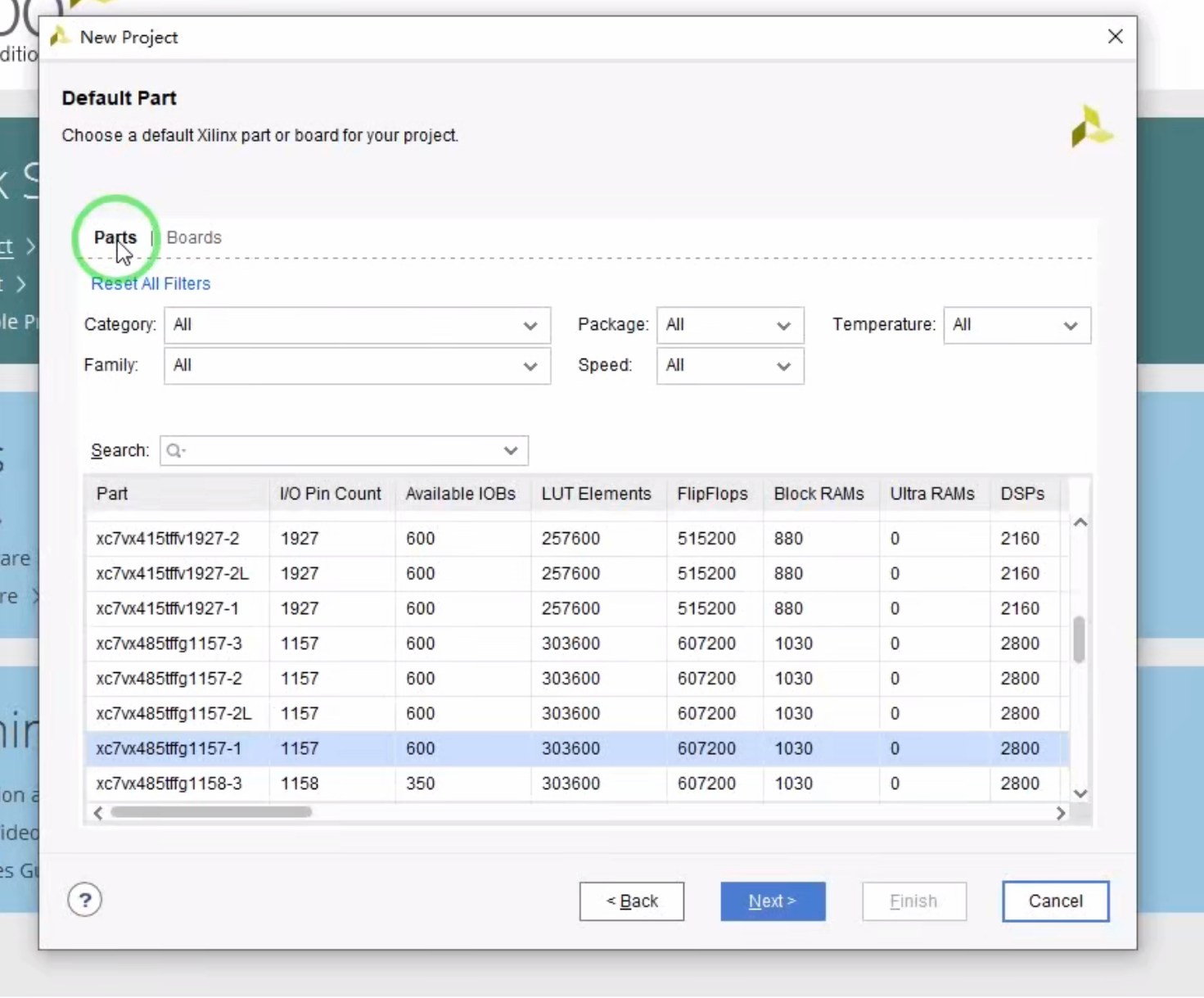

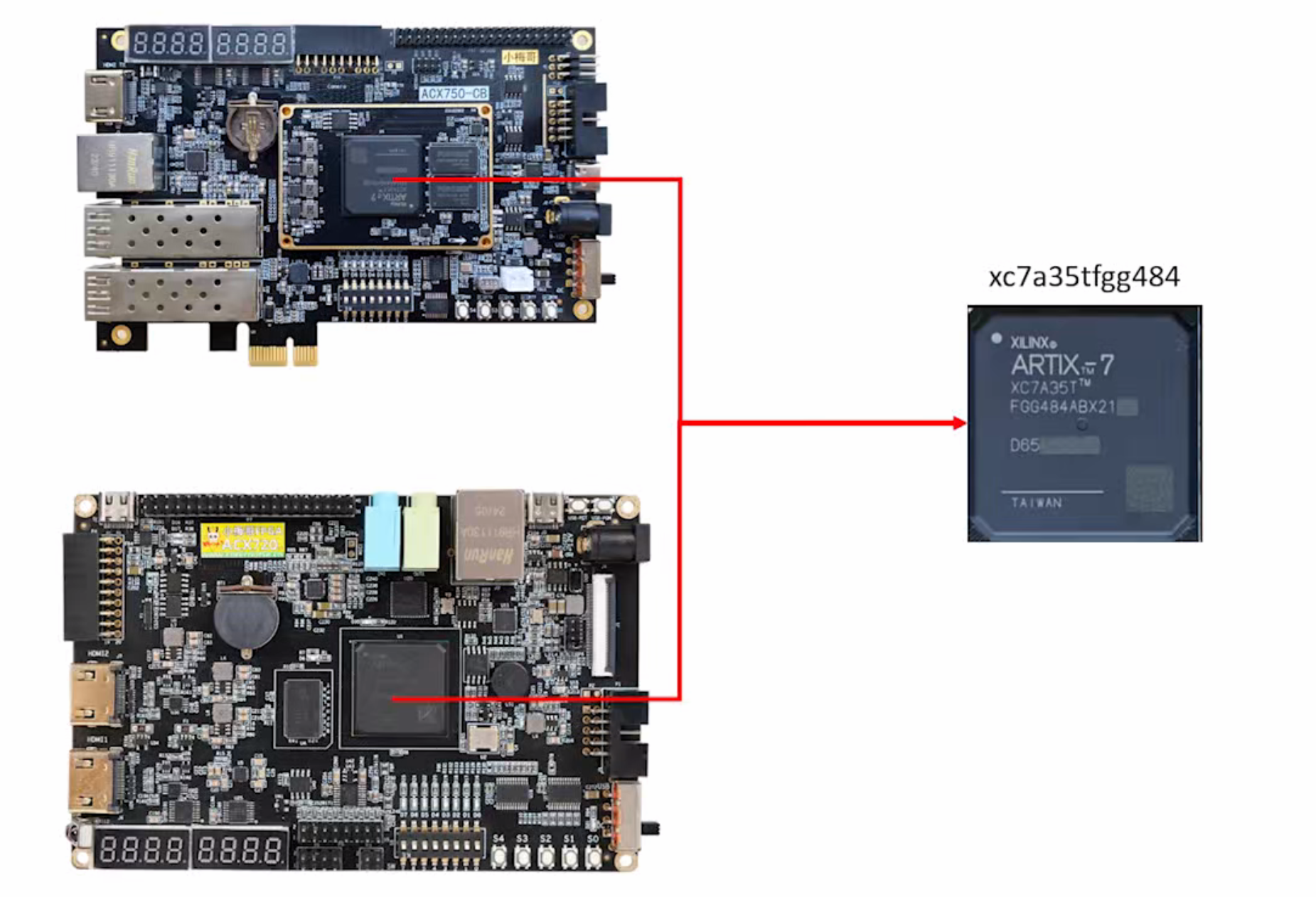

选择器件型号

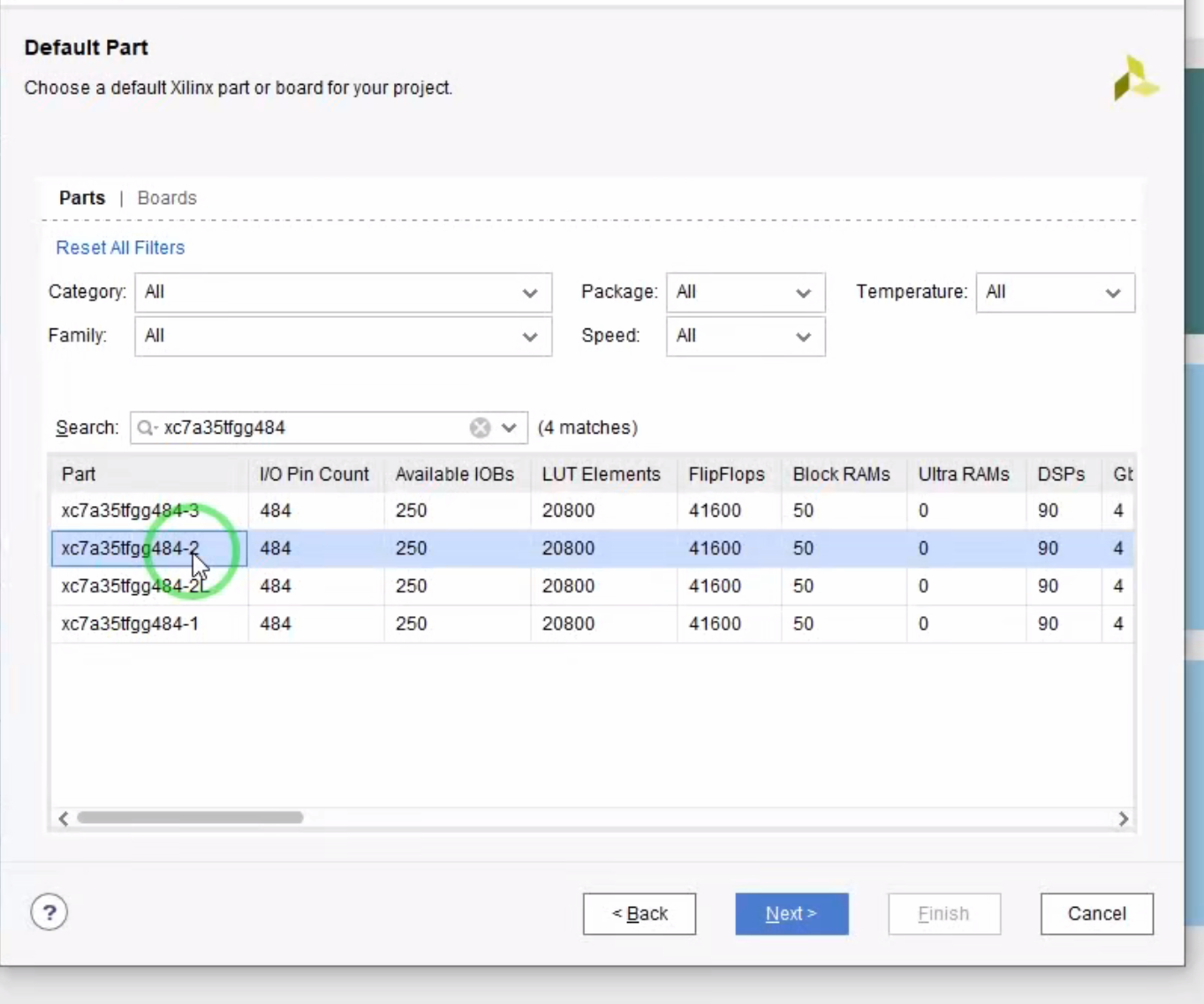

选择器件型号

搜索后选择这个型号

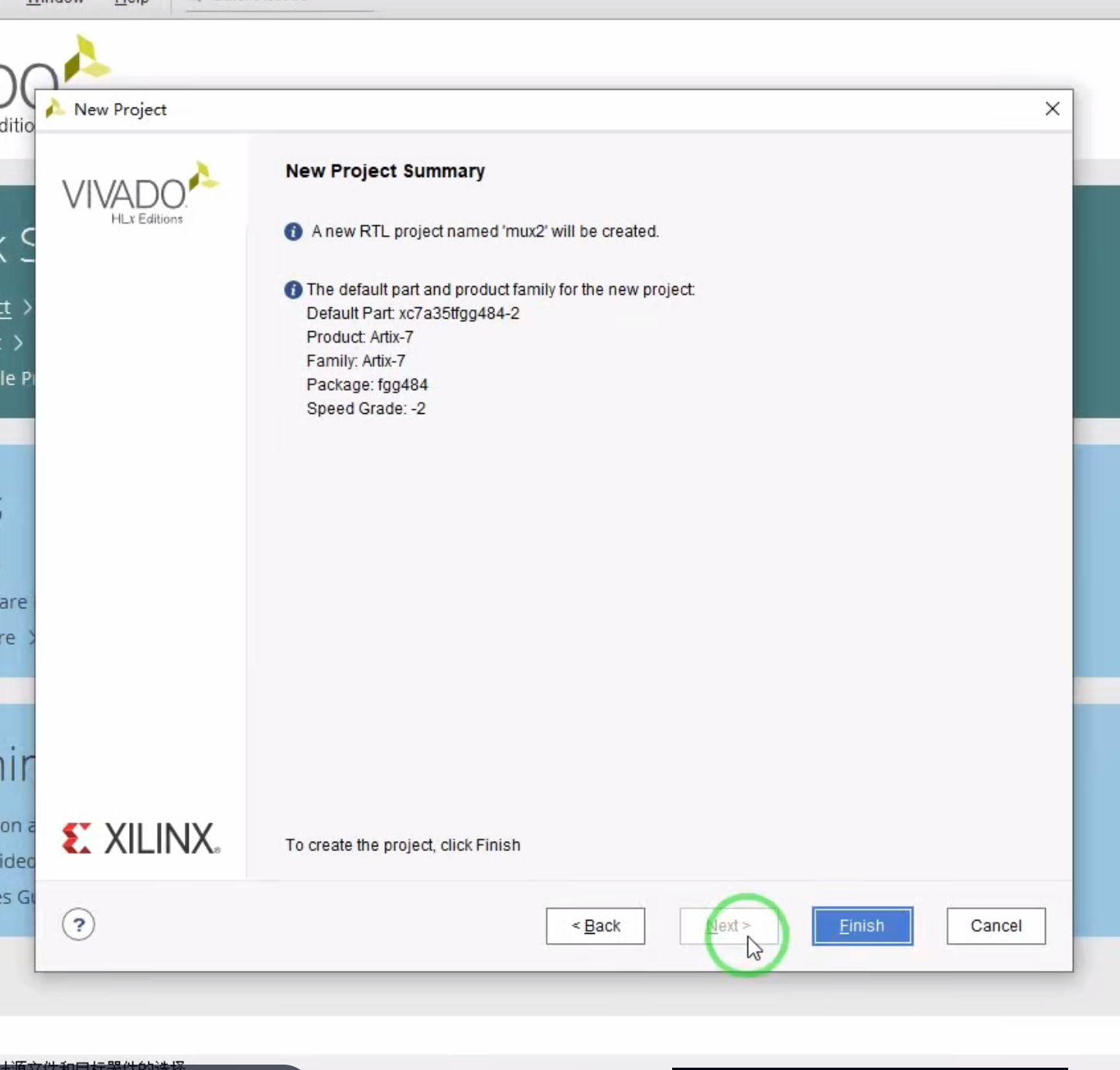

汇总页面,展示各项内容

点击finish

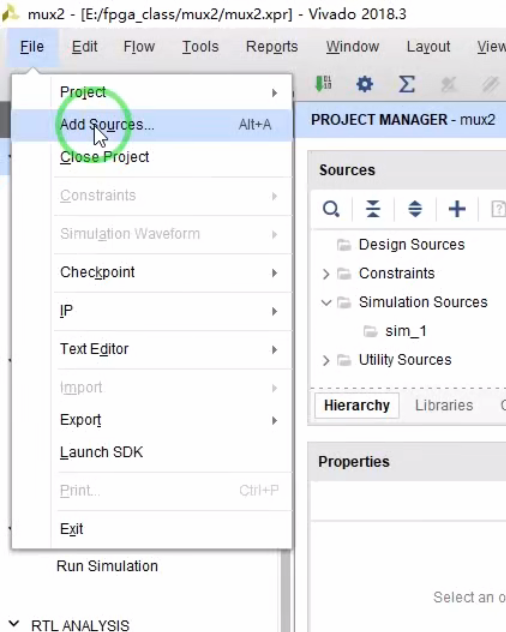

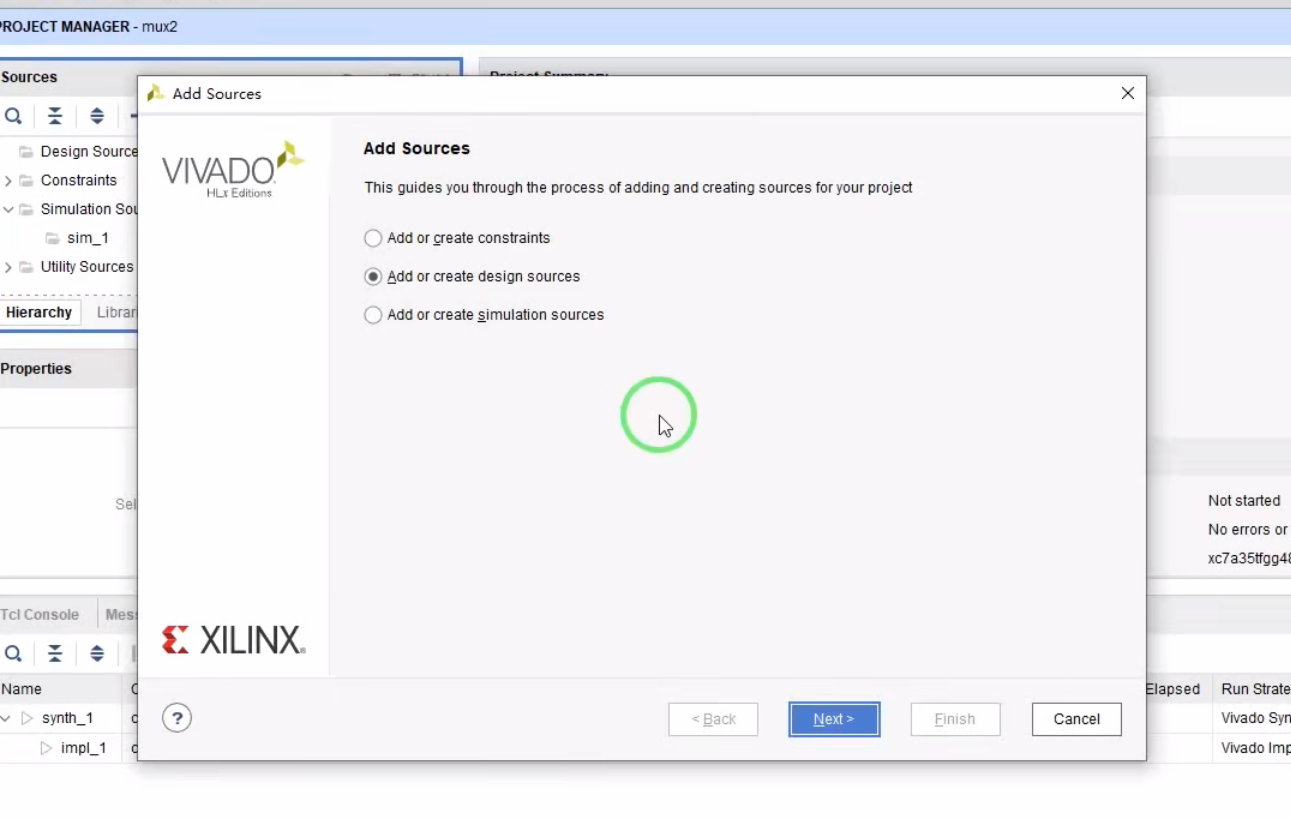

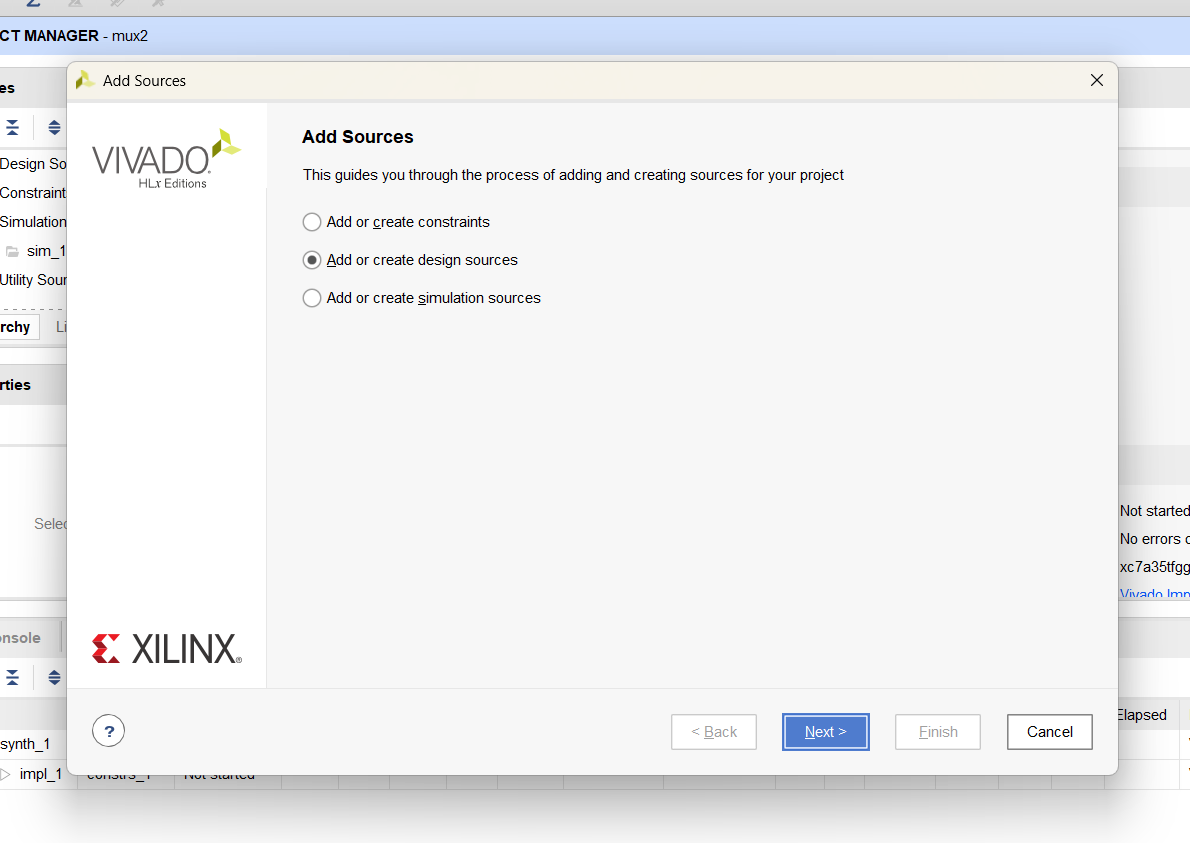

在file中找到 add sources创建源文件选项卡 或者在主界面按alt+a

第一个是创建约束

第二个是创建或添加设计源文件,就是verilog代码或者第三方网表

第三个是创建仿真源文件

选择第二个

点击next

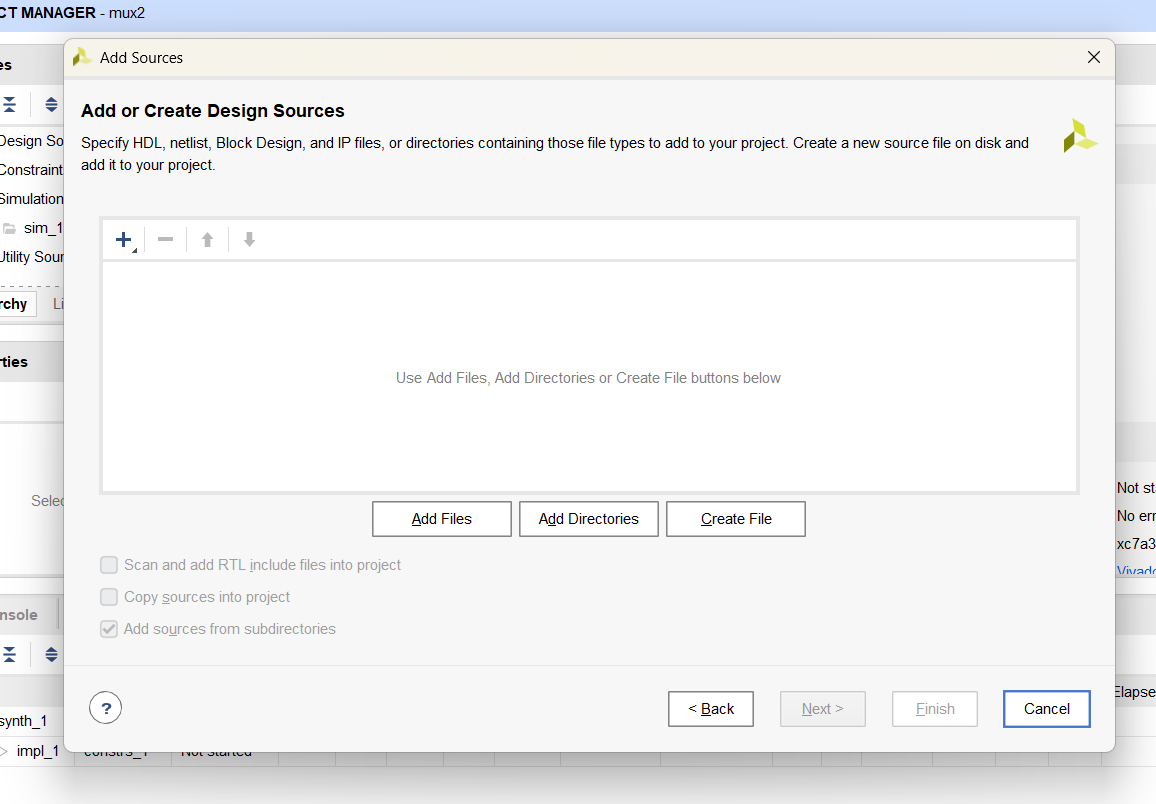

第一个是添加现有文件,第二个是,第三个是创建文件

点击第三个

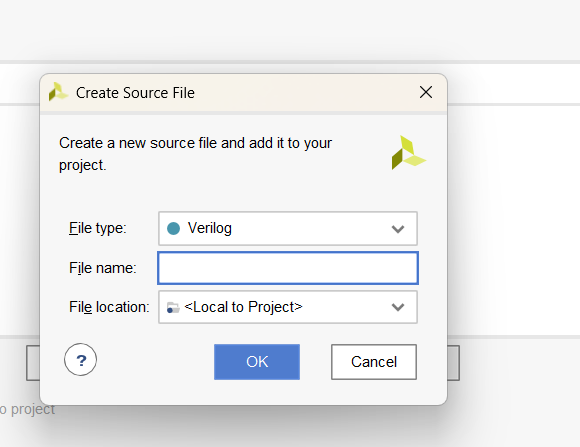

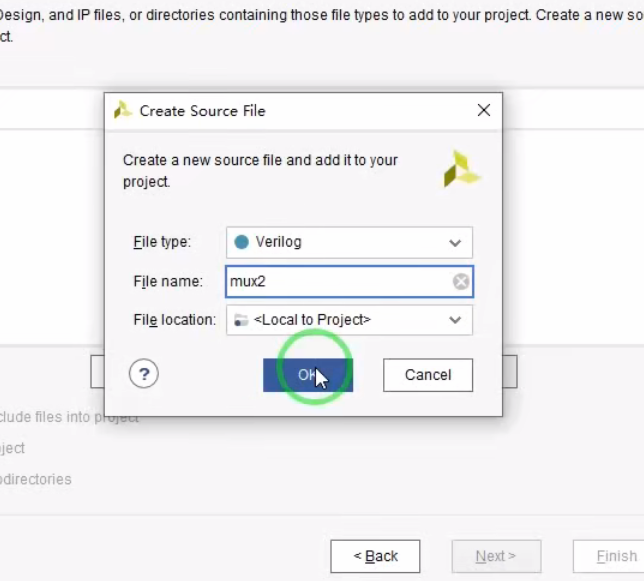

会要求起名,名称和工程保持一致就可以

点击OK,点击finish

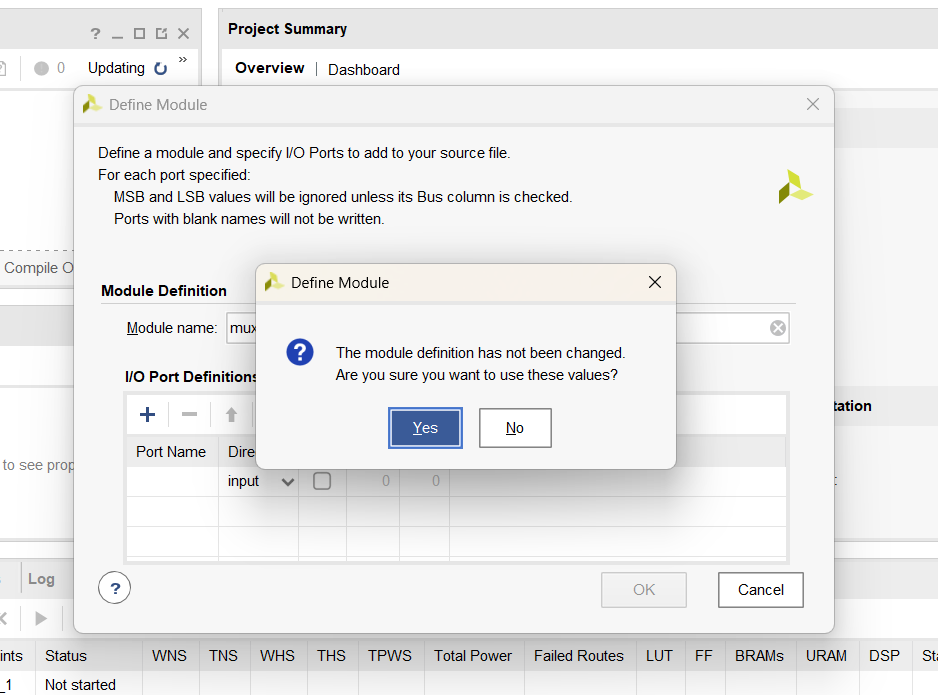

弹出设计页面的端口信息

点击OK,yes

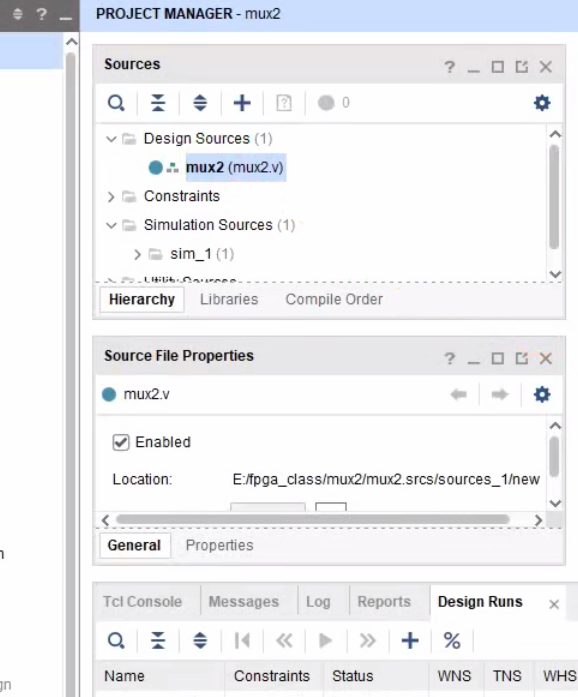

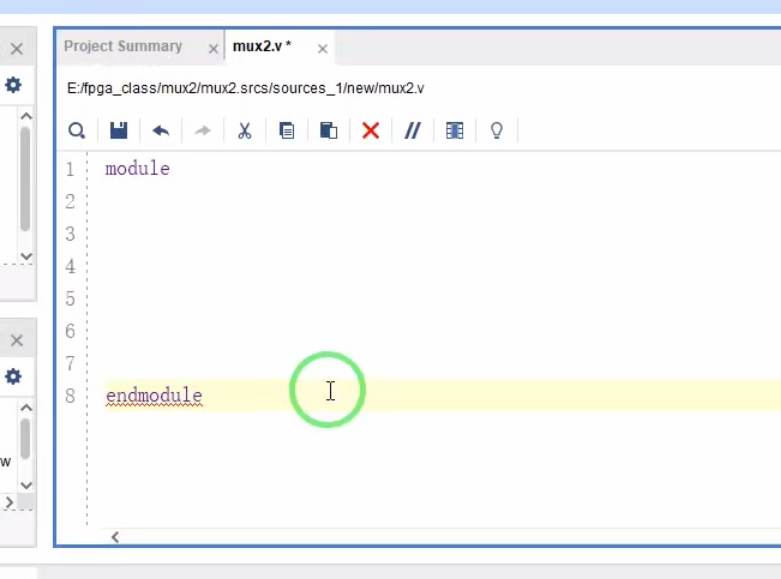

软件就自动帮创建好了

软件就自动帮创建好了

双击文件名打开

三、二选一多路器

sel为零,输出A

sel为1,输出B

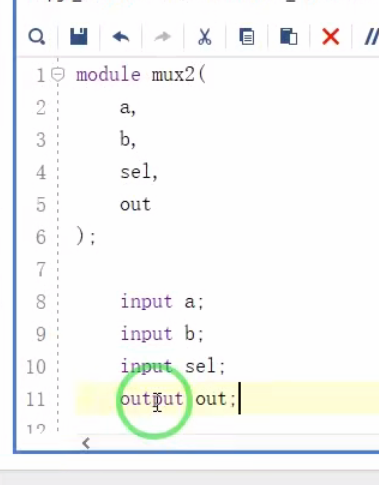

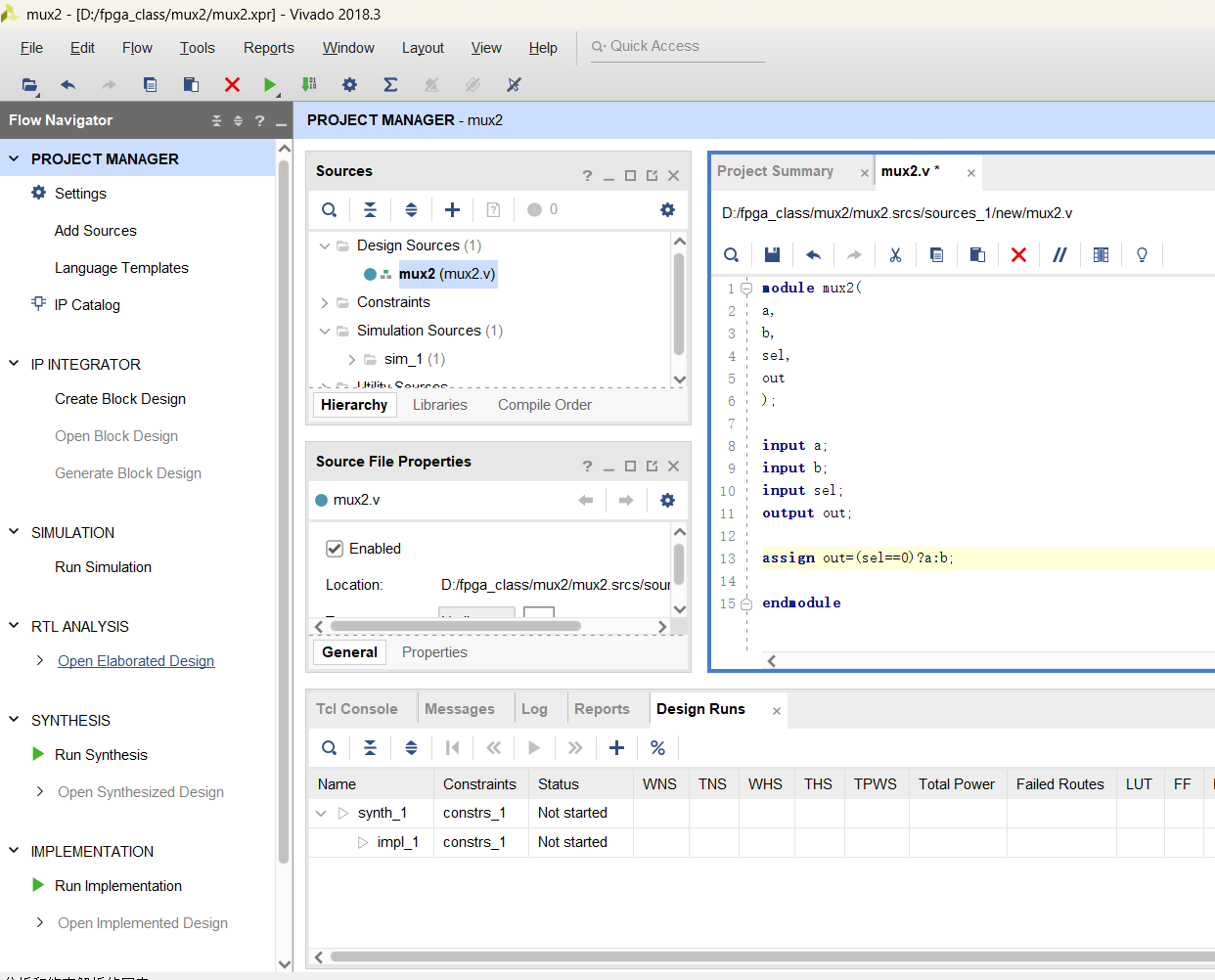

四、编写代码

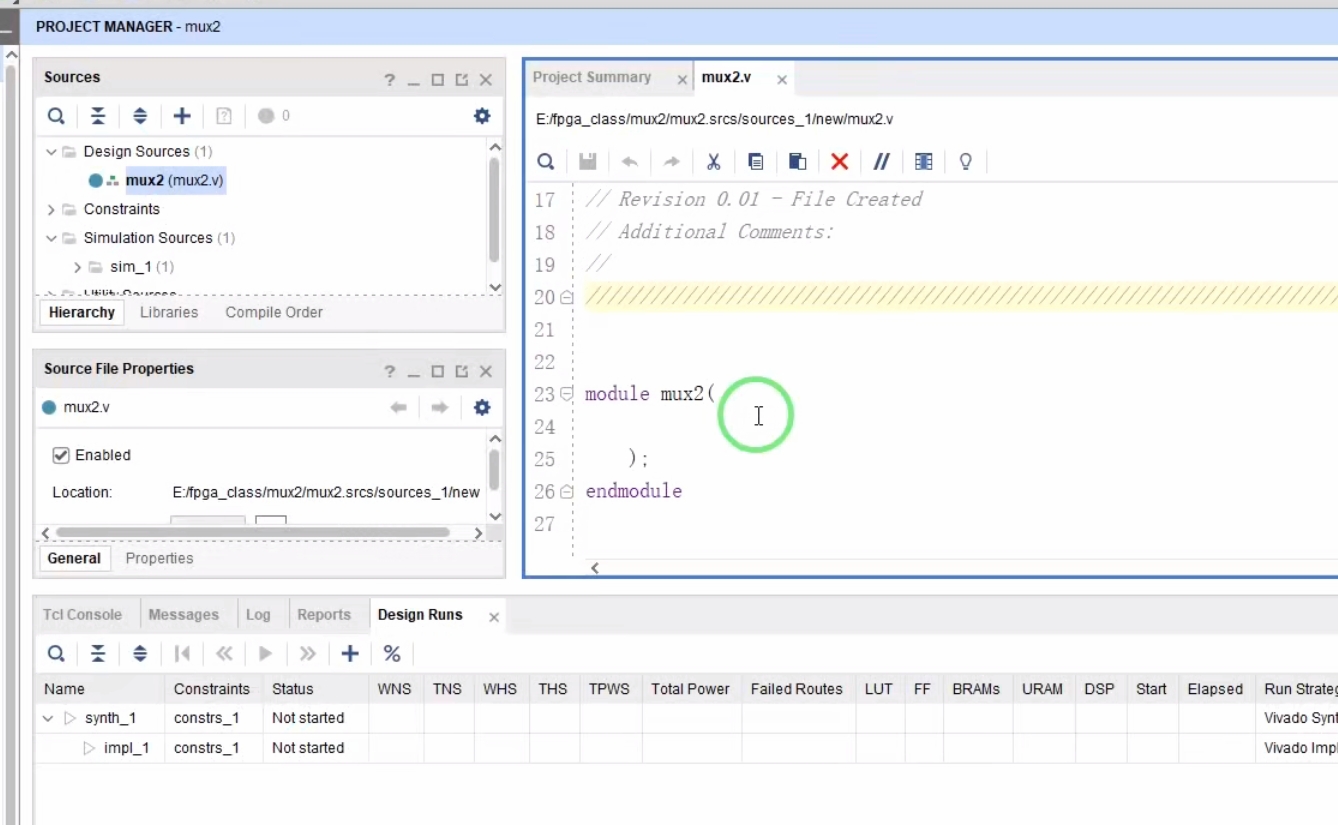

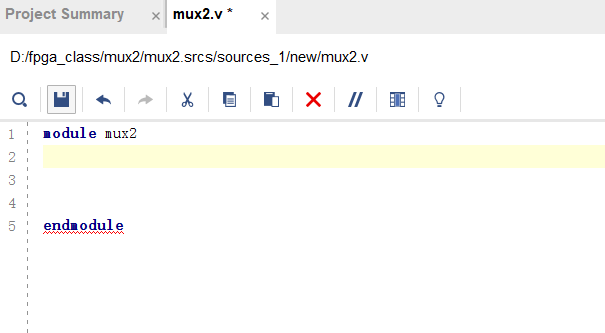

module代表模块开始

endmodule代表模块结束

mux2代表模块名称

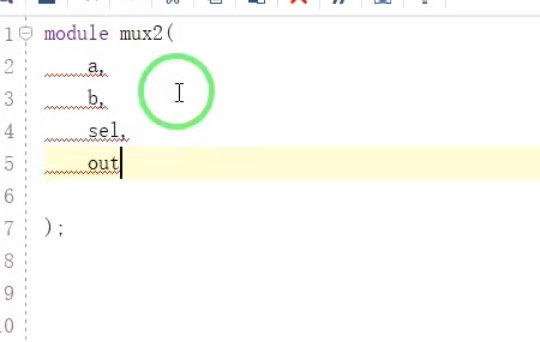

verilog的端口声明用括号结尾加分号,里面是端口列表

注意:verilog所有的代码是区分大小写的,所有字符多必须为英文

下面还需要对端口类型进行声明

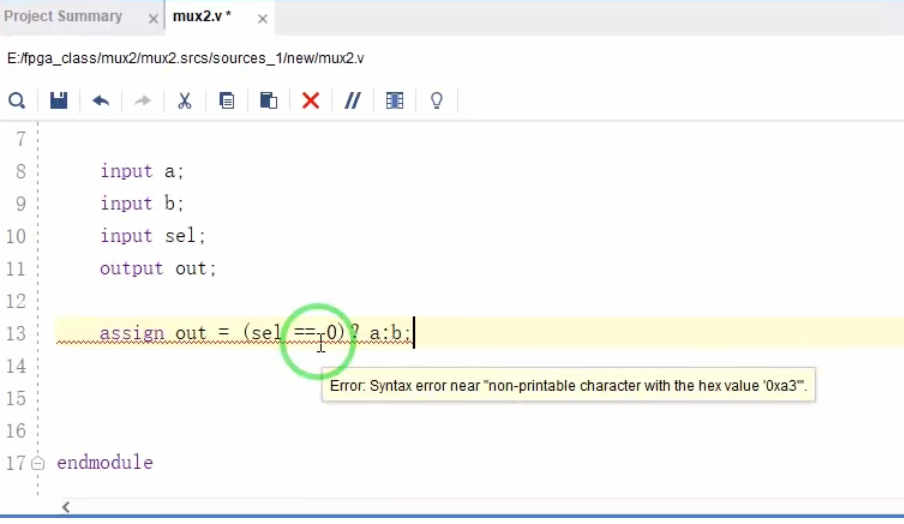

下面进行逻辑关系命名

用连续赋值语句assign,然后对二选一多路选择器进行逻辑描述

上面有报错——有一个无法打印的字符 一般无法打印的字符都是中文字符

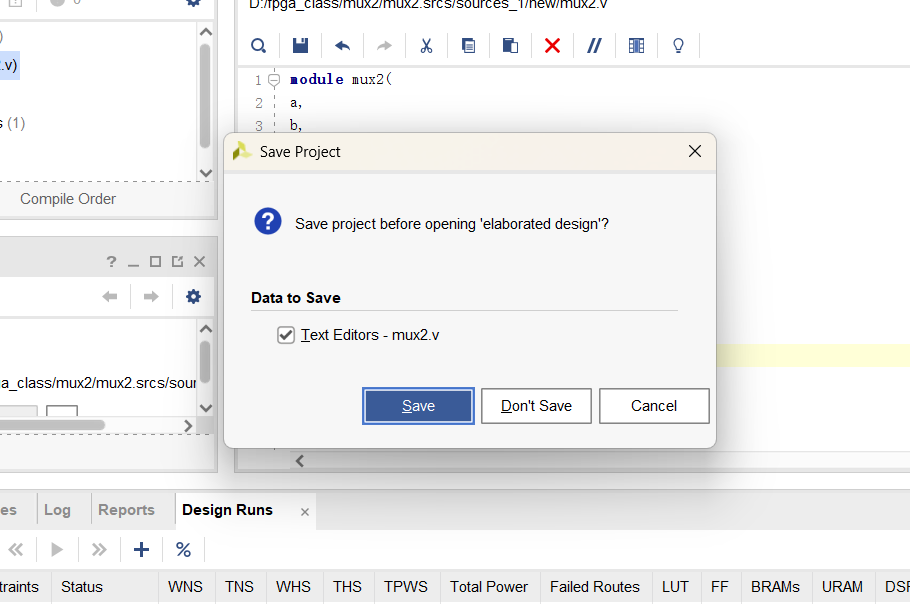

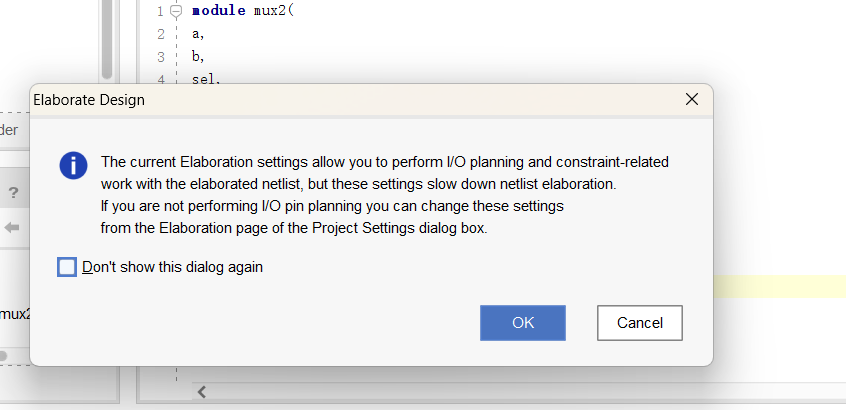

五、分析代码

点击左侧open。。。

点击save

点击OK

点击OK

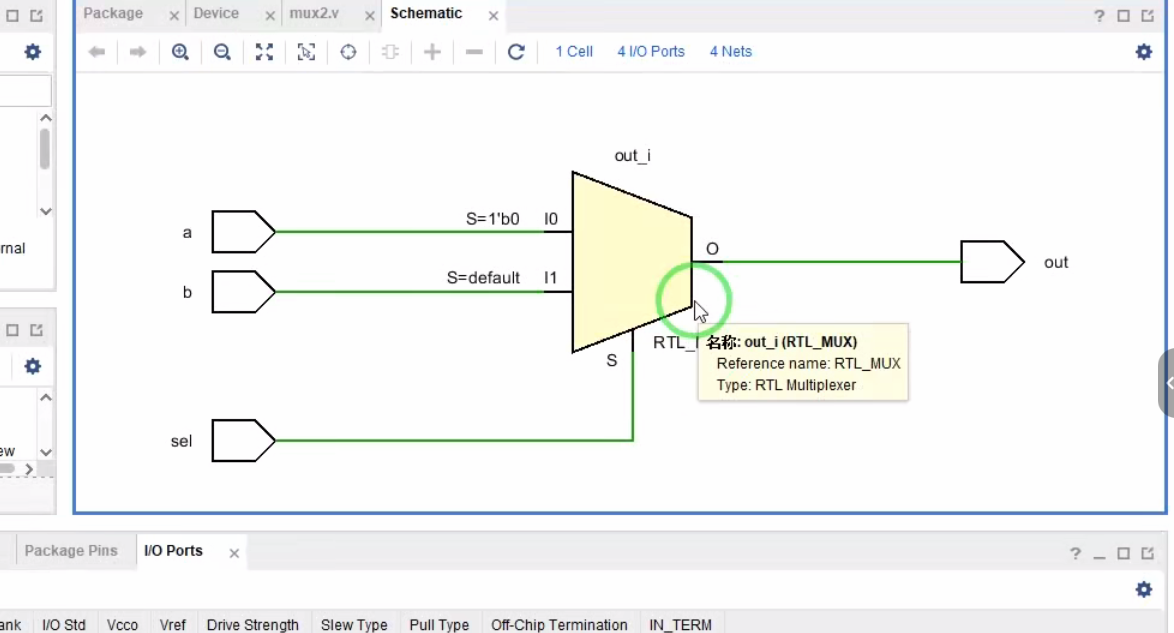

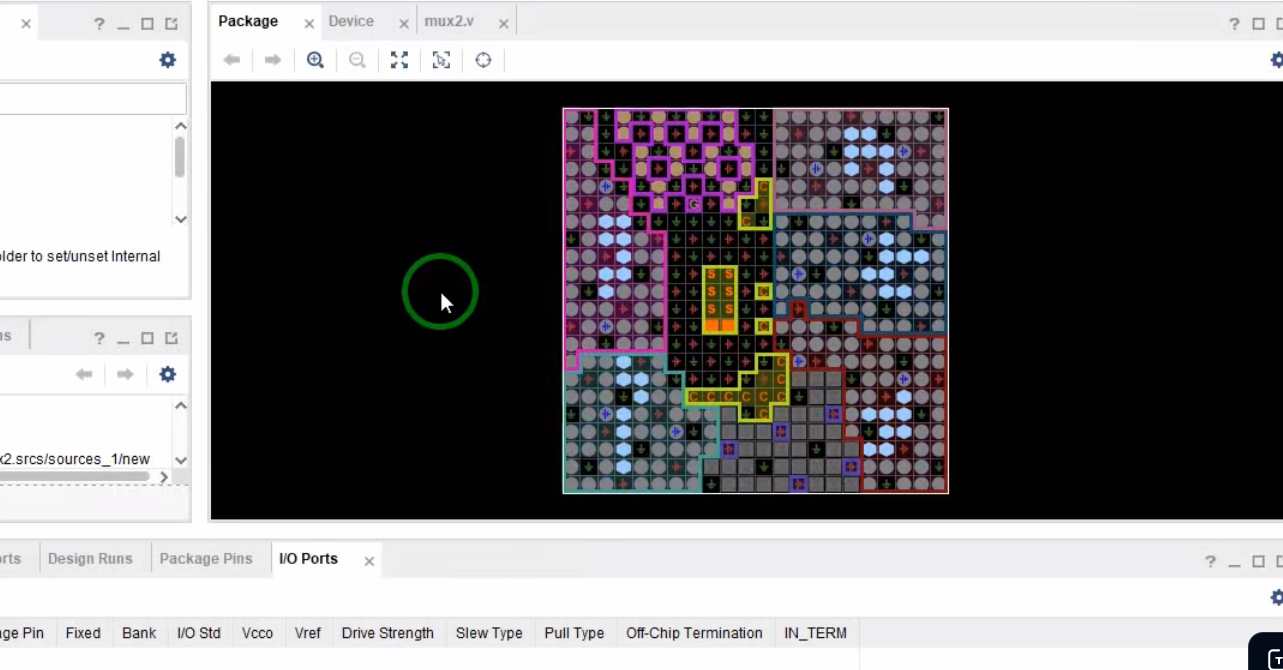

下面显示的分析结果

这是芯片的封装

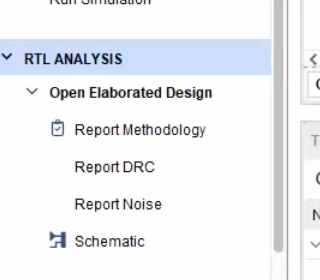

点击左侧schematic

就出现符号图