系统移植篇之uboot-4:UART

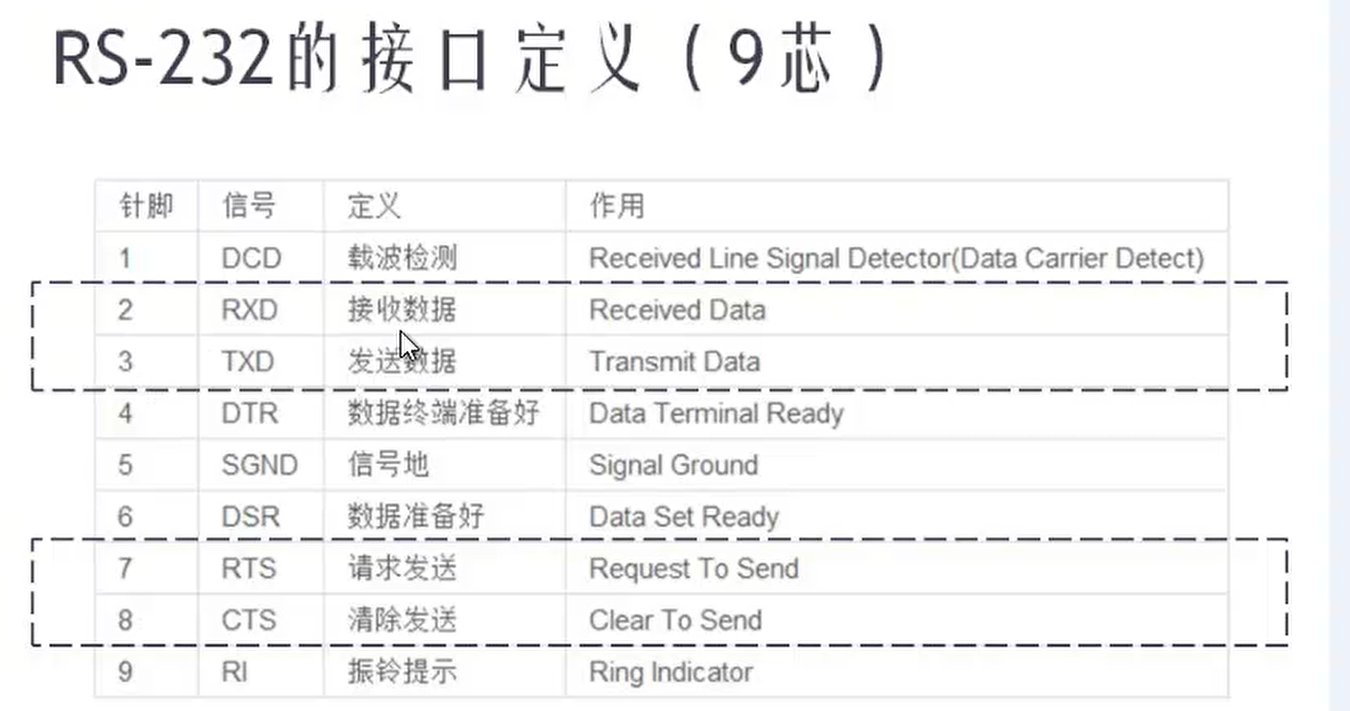

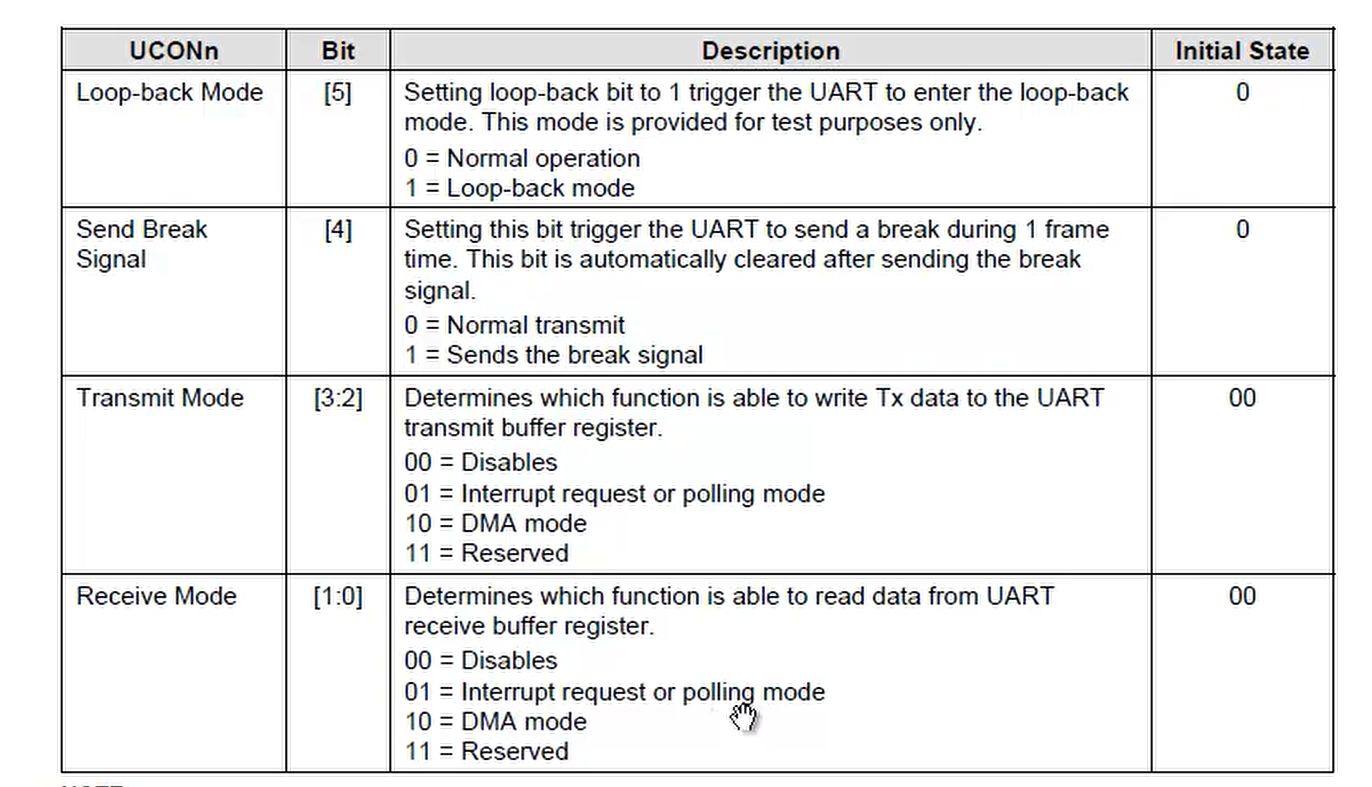

7,8是数据流控制

代码如下:

# u-boot-2012.10.tar\u-boot-2012.10\board\samsung\goni\lowlevel_init.S

...

...

.../* for UART */如何初始化UART串口,调试之类的都依赖这个bl uart_asm_init

...

...

...

/** uart_asm_init: Initialize UART's pins*/

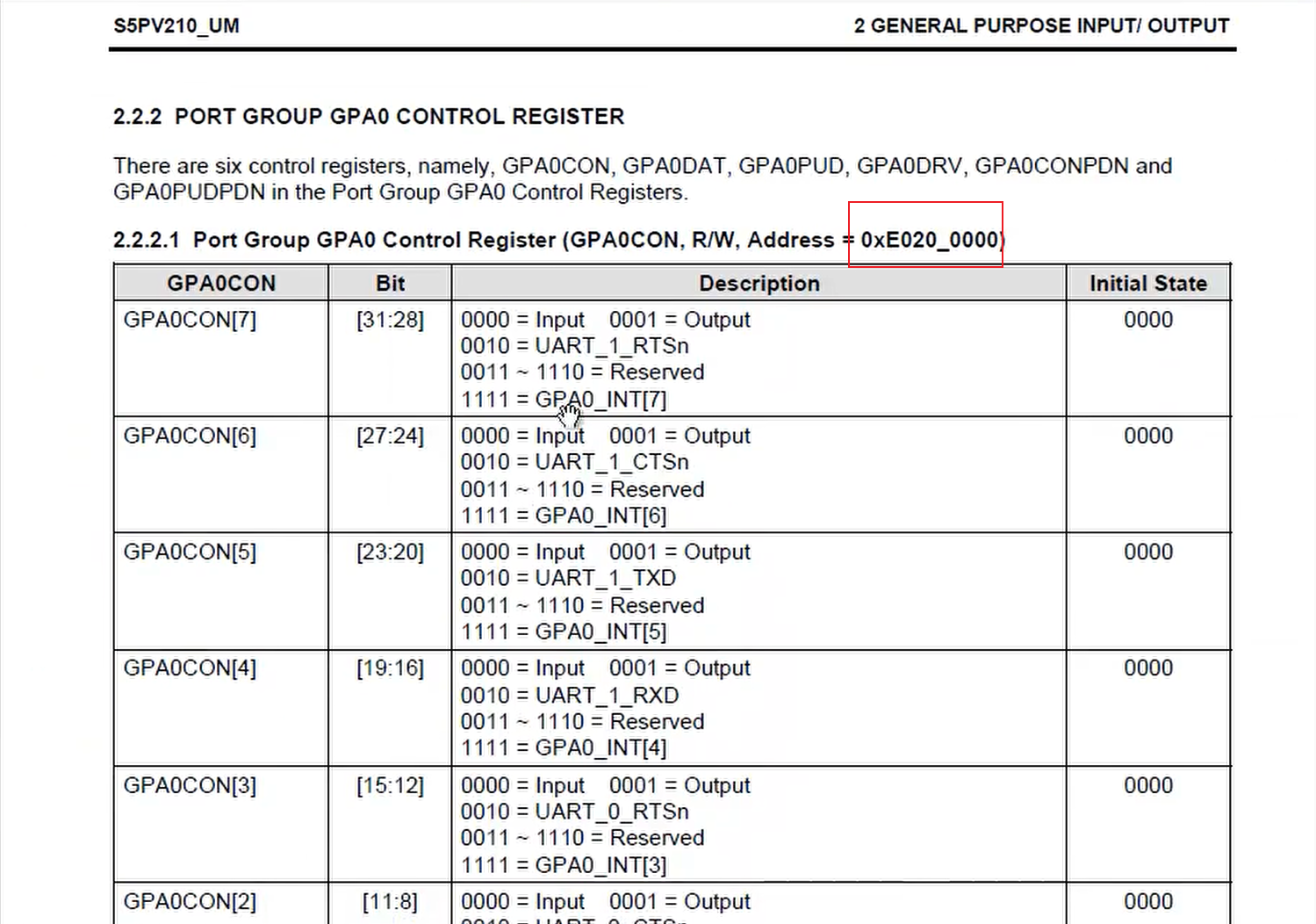

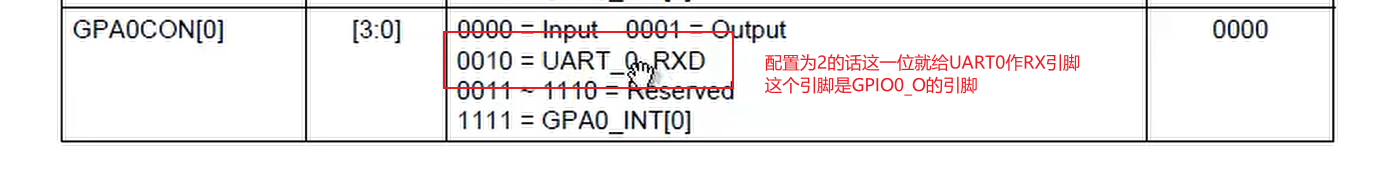

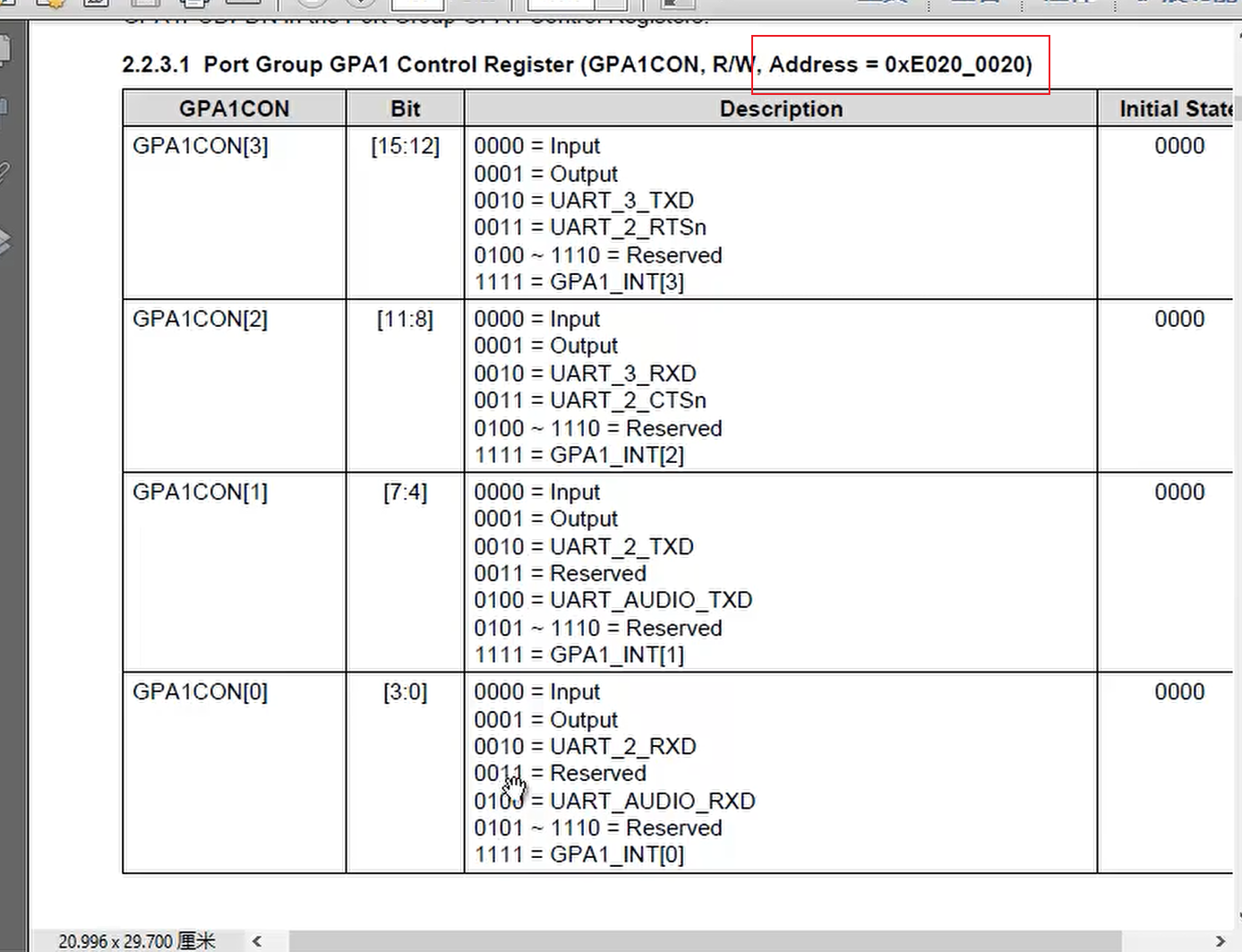

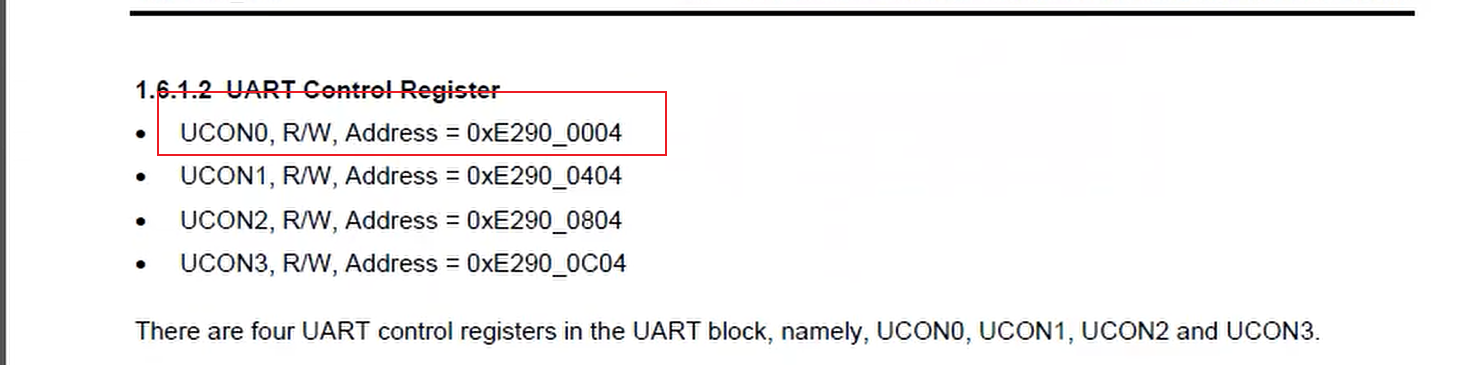

uart_asm_init:/* set GPIO to enable UART0-UART4 */mov r0, r8 # 将r8移到r0 = 0xE020,0000ldr r1, =0x22222222 # 将0x22222222移到r1str r1, [r0, #0x0] @ S5PC100_GPIO_A0_OFFSET #看锚点1,把r1回写到r0,把这些GPIO引脚配置为UART端口ldr r1, =0x00002222 str r1, [r0, #0x20] @ S5PC100_GPIO_A1_OFFSET 把r1回写到r0+0x20地址处,看锚点2/* Check S5PC100 */cmp r7, r8 #再次判断是110还是100型号的bne 110f #not equal向前跳转到110

...

...

...

110:/** Note that the following address* 0xE020'0360 is reserved address at S5PC100*//* UART_SEL MP0_5[7] at S5PC110 */ 下面这一段是配置MP0_5的代码,对我们210开发板没有什么意义,就不看了,这里面并没有对UART的寄存器进行配置,那么等会儿这里需要手动配置add r0, r8, #0x360 @ S5PC110_GPIO_MP0_5_OFFSETldr r1, [r0, #0x0] @ S5PC1XX_GPIO_CON_OFFSETbic r1, r1, #(0xf << 28) @ 28 = 7 * 4-bitorr r1, r1, #(0x1 << 28) @ Outputstr r1, [r0, #0x0] @ S5PC1XX_GPIO_CON_OFFSETldr r1, [r0, #0x8] @ S5PC1XX_GPIO_PULL_OFFSETbic r1, r1, #(0x3 << 14) @ 14 = 7 * 2-bitorr r1, r1, #(0x2 << 14) @ Pull-up enabledstr r1, [r0, #0x8] @ S5PC1XX_GPIO_PULL_OFFSETldr r1, [r0, #0x4] @ S5PC1XX_GPIO_DAT_OFFSETorr r1, r1, #(1 << 7) @ 7 = 7 * 1-bitstr r1, [r0, #0x4] @ S5PC1XX_GPIO_DAT_OFFSET# 写自己的代码了,给自己后面的调试打下基础,看锚点3ldr r0, =0xE2900000ldr r1, =3 #8位数据位 ULCON0 = 3str r1,[r0]ldr r1,=0x305str r1,[r0,#0x4] UCON0=0x305ldr r1,=1str r1,[r0,#0x8] UFCON0=0ldr r1,=0str r1,[r0,#0xC] UFCON0=0ldr r1,=34str r1,[r0,#0x28] UBRDIV0=34ldr r1,=0xDFDD str r1,[r0,#0x2C] udivslot0=13'1接下来往串口里面写数据了,因为是FIFO缓冲区,所以只用往同一个地址写就行了看锚点6,写数据写到0xE290,0020ldr r0,=0xE2900020ldr r1,=0x55 UTH0='U'str r1,[r0]ldr r1,=0x61 UTH0='a'str r1,[r0]ldr r1,=0x72 UTH0='r'str r1,[r0]ldr r1,=0x74 UTH0='t'str r1,[r0]下面是win里面的换行方式\r\nldr r1,=0xA UTH0='\r'str r1,[r0]ldr r1,=0xD UTH0='\n'str r1,[r0]锚点1

128面

这里面配的全都是关于串口的GPIO应用

锚点2

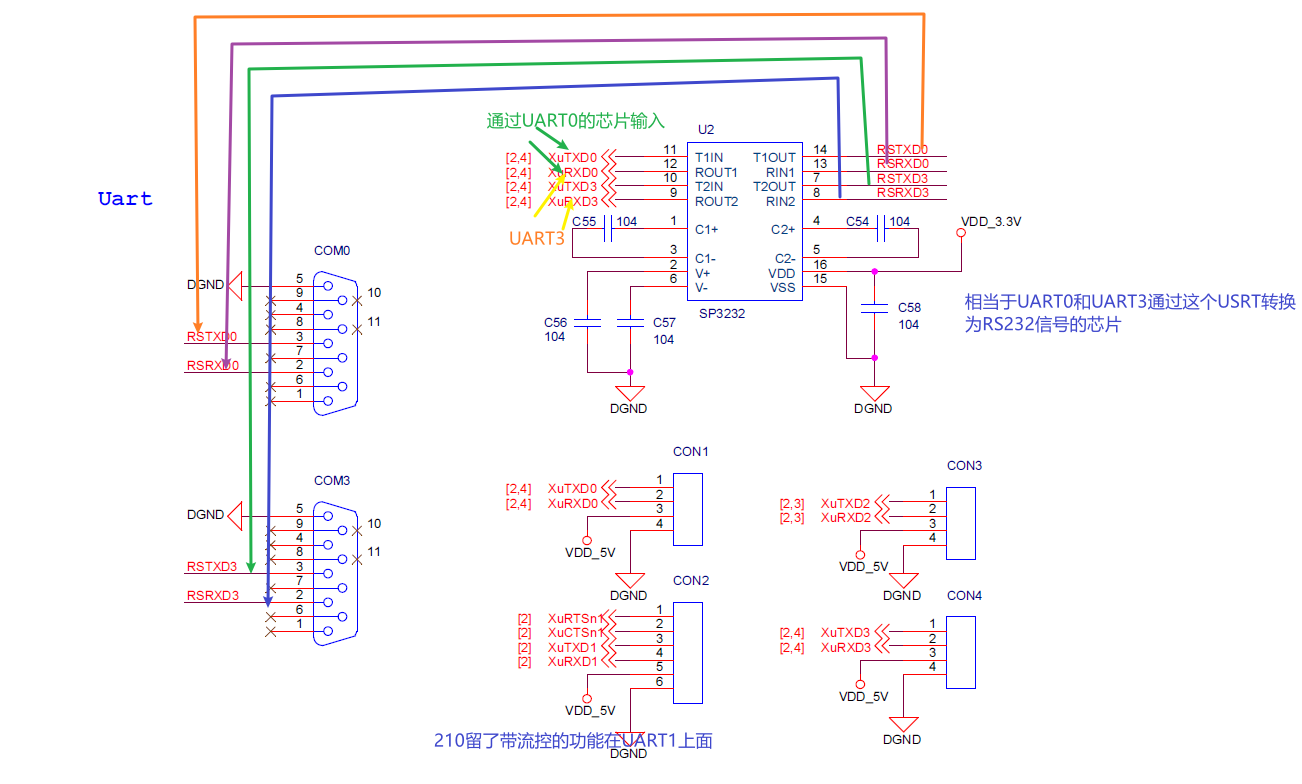

配置UART2和UART3

和前面0和1的区别主要是其省略了一些流控制的引脚

锚点3

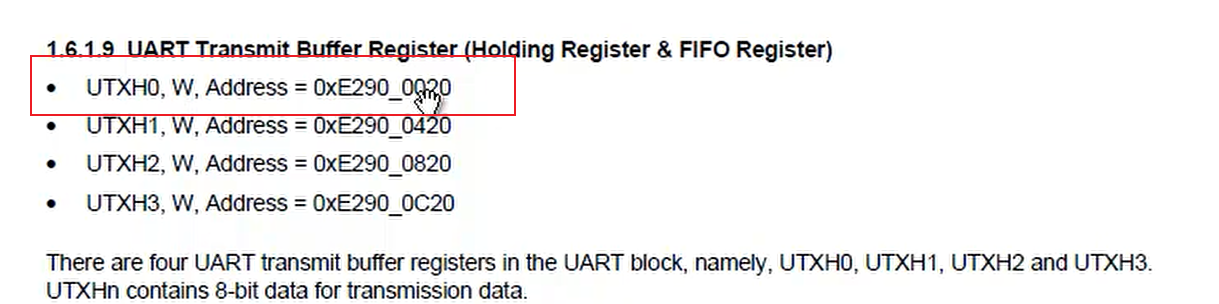

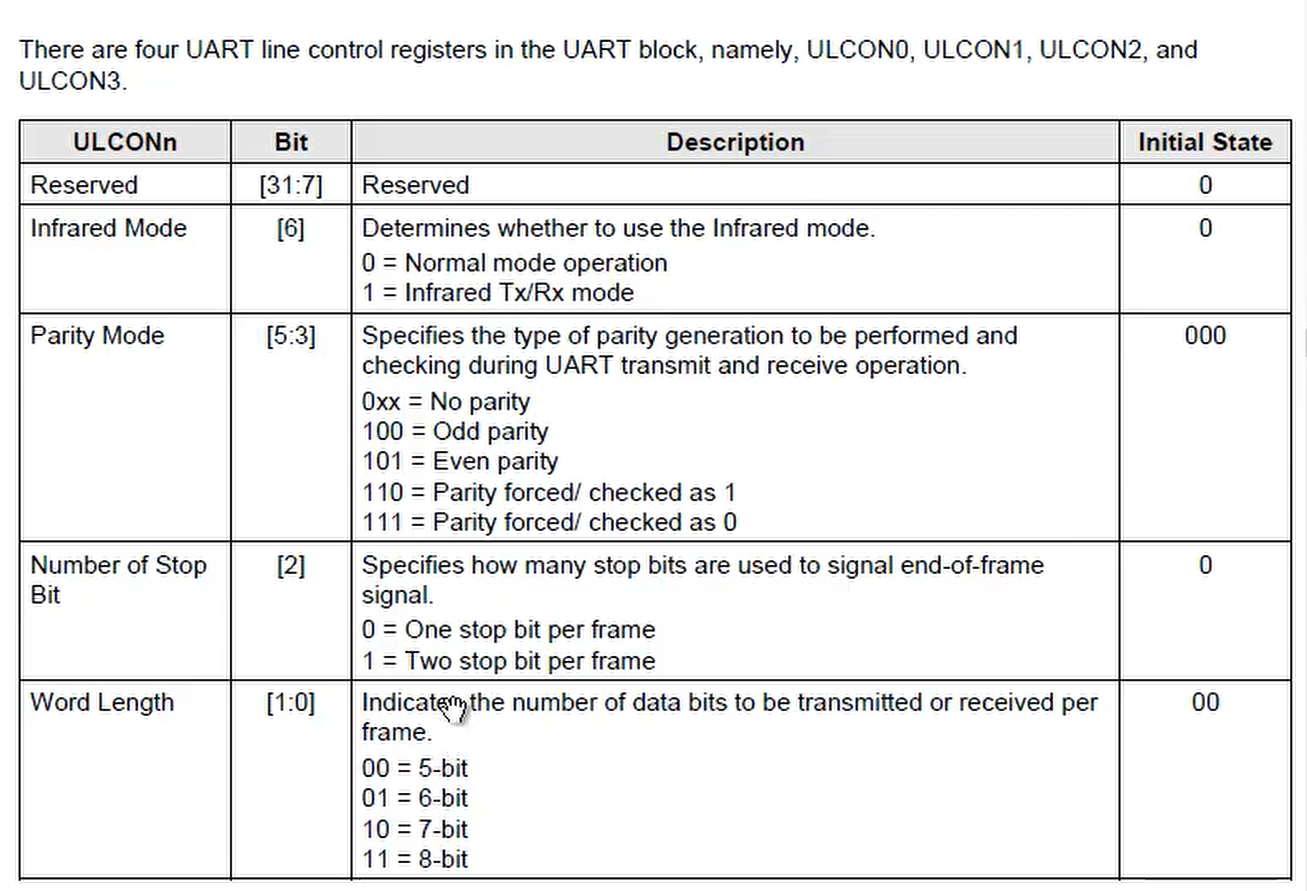

867面

8-bit,一位停止位,不用奇偶校验,不用红外模式 就是0x0000,0011

锚点4

前两位(Receive Mode):一般最常用01这种模式, 中断或者polling查询模式(因为我们一开始禁止中断了,所以最好是查询模式,写了一个程序不断的检查,sdatas后面有一个接收位,位是1的话就代表已经收到数据了,是0代表没有收到数据),10就是DMA模式

锚点5

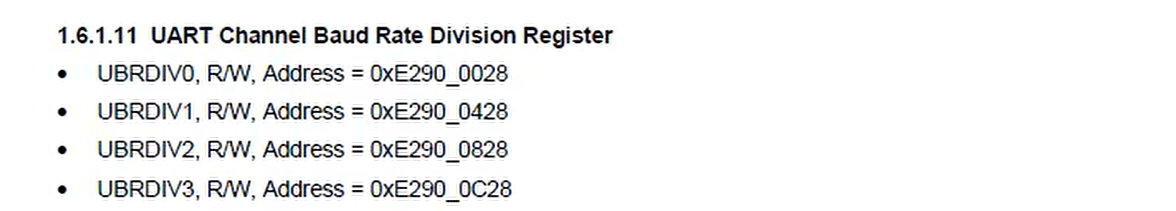

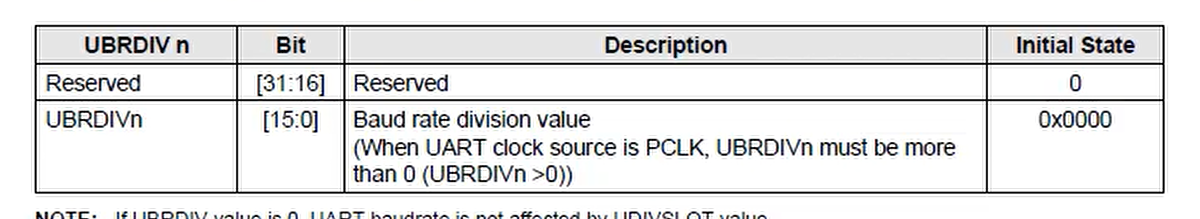

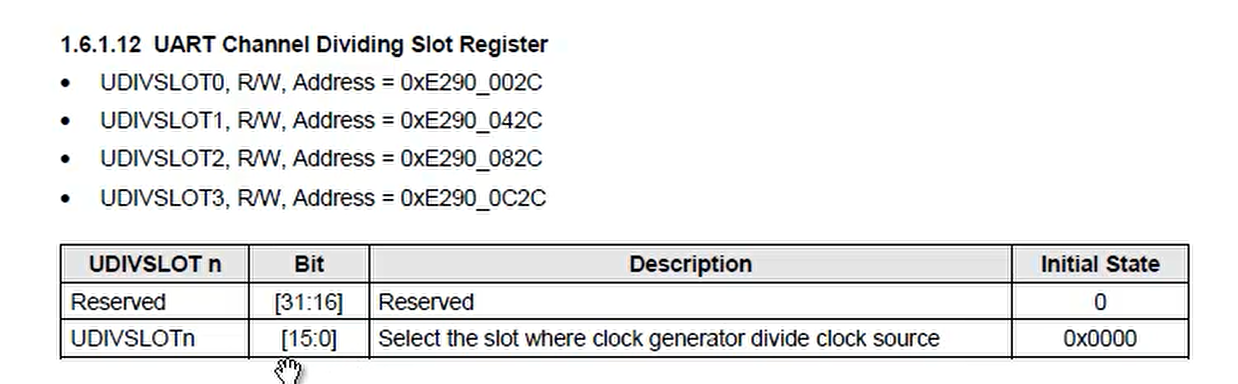

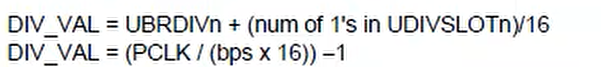

配置分频系数

计算公式如下:

UBRDIVn:

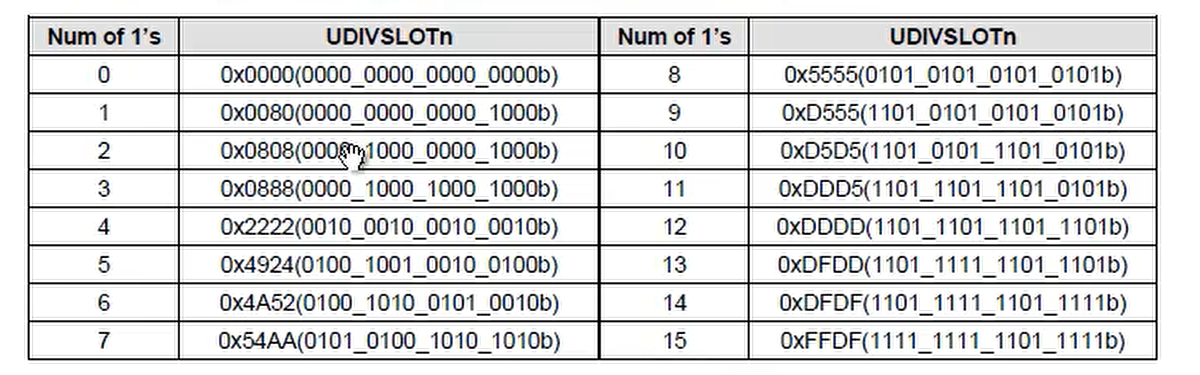

num of 1's in UDIVSLOTn : UDIVSLOTn中1的个数,看手册第880面,下面是官方推荐的值,并不强制

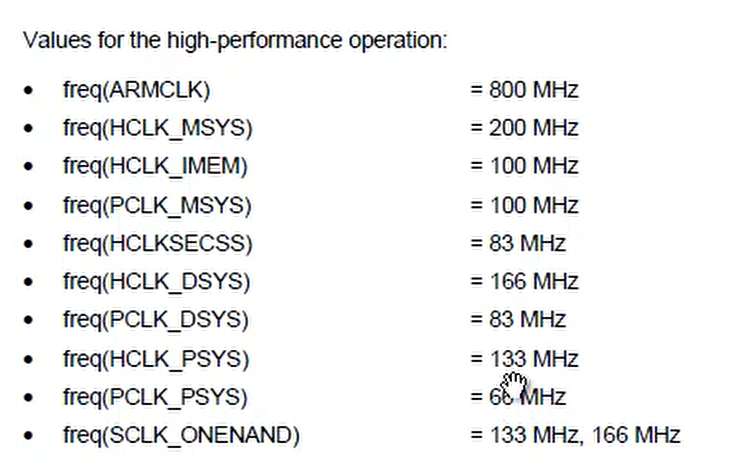

PCLK是66MHz是已知量,手册第351页

bps我们一般是选择115200这个值

假设UDIVSLOTn是0x0080,那么1的个数就是1

接下来算UBRDIVn为66M/(115200*16) - 1 - 1/16 = 34.8072917-0.0625 = 34.74479 ≈35如果报文过长的话,误差就会过大,会有一些畸变的,产生累计错误, 如果使x/16接近于0.8072917,那么这里就是34整数了产生的畸变会小很多, 使用13/16,也就是UDIVSLOTn采用

0xDFDD

锚点6