找人做网站做的很烂网站自助建设推广

实验一 数据选择器实验报告

目录

- 实验目的

- 实验内容

- 原理描述

- Verilog HDL设计源代码

- Testbench仿真代码及仿真结果

- XDC文件配置

- 下板测试

- 实验体会

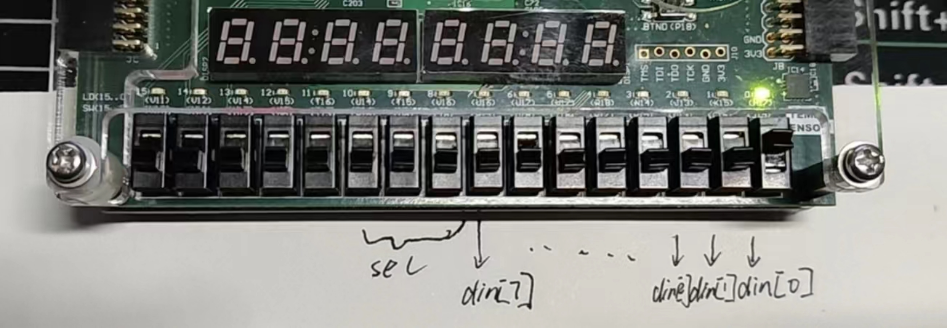

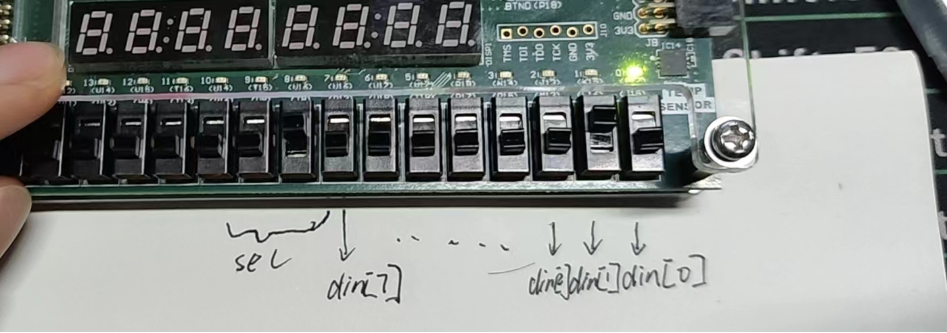

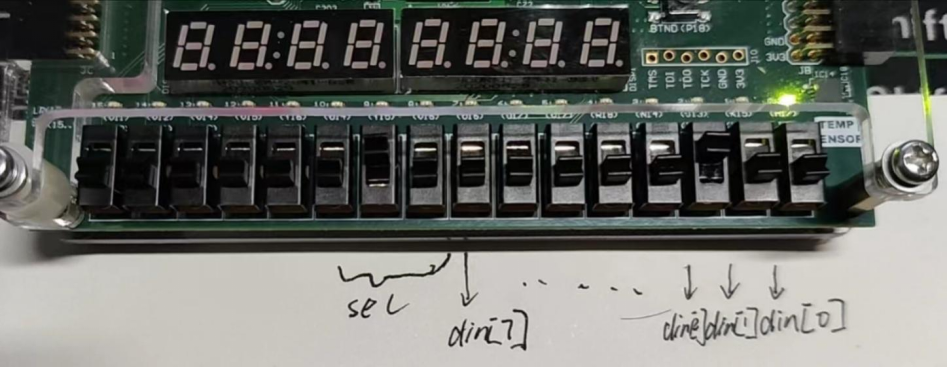

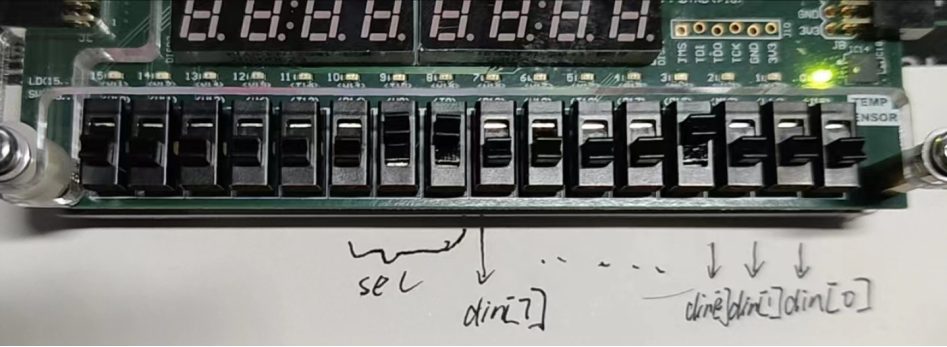

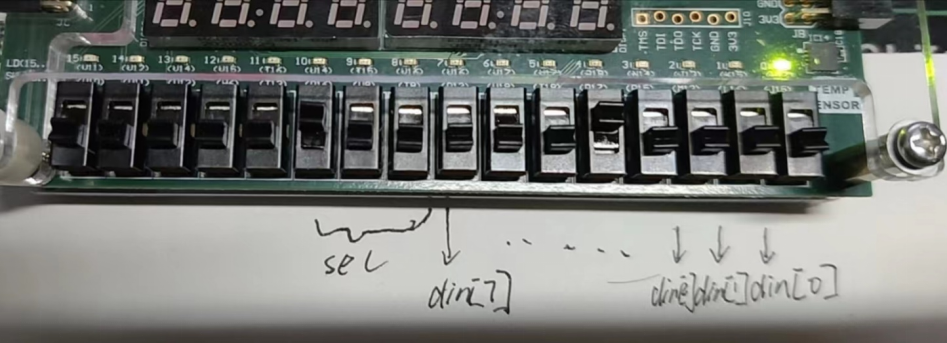

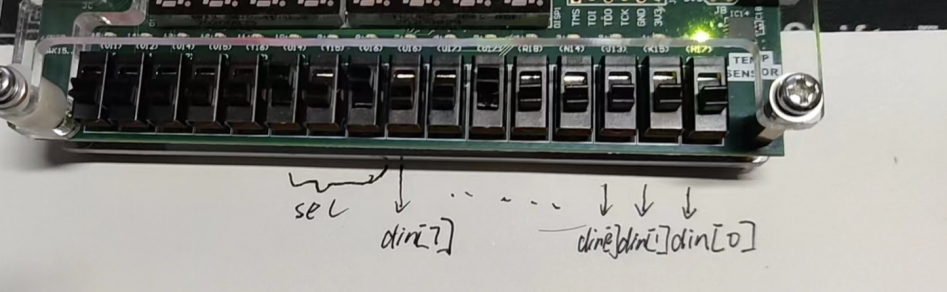

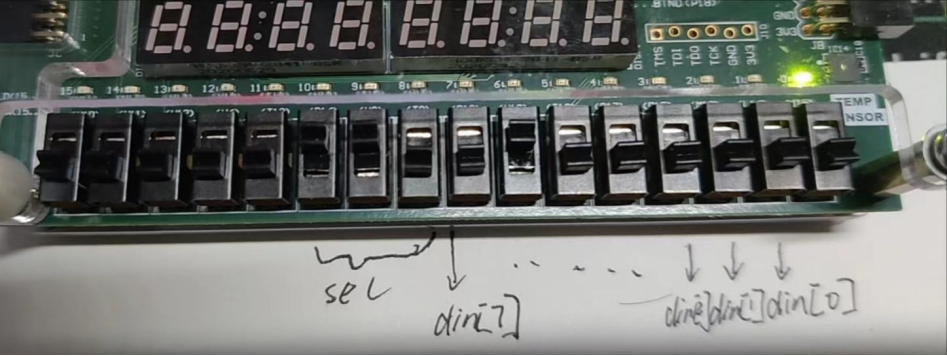

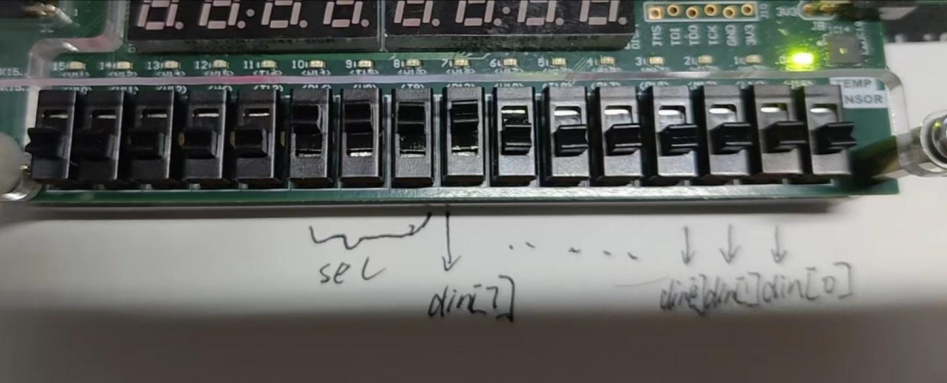

- 实验照片

实验目的

- 熟悉使用Verilog HDL的三种不同描述方式进行基本逻辑电路建模,实现数据扩展。

- 学习使用Vivado进行逻辑设计的基本流程。

- 学习使用Nexys4 FPGA硬件开发板,了解开发板主要的外围接口。

- 了解设计源代码与仿真代码的区别。

实验内容

原理描述

八选一选择器有8个输入端口,通过3位二进制的选择信号(sel[2:0])选择其中一个输入作为输出。可以用Verilog的case语句(推荐)或if语句实现,case语句语法更简洁、整齐。

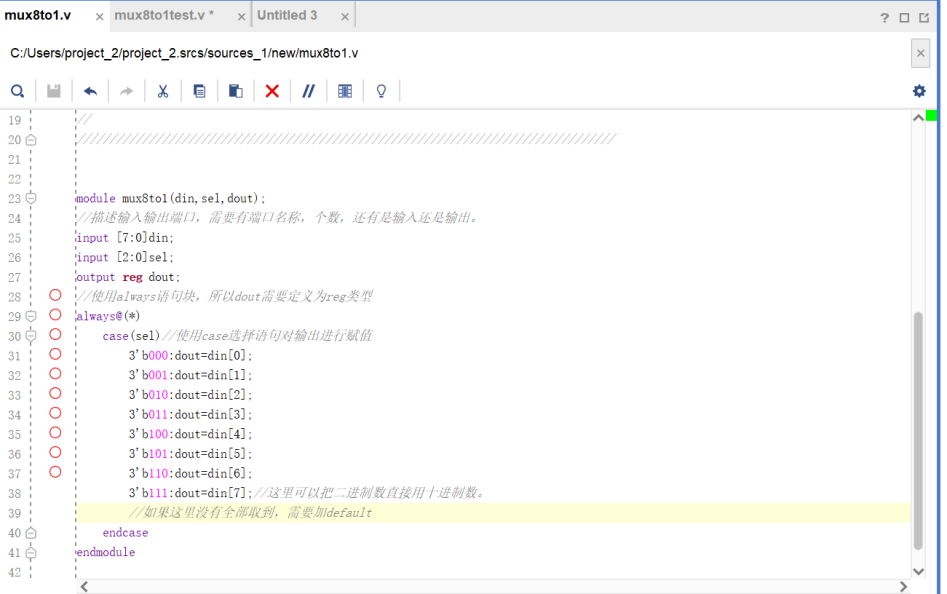

Verilog HDL设计源代码

// 8选1数据选择器

module mux8to1(input [7:0] din, // 8位输入数据input [2:0] sel, // 3位选择信号output dout // 输出数据

);

// 使用case语句描述

reg dout_r;

assign dout = dout_r;always @(*) begincase(sel)3'b000: dout_r = din[0];3'b001: dout_r = din[1];3'b010: dout_r = din[2];3'b011: dout_r = din[3];3'b100: dout_r = din[4];3'b101: dout_r = din[5];3'b110: dout_r = din[6];3'b111: dout_r = din[7];default: dout_r = 1'b0;endcase

endendmodule

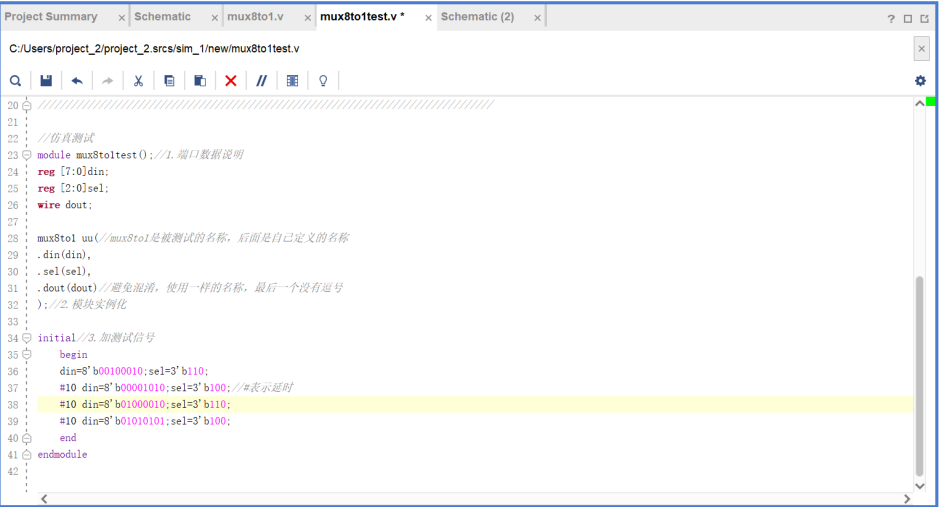

Testbench仿真代码及仿真结果

module testbench();reg [7:0] din;reg [2:0] sel;wire dout;mux8to1 uut(.din(din),.sel(sel),.dout(dout));initial begin// 依次测试每一路高电平输出din = 8'b00000001; sel = 3'b000; #10;$display("din=%b, sel=%b, dout=%b", din, sel, dout);din = 8'b00000010; sel = 3'b001; #10;$display("din=%b, sel=%b, dout=%b", din, sel, dout);din = 8'b00000100; sel = 3'b010; #10;$display("din=%b, sel=%b, dout=%b", din, sel, dout);din = 8'b00001000; sel = 3'b011; #10;$display("din=%b, sel=%b, dout=%b", din, sel, dout);din = 8'b00010000; sel = 3'b100; #10;$display("din=%b, sel=%b, dout=%b", din, sel, dout);din = 8'b00100000; sel = 3'b101; #10;$display("din=%b, sel=%b, dout=%b", din, sel, dout);din = 8'b01000000; sel = 3'b110; #10;$display("din=%b, sel=%b, dout=%b", din, sel, dout);din = 8'b10000000; sel = 3'b111; #10;$display("din=%b, sel=%b, dout=%b", din, sel, dout);$stop;end

endmodule

仿真结果:每组 din 中只有一位为高,sel 对应该位,dout 均为 1(高电平),其余情况为 0(低电平)。

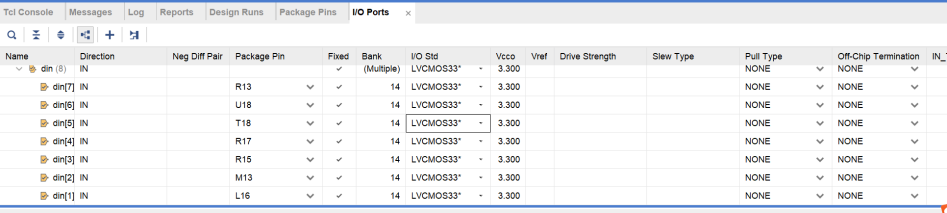

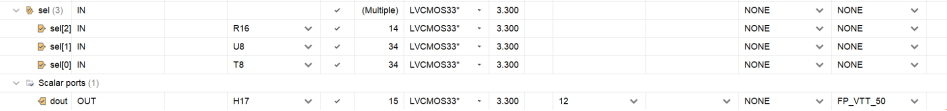

XDC文件配置

# 信号与开发板引脚映射示例(请根据实际开发板调整)

set_property PACKAGE_PIN A1 [get_ports {din[0]}]

set_property PACKAGE_PIN B1 [get_ports {din[1]}]

set_property PACKAGE_PIN C1 [get_ports {din[2]}]

set_property PACKAGE_PIN D1 [get_ports {din[3]}]

set_property PACKAGE_PIN E1 [get_ports {din[4]}]

set_property PACKAGE_PIN F1 [get_ports {din[5]}]

set_property PACKAGE_PIN G1 [get_ports {din[6]}]

set_property PACKAGE_PIN H1 [get_ports {din[7]}]

set_property PACKAGE_PIN J1 [get_ports {sel[0]}]

set_property PACKAGE_PIN K1 [get_ports {sel[1]}]

set_property PACKAGE_PIN L1 [get_ports {sel[2]}]

set_property PACKAGE_PIN M1 [get_ports dout]

set_property IOSTANDARD LVCMOS33 [get_ports {din[*]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sel[*]}]

set_property IOSTANDARD LVCMOS33 [get_ports dout]

注意:实际引脚编号请参照Nexys4开发板用户手册设置,与实际硬件接口一一对应。

注:需要对应开发板上的接口

下板测试

-

测试方法:分别将din的8位输入设置为00000001~10000000,各自对应sel从000到111,观察dout端口电平状态。

-

预期结果:每种情况下,sel选择的那一位din为高,dout输出为高电平,其余为低。

-

测试举例:

- din = 00000001, sel = 000, dout = 高

- din = 00000010, sel = 001, dout = 高

- din = 00000100, sel = 010, dout = 高

- din = 00001000, sel = 011, dout = 高

- din = 00010000, sel = 100, dout = 高

- din = 00100000, sel = 101, dout = 高

- din = 01000000, sel = 110, dout = 高

- din = 10000000, sel = 111, dout = 高

实验体会

- 第一次使用FPGA开发实验,虽然结果很简单,但过程很艰难。需要把理论学习到的原理真正用到开发中,有时确实是反应不过来,不过熟能生巧,下次一定会更好。

- 需要多使用Verilog语言,熟悉其语法,和C语言类似。

- 真正学会了使用Vivado进行FPGA开发实验的流程,跟着老师一步一步来,多想多记忆,同时也需要自己课后多学习。

- 实验的第一步一定是搞清楚原理再写代码。心里要有一个框架,做实验的时候才能得心应手。