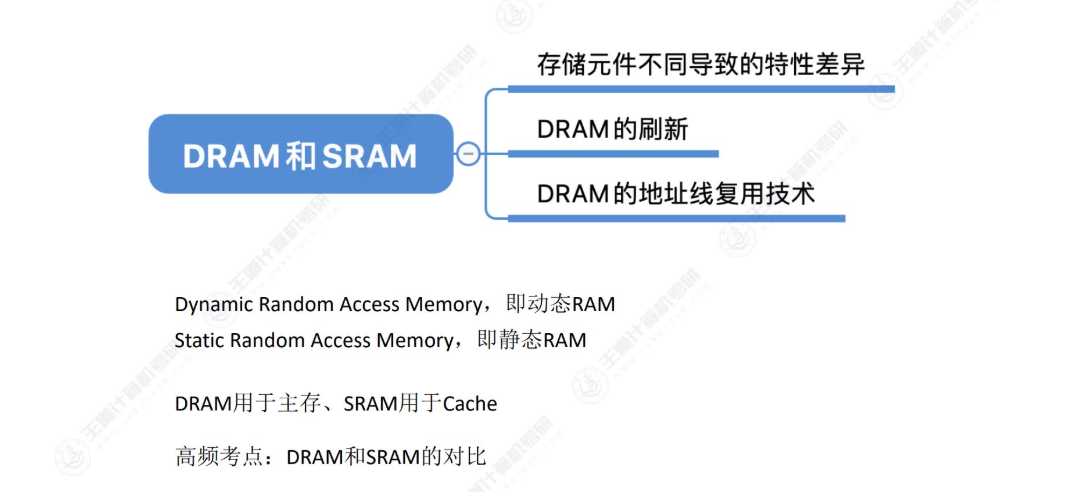

【408计组】3.3 SRAM和DRAM

一,知识脉络

知识思维导图

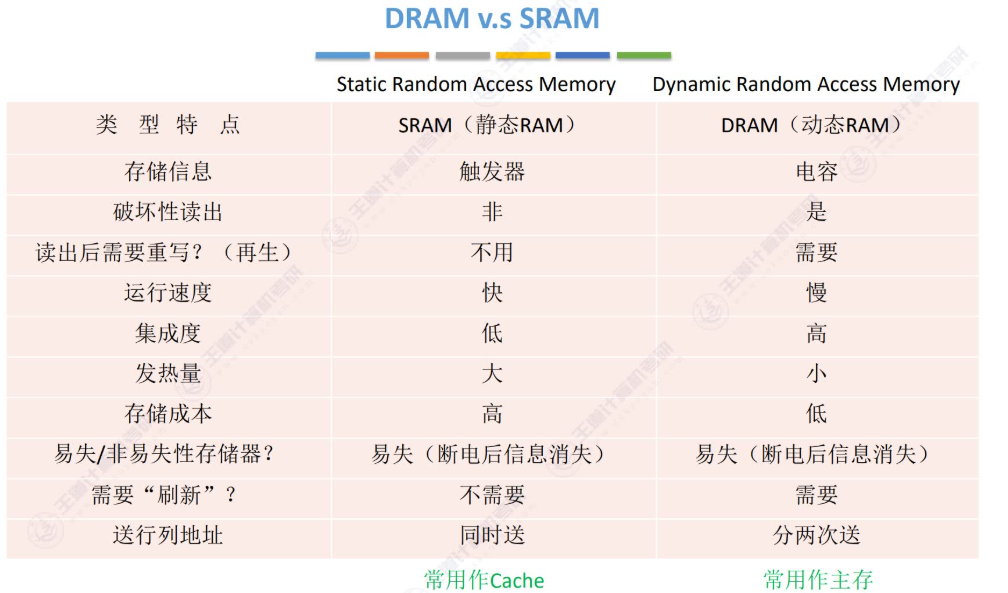

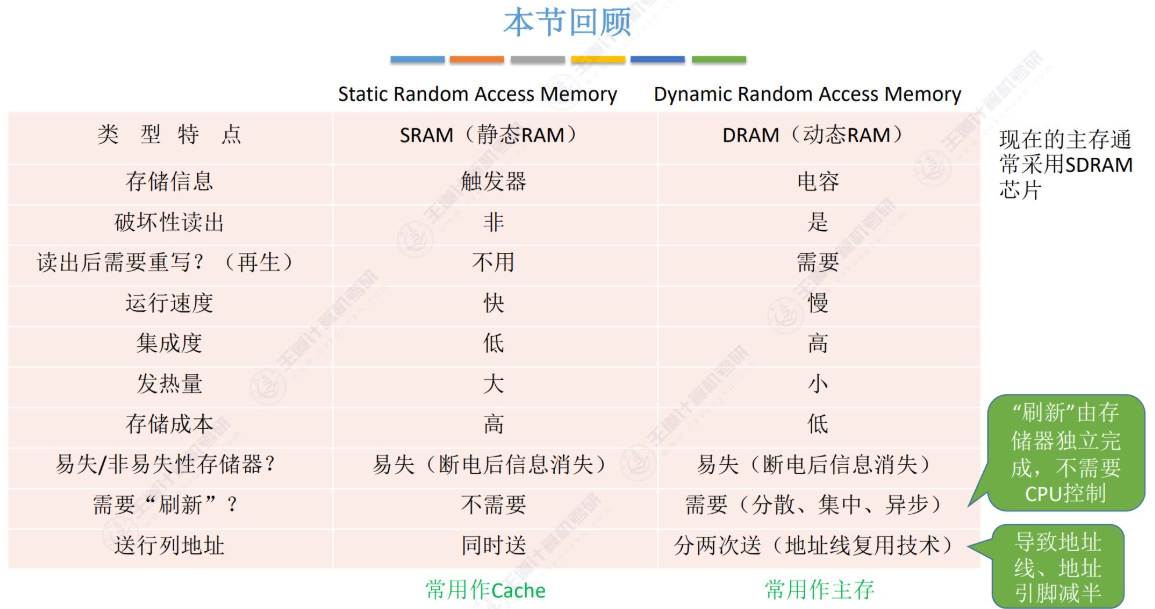

1. DRAM和SRAM是两个不同的寄存器,这里需要重点关注的是两个寄存器的差异和功能与性能和成本的优点,什么场景下选择DRAM存储元件,什么场景下选择SRAM存储元件

2. DRAM是需要刷新的,电路如何给DRAM刷新,为什么需要刷新都是需要去理解的

3. DRAM的优化是改变了哪里?

二,DRAM和SRAM芯片的对比

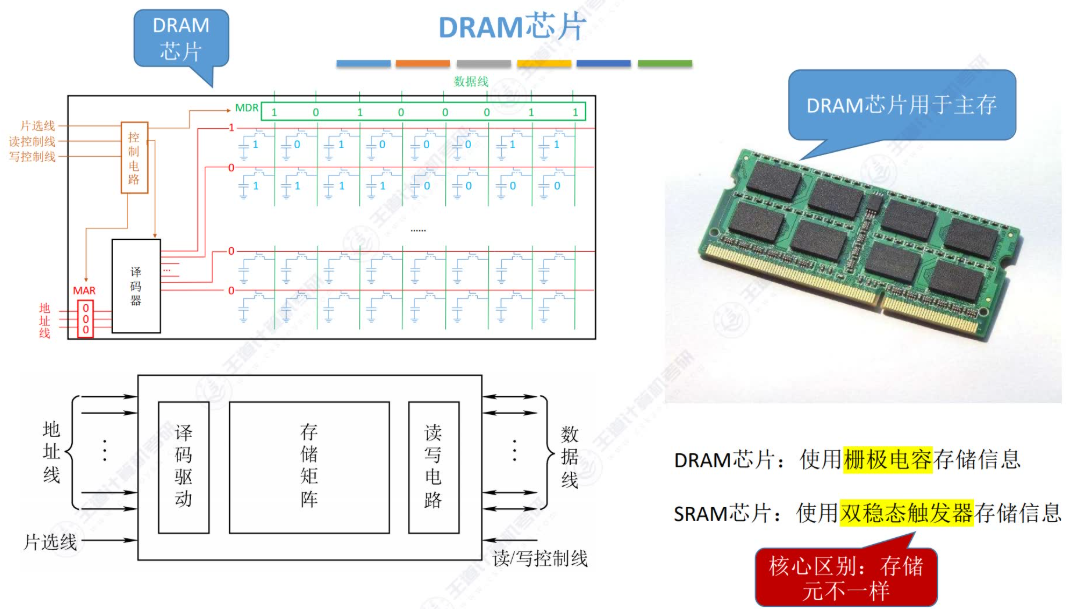

(1) DRAM和SRAM芯片的区别

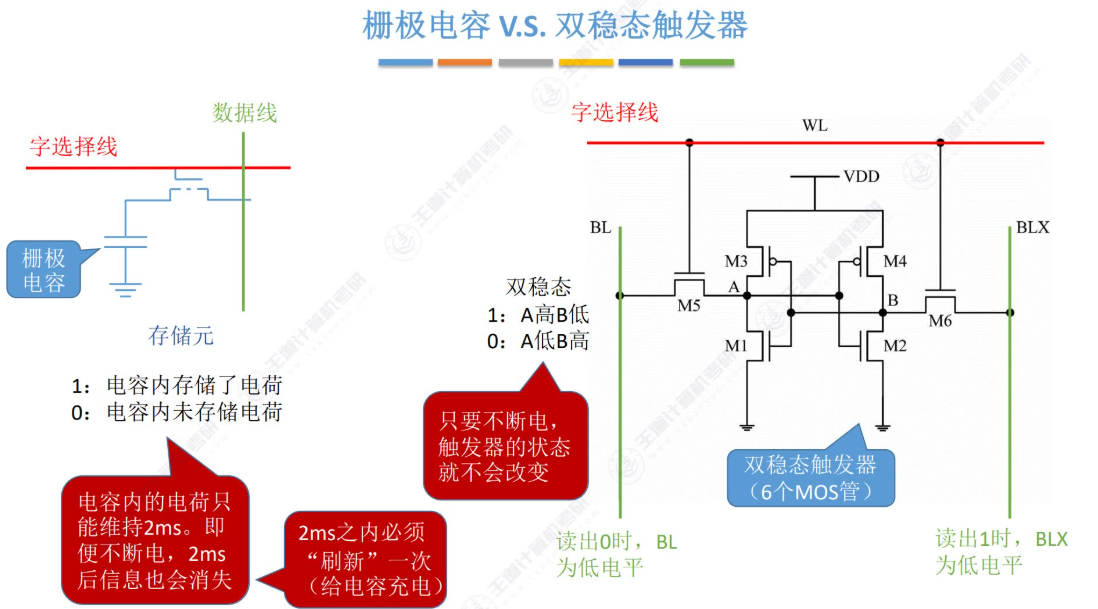

前面学习过一个主存储器的电路,这个电路就是对应着这个DRAM芯片的电路,这里主要是由电容来存储0和1两个数据,然后SRAM不是通过电容来存储0和1两个数据,是通过双稳态触发器来存储信息,这个核心区别就是两个存储元不一样

(2) 两个存储元的区别之处

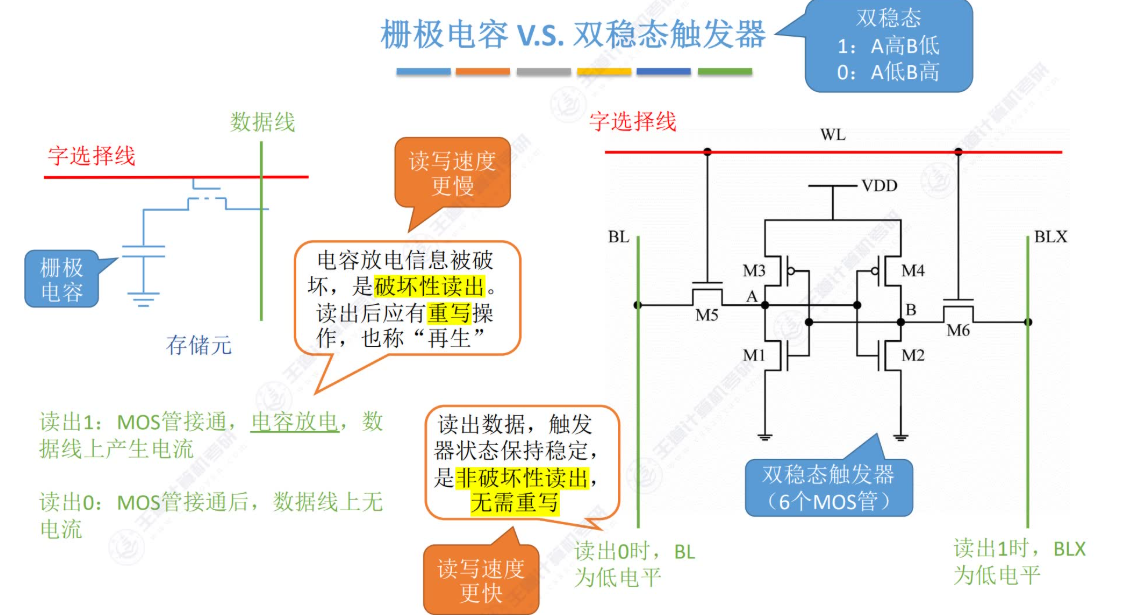

1. 存储元之间的读写区别

(1) 栅极电容

该电容表示的是0和1之间的数据处理,读入和写数据都是通过电容的状态改变来进行读写的,在3.1也有讲解过

但是电容的电信号具有破坏性读出,因为电容放完电就没电了在里面,所以是有破坏性读出,所以这里需要重生,就是再次写入,然后由于电容原本放在那里也会有放电的效果,所以电量也会慢慢地流失,所以这个时候数据也会存在误差,所以在这里就需要进行刷新

(2) 双稳态触发器

双稳态触发器就是说,当我们B为低电压的时候,BLX不动,此时就是写入0,反之则为1,写入操作就是当BL为高电平,BLX为低电平的时候,测试写入为0,反之则为12. 两者的制造成本

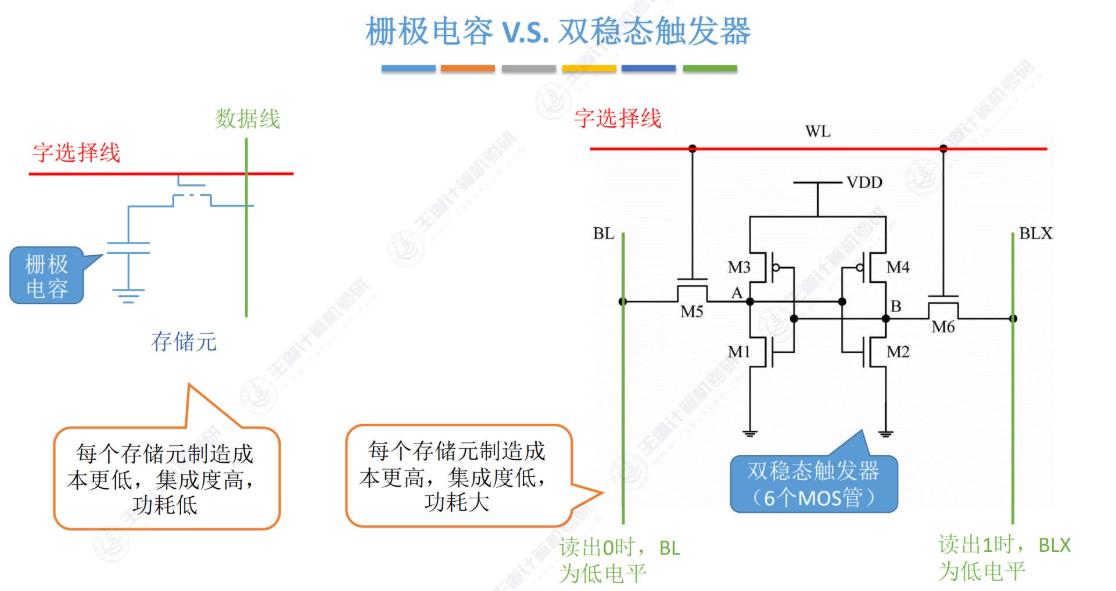

由于栅极电容只需要一个MOS管并且电路大,所以可以集成多,但是双稳态触发器的MOS管多并且电路大,所以对应的集成就很难集成并且功耗大,但是唯一的有点就是时间花销小,因为不需要进行再次写入和刷新时间的开销

3. 两者需刷新和不需刷新的供电

栅极电容里面的电荷只可以维持2ms,所以在2ms之内必须进行刷新,但是双稳态触发器是只需要不断地在VDD提供电压就不会改变

4. 两者的区别大致图

三,DRAM的优化电路变化

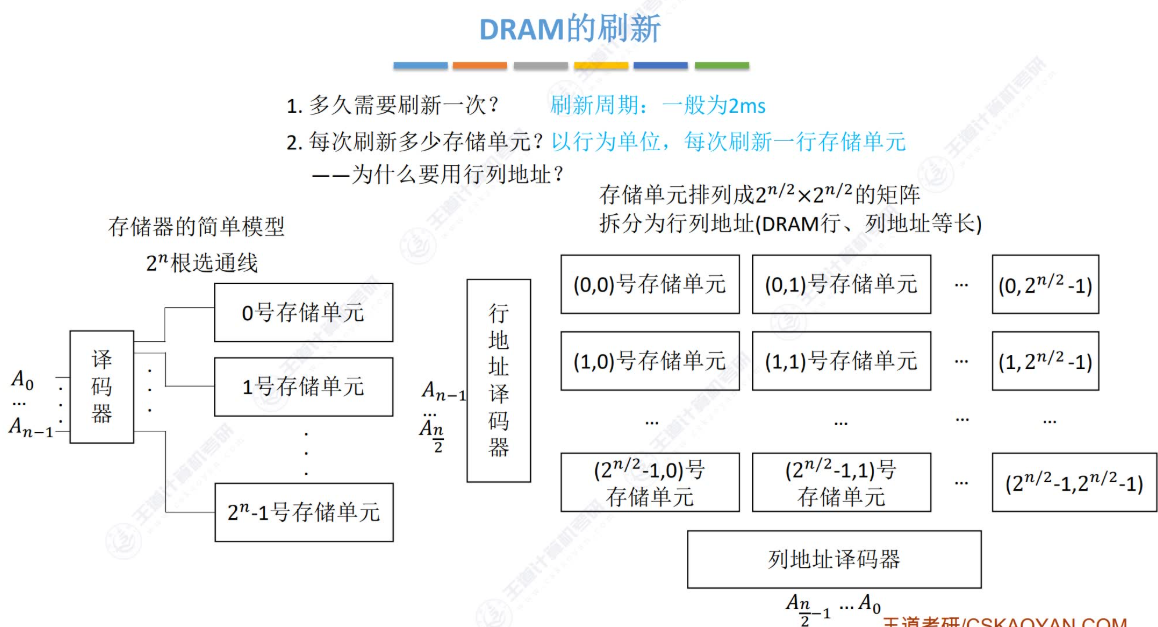

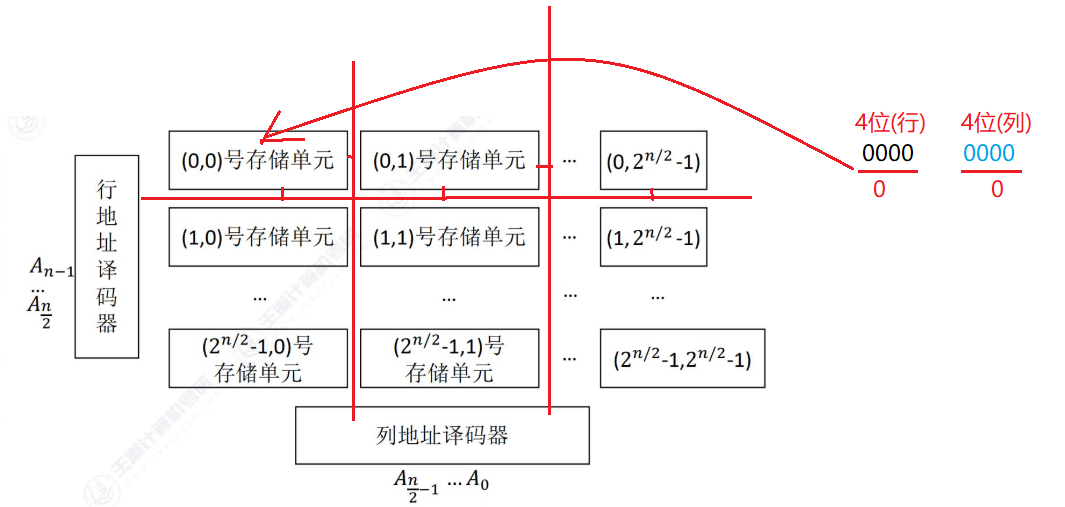

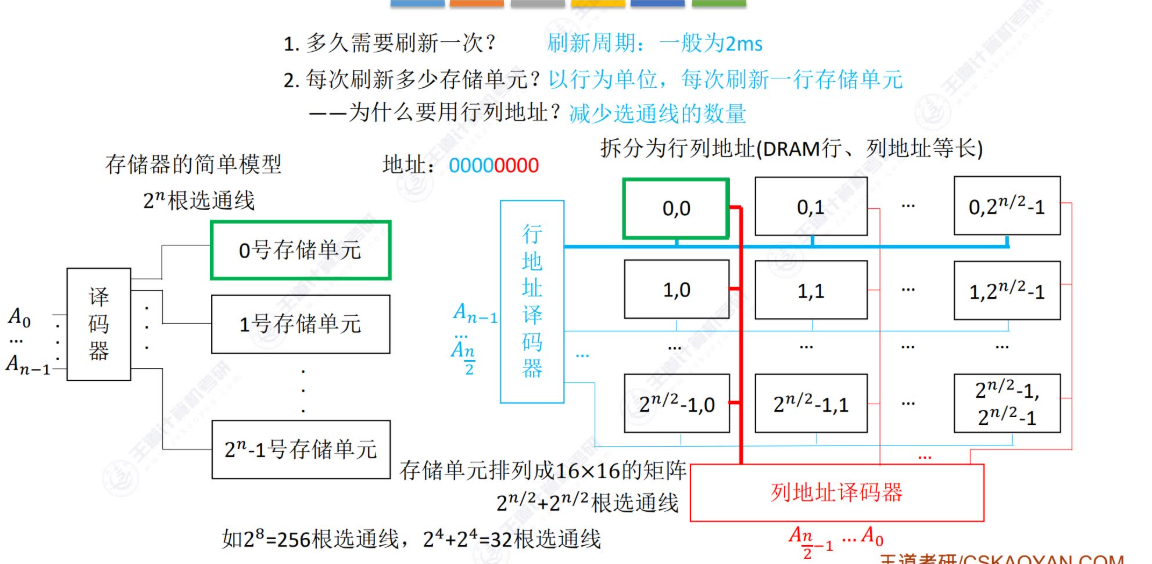

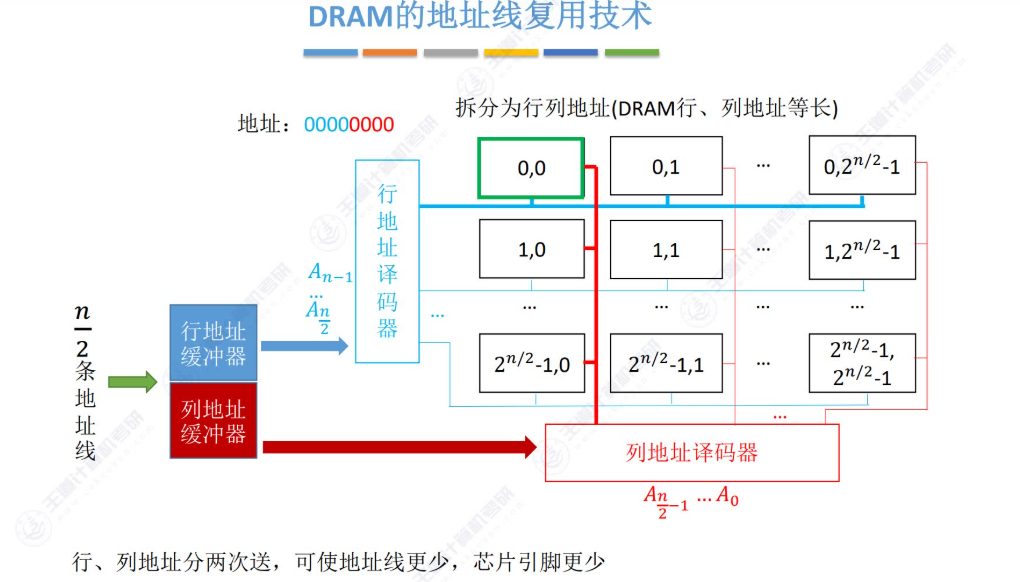

知晓了栅极电容的必须在2ms里面进行一次刷新,在此之前需要优化一下这个存储器的模型,因为当直接按照列的话,那么就会导致,译码器的右边会有大量的选通线,这个时候特别难集成,这个时候,假设为8位一个存储单元,这个时候我们将8位,此时把8位切成两半,就是分为四位四位,分别设置为行来操作四位,列来操作四位,此时就会降这个2^n次幂的n值,此时就会减少这个一个译码器旁边的选通线,如下图所示,8位将为两个四位,这个时候就可以减少一个译码器的选通线了

此时通过标准绘画出图就如上如所示,结果的计算也就是通过降级,减少选通线的产生,更好的集成这个电路

四 DRAM的刷新

通过上述的电路变化,首先减少了译码器与选通线的之间集成的难度,第二个就是可以更好的进行刷新存储单元,因为可以细分化时间,更好地掌握这个刷新时间

这里有三个刷新的机制

1. 每次读写都进行一次刷新

系统进行一次读写为0.5us,刷新的时间为0.5us,此时此刻不难算出刷新的次数相当多,因为2ms/1us = 2000次,2000次足够刷新128行的数据了,所以是相当多次刷新,时间浪费太多了2. 2ms集中安排刷新

就是集中一个时间点进行刷新,那么就会有一个长时间是不可以访问内存的,因为这个时候在进行刷新,所以这个方案不妥,因为有很长时间为死时间3. 2ms需要128次刷新

那么就是15.6us进行一次刷新,那么就可以把这个时间放到译码阶段去执行刷新

五,不同芯片的对比