浅谈内存DDR——DDR4的RASR/Bank Group等技术

在DDR3及更早的内存中,虽然一个内存芯片内部也划分了多个Bank(可以理解为独立的内存子阵列),可以在不同Bank之间进行流水线操作,但同一时刻只能有一个Bank在进行数据读写。当控制器要访问一个Bank时,必须经历一系列的命令(激活、读写、预充电),在此期间,其他已经准备好的Bank也必须等待,这形成了性能瓶颈。

Bank Group

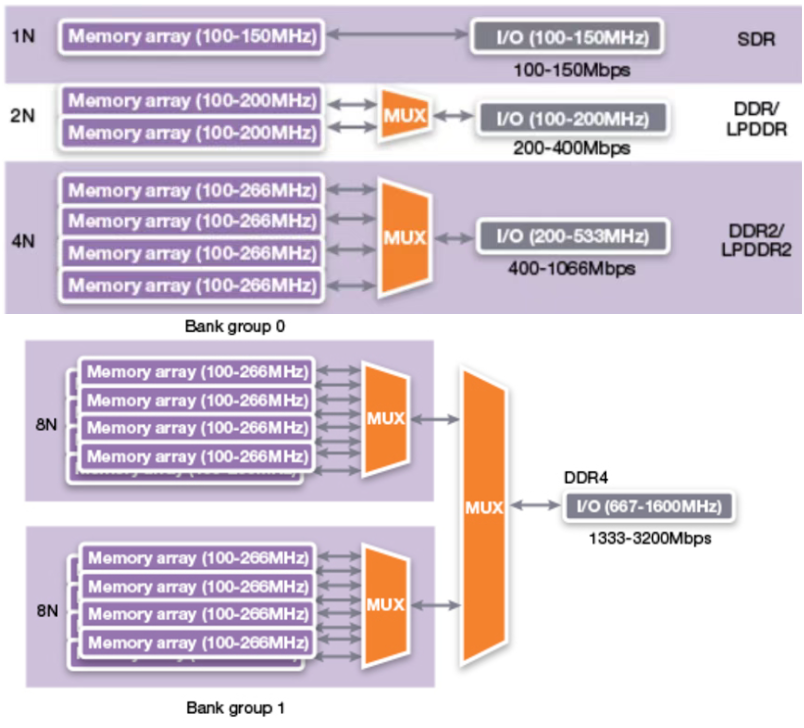

DDR(Double Data Rate)内存技术中的预取(Prefetch)机制是提高数据传输效率和减少内存访问延迟的关键技术之一。预取机制通过在一次内存访问中读取多个数据位,并将这些数据暂存到缓冲区中,以便后续的快速访问。 预取位数随着DDR技术的演进而不断增加,从DDR1的2位预取到DDR5的16位预取。

以下是各个DDR版本的预取位数:

DDR1:2位预取(2n Prefetch) DDR2:4位预取(4n Prefetch)

DDR3:8位预取(8n Prefetch) DDR4:8位预取(8n Prefetch)

DDR5:16位预取(16n Prefetch)

按照发展趋势,其实DDR4的预取应该为16位预取,但是DDR4并没有增加到16位预取。DDR4不使用16倍预取的原因主要有以下几点:

与CPU Cache Line大小不匹配:16倍预取会导致数据浪费,降低带宽利用率。现代CPU的Cache Line大小通常是64字节(64B)。如果DDR4使用16倍预取,对于64位(8字节)的DDR,一次会取出128字节的数据。而CPU的Cache Line大小是64字节,这意味着多取出来的64字节数据可能会被浪费,因为这些数据可能不会立即被使用。

增加DRAM内部面积资源:16倍预取需要更大的内部缓冲区,增加芯片面积和制造成本。

平衡性能和功耗:8倍预取在满足高带宽需求的同时,避免了不必要的数据传输,降低了功耗。

所以,这是当时情况下的最优解。同时为了提高速度,DDR4引入了Bank Group这个技术。

两个时序参数

Bank Group的设计使得在同一时间可以并行处理多个读写操作,从而提高了内存系统的整体性能。

DDR4将多个Bank分组形成一个Bank Group,每个Bank Group可以包含多个Bank。通过Bank Group,DDR4内存可以在不同的Bank Group之间同时执行命令,而不会相互干扰。这意味着,当一个Bank Group正在进行数据传输时,另一个Bank Group可以同时进行其他操作,从而提高了内存的整体性能。 通过多个BG再进行MUX,这样多级MUX结构,2个BG就能够实现等效16N预取的效果。 在DDR4中,Bank Group的引入使得设计者能够在不增加预取长度的情况下,提升内存的带宽和效率。通过将Bank分组,设计者可以更灵活地管理内存的访问,避免了因增加预取长度而带来的复杂性和潜在的性能瓶颈。

DDR4增加Bank Group后,引入了tCCD_S和tCCD_L(CCD:Column to Column Delay)两个时序参数。

tCCD_S(Short Column to Column Delay)

定义:tCCD_S表示不同Bank Group之间的列访问等待时间。其值通常是4个时钟周期(Cycle),与一个数据Burst长度相同。作用是允许不同Bank Group之间的快速切换,提高并发操作能力。

tCCD_L(Long Column to Column Delay)

定义:tCCD_L表示同一个Bank Group内部的列访问等待时间。其值通常比4个时钟周期长,即会超过一个数据Burst长度。作用是确保在同一Bank Group内部进行连续列访问时,有足够的等待时间来避免冲突和数据错误。

Bank Group核心思想

Bank Group的核心思想是缩短同一Group内Bank间的命令延迟,但允许不同Group之间以更短的延迟进行切换

• 同一Bank Group内的操作:当在一个Bank Group内切换Bank时,仍然需要遵守类似于DDR3的时序限制(如 tCCD_L, 列到列延迟),这个延迟较长。

• 不同Bank Group间的操作:当从一个Bank Group切换到另一个完全不同的Bank Group时,可以应用一个更短的延迟(如 tCCD_S)。这相当于为内存控制器打开了多条“高速公路”,可以在一条路上有车(命令)时,另一条路上也同时发车。

把DDR3的内存看作一个只有一个出入口的大型停车场。无论车停在哪个车位,进出都要经过这个口,容易堵车。

而DDR4的内存则像一个有多个独立出入口的四层停车场。车辆可以同时从不同层的出入口进出,大大提升了通行效率。

• 更高的数据速率:通过交叠来自不同Bank Group的访问请求,有效提升了数据总线的利用率,使得DDR4能够稳定运行在远高于DDR3的频率

(如 2133MT/s 起,最高可达 3200MT/s+)。

• 降低实际延迟:虽然绝对延迟(如CAS Latency)的数值可能没有下降,但由于并发性的提高,系统的整体感知延迟降低了,因为多个请求可以被并行处理。

RASR - 可靠性、可用性与可服务性

RASR并不是一个单一的技术,而是一系列旨在提高内存子系统 可靠性、可用性和可服务性 的功能集合(刷新管理)。在DDR4中,这些功能变得更加重要,因为更高的密度和更低的电压使得内存对错误更加敏感。

在自刷新模式下,DRAM需要定期刷新其存储单元以防止数据丢失。传统的自刷新模式下,刷新周期是固定的,这会导致不必要的功耗,尤其是在低功耗应用场景中。为了优化功耗,DDR4引入了Reduced Auto Self-Refresh (RASR) 技术。 RASR技术通过减少刷新周期的数量来降低功耗,同时确保数据的完整性。其核心原理在于动态调整刷新周期的数量,以适应不同的工作状态和温度条件。

• 减少刷新周期:在RASR模式下,DDR4 SDRAM会根据当前的工作状态和温度动态减少刷新周期的数量。这意味着在某些情况下,DRAM可以使用更长的刷新间隔,从而减少刷新操作的频率。

• 优化算法:DDR4 SDRAM内部使用优化算法来决定何时减少刷新周期的数量。这些算法考虑了当前的温度、工作负载和其他相关因素,以确保在减少刷新周期的同时,数据的完整性不受影响。

• 温度监测:DDR4 SDRAM内部集成了温度传感器,可以实时监测当前的温度。温度信息用于调整刷新周期的数量,确保在高温条件下仍然能够保持数据的完整性。

片上ECC

在一些高端的DDR4内存芯片(通常是服务器级)中,在每个芯片内部 就集成了错误纠正码逻辑。

它在数据被写入芯片的存储单元时生成ECC校验位,并在读取时进行校验和纠正。这与主板/CPU层面实现的ECC(在内存条上有多余的颗粒)是不同的层级。

可以纠正芯片内部产生的个别位错误,防止这些错误传递到系统总线上,从而提高了芯片本身的可靠性。这对于构建极高可靠性的服务器系统至关重要。

数据的ECC,ECC(Error Correction Code)。它通过在数据中添加冗余信息(ECC码),可以检测并纠正一定数量的错误比特。但是这个是需要额外的存储空间才能实现的,一般在车载,服务器领域才会使用。

命令/地址奇偶校验

DDR4为从内存控制器发送到内存颗粒的命令和地址信号 增加了奇偶校验功能。

内存控制器在发送命令/地址的同时会计算并发送一个奇偶校验位。内存颗粒在接收端会重新计算奇偶校验,如果发现不匹配,会通过一个专门的 ALERT_n 信号线通知控制器。

防止因命令或地址信号在传输过程中出错而导致的错误内存操作(如写入错误的位置),提升了系统的稳定性。

奇偶校验是一种简单的错误检测机制,它通过在数据中添加一个额外的位(奇校验或偶校验位)来确保数据中1的总数是奇数或偶数。在DDR4中,奇偶校验可以通过模式寄存器启用。启用后,DRAM会使用ACT_n,RAS_n/A16,CAS_n/A15,WE_n/A14,BG0-BG1,BA0-BA1,A17-A0计算奇偶校验。输入奇偶校验应保持在时钟的上升沿,并同时与CS_n LOW的命令和地址保持一致。如果命令地址奇偶校验中存在错误,则Alert_n会在相当长的一段时间内变为低电平。

数据总线CRC

DDR4为数据总线 引入了循环冗余校验。

在突发传输(Burst)期间,内存控制器会计算并附加一个CRC校验码。内存颗粒在接收数据时会进行CRC校验。如果发现错误,颗粒可以通知控制器,控制器可以重新发送数据。

保护了在数据总线上传输的数据完整性,特别是在高频率下,信号完整性面临挑战时,CRC能有效检测并帮助纠正传输错误。

CRC校验是一种广泛使用的错误检测技术,它通过计算数据包的CRC值来检测在传输过程中数据是否被篡改或损坏。在DDR4中,CRC校验可以通过模式寄存器开启,并在写操作时进行校验操作。当CRC校验开启时,数据结构格式为固定10个UI,同时对BL8与BC4有效。如果在写操作时启用了CRC,DRAM会在数据突发末尾添加CRC。

可编程的刷新功能

这是DDR4 RASR中一个非常重要且灵活的特性,主要包括:

自动自刷新

内存可以根据其内部温度传感器,动态调整自刷新的频率。

内存颗粒内部集成温度传感器。当温度升高时,DRAM单元漏电加快,需要更频繁地刷新;温度降低时,则可以降低刷新频率。

在低温下减少不必要的刷新操作,可以显著降低功耗(称为“自刷新功耗”),这对于需要始终通电的移动设备和服务器来说意义重大。

精细粒度刷新

提供了多种刷新模式,允许系统在性能和可靠性之间进行权衡。

1x Refresh:标准刷新模式,每隔 tREFI 时间进行一次刷新。

2x Refresh:将刷新命令的频率提高一倍。这通常在内存温度很高时使用,以确保数据不会因漏电而丢失,但会稍微影响性能(因为刷新更频繁地占用总线)。

5x/4x Refresh:一些厂商支持更极端的模式,如降低刷新频率以在低温下节能,或极度提高频率以应对极端高温。

赋予了系统设计者根据实际工作环境(如温度)来优化内存子系统的能力。

Bank Group和增强的RASR功能是DDR4技术的两大支柱。Bank Group主要负责“开得快”,通过架构革新解决了高频率下的并发瓶颈;而RASR主要负责“开得稳”,通过一系列纠错、校验和智能管理功能,确保了在高速、高密度、低电压下的数据可靠性和系统耐久性。这两者结合,使得DDR4能够满足从移动设备到高性能计算、数据中心等广泛领域对内存性能、功耗和可靠性的苛刻要求。