I2C总线详解

一、概述

I2C(Inter-Integrated Circuit)总线是由飞利浦半导体(现恩智浦NXP)在1980年代开发的一种双向、二线制、同步串行通信总线。它设计初衷是提供一种简单、高效的方式,让主板、嵌入式系统或物联网设备上的微控制器(CPU)能够与周边设备芯片进行通信。由于其硬件连接简单,引脚占用少,在各类传感器、EEPROM、RTC(实时时钟)等设备中得到了广泛应用。

二、物理特性与硬件连接

两线制:

SDA:串行数据线,用于双向数据传输。

SCL:串行时钟线,由主设备产生,用于同步数据位传输的节奏。

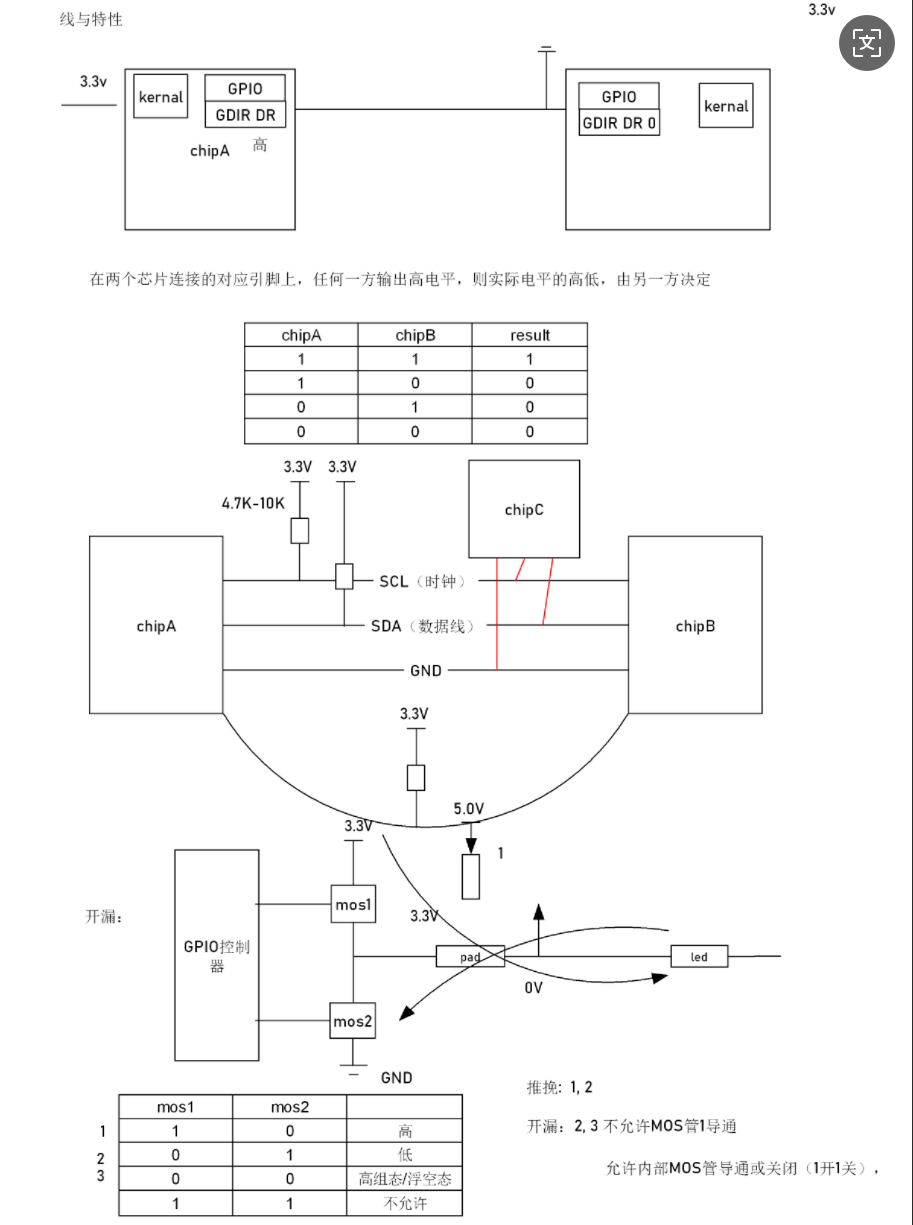

线与特性:

这是I2C总线能够实现多主多从通信的基石。

硬件基础:SDA和SCL线都通过上拉电阻连接到正电源VCC。总线上的所有设备其I/O引脚都是开漏输出或集电极开路输出结构。

工作原理:

当任何一个设备的输出为低电平时,它会将总线通过MOS管或三极管下拉到低电平。由于“线与”逻辑,此时整个总线呈现为低电平。

只有当所有设备都输出高电平(即释放总线,呈高阻态)时,上拉电阻才会将总线拉至高电平。

核心优势:

电平冲突检测:如果一台设备试图输出高电平,而另一台正在输出低电平,结果总线是低电平。这使主设备能够通过读取总线电平与自己输出的电平进行比较,从而判断是否发生了总线仲裁,这对于支持多主模式至关重要。

无需担心电源时序:不同设备的逻辑电平可以不同,只要其开漏输出能够承受VCC电压即可。

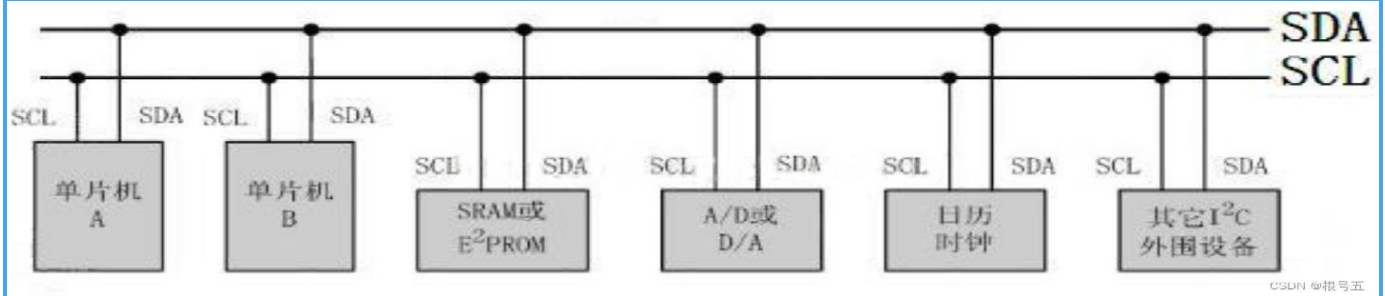

支持多设备连接:

总线采用主从式通信架构。

主设备:负责发起和终止一次数据传输,并产生时钟信号SCL。通常是微控制器、CPU或DSP。

从设备:响应主设备的寻址和命令,被动地接收或发送数据。例如传感器、存储器等。

总线上可以连接多个主设备(支持多主竞争仲裁)和多个从设备。

三、通信协议与寻址机制

通信的发起与终止:

起始条件(起始信号):在SCL为高电平时,SDA线出现一个从高到低(下降沿)的跳变。这表示一次通信的开始,并唤醒所有从设备准备接收地址。

停止条件(停止信号):在SCL为高电平时,SDA线出现一个从低到高(上升沿)的跳变。这表示本次通信的结束,释放总线,总线恢复空闲状态(高电平)。

设备寻址与数据流向:

唯一地址:总线上每个从设备都必须有一个7位的唯一设备地址(部分I2C设备支持10位地址扩展)。

地址帧结构:主设备发送起始条件后,紧接着发送的第一个字节就是地址字节。

高7位:从设备地址。

最低位:(之后的数据流向)读写控制位。

0:表示主设备接下来要向从设备写入数据(主发从收)。

1:表示主设备接下来要从从设备读取数据(从发主收)。

举例:一个从设备地址为

0x48(二进制0100 1000)。主设备要写数据时,发送的地址字节为:

0x48 << 1 | 0=0x90(二进制1001 0000)。主设备要读数据时,发送的地址字节为:

0x48 << 1 | 1=0x91(二进制1001 0001)。

应答机制:

每个字节(包括地址字节和每一个数据字节)传输完成后,接收方必须发送一个应答位。ACK:第9个时钟周期,SDA被拉低(低电平),表示接收成功。

NACK:第9个时钟周期,SDA保持高电平,表示:

接收失败。

主设备作为接收方时,发送NACK来告知从设备“这是最后一个字节,不要再发了”。

3.数据传输规则:

1.I2C 以字节(8 位)为单位传输数据,且高位(MSB)先传输。

2.在传输过程中,在时钟线(SCL)为低电平时,只允许发送方改变数据线(SDA).接收方不得采样。

3. 在传输过程中,在时钟线(SCL)为高电平时,只允许接收方采样数据线(SDA).发送方需要保持SDA的稳定

四、典型操作时序详解

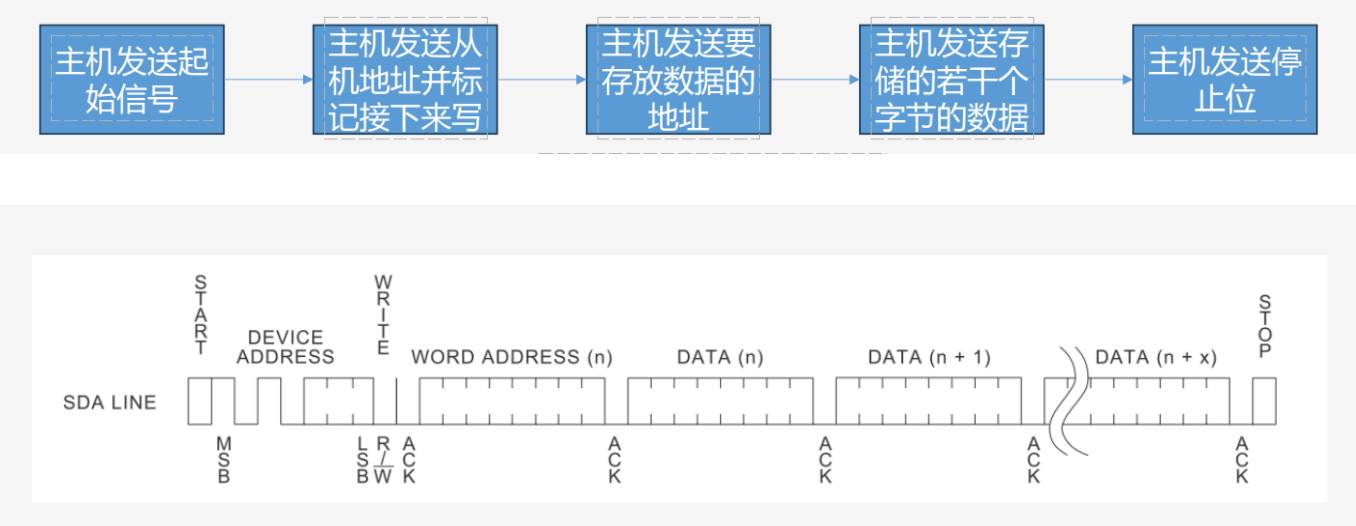

1. 写操作时序

这种操作常用于向EEPROM等存储设备写入数据,或向配置寄存器写入命令。

步骤:

主机发送起始信号。

主机发送从机地址 + 写位(之后的数据流向,主发从收)。

从机回复ACK。

主机发送要写入的内存地址。

从机回复ACK。

主机开始逐字节发送一个或多个数据字节。每发送一个字节,从机回复一个ACK。

主机发送停止信号,结束本次通信。

时序图示意:

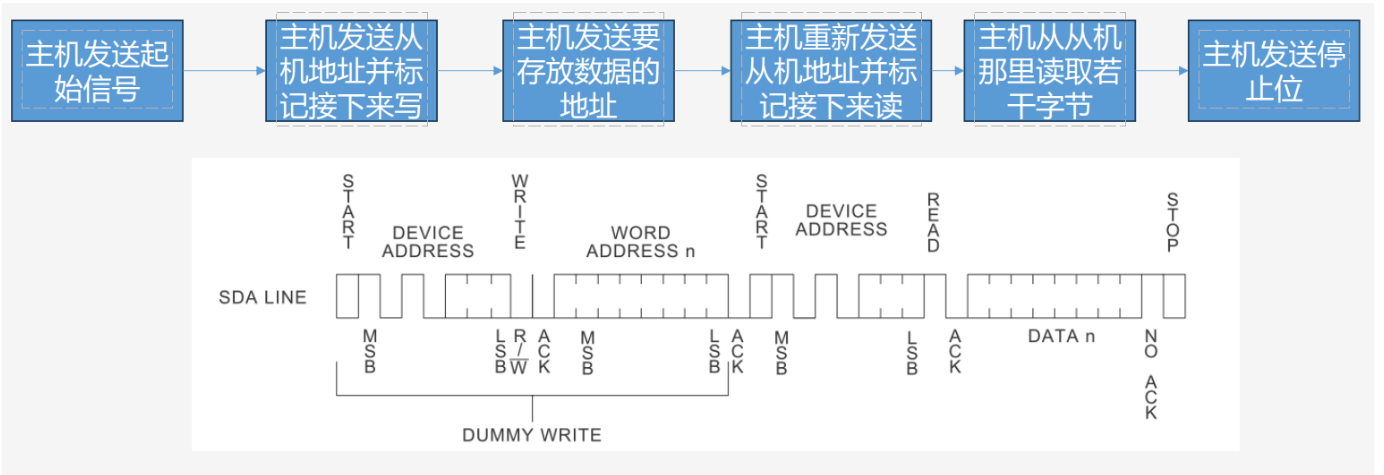

2. 读操作时序

读操作相对复杂,主设备需要先告诉从设备要读取哪个地址的数据。有两种常见方式,重点介绍效率更高的“复合格式”读操作。

高效读操作(复合格式):

主机发送起始信号。

主机发送从机地址 + 写位(之后的数据流向,主发从收)。 //此次是为了告诉从设备要读取哪个地址的数据,一般被叫做“哑写”

从机回复ACK。

主机发送要读取的内存地址。 // 主机此时是在“写”地址指针

从机回复ACK。

主机不发送停止信号,而是再次发送一个起始信号。 // 关键步骤:重启

主机发送从机地址 + 读位(改变之后的数据流向,从发主收)。

从机回复ACK。

从机开始逐字节发送一个或多个数据字节。每接收一个字节,主机回复一个ACK,但对于最后一个字节,主机必须回复NACK。

主机发送停止信号,结束通信。

关键点:

为何高效:在一次通信过程中完成了“设置地址指针”和“读取数据”两个动作,无需两次完整的通信周期。

最后一个字节的NACK:这是至关重要的。它向从设备表明主设备不再请求更多数据,从设备在收到NACK后会释放SDA线。如果不发送NACK,从设备可能会继续尝试发送下一个字节,导致通信时序错乱。

时序图示意:

五、总结

| 特性 | 描述 |

|---|---|

| 总线结构 | 二线制(SDA, SCL),开漏输出,需上拉电阻,具有“线与”特性。 |

| 通信模式 | 同步、串行、半双工、主从式。 |

| 寻址方式 | 7位或10位从设备地址,首个字节包含读写方向位。 |

| 关键信号 | 起始条件、停止条件、应答位、重复起始条件。 |

| 操作模式 | 支持标准模式、快速模式、高速模式等,速率从100kbps到5Mbps不等。 |

| 应用优势 | 硬件简单,引脚节省,支持多主多从,有成熟的软件库和硬件支持。 |