玳瑁的嵌入式日记---0925(ARM--时钟)

一、核心概念定义

1. 定时器(EPIT/GPT)

定时器是一种通过对已知频率的时钟信号进行计数,实现定时、延时或事件计数功能的硬件模块或软件机制。在嵌入式系统中,主要以硬件定时器模块形式存在,如 EPIT、GPT 等,是实现精准时序控制的核心组件。

2. 时钟(Clock)

在电子系统中,时钟是产生稳定、周期性振荡信号的电路或组件。其作用类似 “节拍器” 或 “心跳”,为数字电路(如 CPU、定时器、外设)的所有操作提供同步时序基准,确保各模块按统一节奏协同工作。

3. 实时时钟(RTC, Real Time Clock)

RTC 是微处理器中的专用功能模块,核心特点是在系统主电源关闭时,可通过备用电源(如纽扣电池)继续工作,从而持续提供精确的日历(年 / 月 / 日)和时间(时 / 分 / 秒)信息,常用于记录事件发生时间、唤醒休眠系统等场景。

二、硬件基础:时钟与分频相关组件

1. 时钟源:晶体振荡器

- 核心作用:为整个系统提供最原始、最稳定的时钟信号,是所有时序的 “源头”。

- 工作原理:将石英晶体切割成特定形状(如音叉形),对其施加交变电压后,晶体会因 “压电效应” 产生稳定的机械振荡,进而转化为电信号输出,频率精度远高于普通 RC 振荡电路。

2. PLL(Phase Locked Loop,锁相环电路)

- 核心功能:倍频(将输入时钟频率放大)。

- 作用场景:当晶体振荡器输出频率较低(如 12MHz),无法满足 CPU 或高速外设(如 USB、以太网)的高频需求时,通过 PLL 将基础频率倍频至目标频率(如 72MHz、1GHz),为系统提供高速时钟。

3. Prescale(分频器)

- 核心功能:分频(将输入时钟频率降低)。

- 作用场景:高速时钟(如 CPU 核心时钟)直接供给低速外设(如定时器、UART)时,会导致外设计数过快、功耗过高。通过分频器按固定比例(如 1/2、1/4、1/16)降低频率,得到外设所需的低速时钟。

4. PFD(Phase Fractional Prescale,相位分数分频器)

- 核心功能:灵活调节频率,输出频率可升可降(区别于普通分频器仅能降频),且支持非整数倍的频率调节(如将 10MHz 调节为 12.5MHz)。

- 优势:相比整数分频器,能提供更精细的频率梯度,满足不同外设对时钟精度的差异化需求。

三、经典单片机 / 处理器定时器工作原理

1. 51 单片机定时器

51 单片机定时器核心为8 位 / 16 位计数器,工作依赖系统时钟分频后的信号,核心特点如下:

- 8 位定时器(如 T0/T1 模式 0/2):支持自动重装。初始化时设置 “计数初值”,计数器从初值开始累加,当计数到最大值(0xFF)时,自动将初值重新载入计数器,无需在中断服务程序中手动赋值,适合产生固定频率的脉冲或定时。

- 16 位定时器(如 T0/T1 模式 1):需在中断服务程序中手动重装初值。16 位计数器最大值为 0xFFFF,计数溢出后会触发中断,需在中断服务函数中重新写入初值,才能继续下一轮定时,适合需要更长定时周期的场景。

2. I.MX6ULL 处理器定时器

I.MX6ULL 作为 ARM 架构处理器,定时器模块更丰富,核心介绍EPIT和GPT两种常用定时器:

(1)EPIT(Enhanced Periodic Interrupt Timer,增强型周期中断定时器)

- 核心定位:专注于周期性中断,适合实现固定间隔的定时任务(如定时采样、LED 闪烁)。

- 工作原理:

- 从系统时钟中选择合适的时钟源(需经过 PLL / 分频器处理);

- 设置 “计数初值”:根据目标定时时间和时钟频率计算初值(公式:初值 = 定时时间 × 时钟频率);

- 计数器从初值开始递减(部分型号为递增),当计数到 0 时,触发中断,并自动重装初值,进入下一轮计数,实现 “周期中断”。

- 典型实验:1s 中断反转 LED 灯假设时钟频率为 1MHz(1000000Hz),1s 定时需计数 1000000 次,因此设置计数初值为 1000000。计数器每减至 0 时触发中断,在中断服务函数中切换 LED 的电平状态(亮→灭 / 灭→亮),即可实现 LED1 秒闪烁。

(2)GPT(General Purpose Timer,通用目的定时器)

- 核心定位:功能更灵活,除定时外,还支持输入捕获和比较输出,适用于复杂时序控制场景。

- 核心功能:

- 输入捕获:检测外部引脚的电平变化(如上升沿、下降沿),并记录当前计数器值,可用于测量脉冲宽度、频率(如测量电机转速、红外信号解码);

- 比较输出:预先设置 “比较值”,当计数器值与比较值相等时,触发指定动作(如输出高低电平、产生脉冲),可用于生成 PWM 波(如电机调速、LED 呼吸灯);

- 自由运行模式:计数器从 0 开始持续递增,溢出后重新从 0 开始,可用于实现精准延时。

- 典型实验:自由运行模式编写精准延时函数

- 配置 GPT 时钟源(如 1MHz),开启自由运行模式;

- 延时函数中,记录延时开始时的计数器值(记为

start_val); - 循环读取当前计数器值(

curr_val),计算差值curr_val - start_val; - 当差值达到 “延时时间 × 时钟频率” 时,退出循环,完成精准延时(如 1ms 延时需差值达到 1000)。

四、关键计算说明(避免混淆)

频率计算:1M = 1000×1000频率单位中,1MHz(兆赫兹)= 1000kHz(千赫兹)= 1000×1000Hz(赫兹),即 1 秒内振荡 1000000 次,常用于定时器初值计算(如 1MHz 时钟下,1ms 需计数 1000 次)。

存储容量计算:1MB = 1024×1024存储单位中,1MByte(兆字节)= 1024KByte(千字节)= 1024×1024Byte(字节),与频率计算的 “1000 进制” 不同,需注意区分,避免计算错误。

1. 什么是 PLL、Prescaler、PFD,它们各自有什么作用?

- PLL(Phase - Locked Loop,锁相环):是一种反馈控制系统,能使输出信号的相位与输入参考信号的相位保持同步(锁定)。作用是将输入的参考时钟信号倍频,产生更高频率且稳定的时钟信号,为系统各模块提供时钟。

- Prescaler(预分频器):是一种分频电路。作用是对输入的时钟信号进行分频,降低时钟频率,以满足不同模块对时钟频率的需求,比如一些低速外设不需要高频时钟,就可以通过预分频器降低时钟频率。

- PFD(Phase - Frequency Detector,鉴频鉴相器):是 PLL 中的关键部件。作用是检测输入参考时钟和 PLL 反馈时钟之间的相位差和频率差,输出相应的误差信号,该误差信号用于后续调整 PLL 输出时钟的相位和频率,使 PLL 实现锁定。

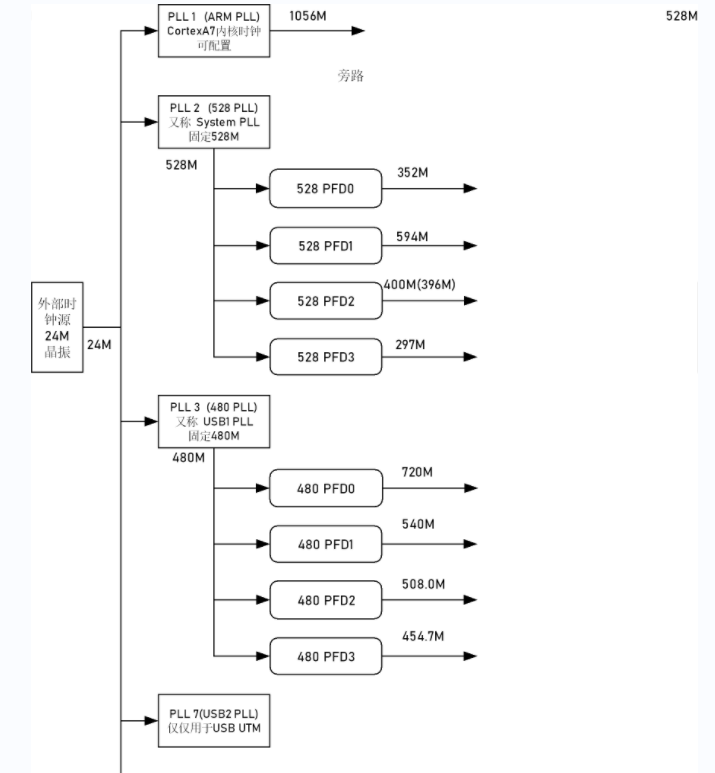

2. IMX6ULL 中有几个 PLL?几个 PFD?

IMX6ULL 中有多个 PLL,常见的有 PLL1(系统 PLL)、PLL2(音频 PLL)、PLL3(USB PLL)、PLL4(视频 PLL)、PLL5(HDMI PLL)等;每个 PLL 通常有多个 PFD(比如 PLL1 有 4 个 PFD),不同的 PLL 所包含的 PFD 数量可能不同

3. 简述 ARM PLL 的配置流程

- 使能 PLL 相关时钟:确保 PLL 模块的电源和时钟使能,使其可以工作。

- 配置参考时钟源:选择 PLL 的输入参考时钟,比如选择外部晶振或者内部时钟源作为输入。

- 配置 PLL 控制寄存器:设置 PLL 的倍频系数、分频系数等参数,通过这些参数来确定 PLL 输出时钟的频率。

- 使能 PLL 并等待锁定:启动 PLL,然后等待 PLL 锁定指示信号,表明 PLL 已经稳定输出所需频率的时钟。

- 配置时钟分发:将 PLL 输出的时钟通过分频、选通等方式分发给系统各个需要时钟的模块,比如 CPU、外设等。

4. IMX6ULL 中的 EPIT 和 GPT 的工作原理是什么?

- EPIT(Enhanced Periodic Interrupt Timer,增强型周期性中断定时器):

- 是一个 32 位的定时器,可工作在自由运行模式或周期性中断模式。

- 工作时,它从设定的初始值开始递减计数(也可递增,取决于配置),当计数到 0 时,产生中断信号,并且可以自动重新加载初始值,从而实现周期性的定时中断功能,常用于需要周期性触发的任务,如定时采样、周期性控制等。

- GPT(General Purpose Timer,通用定时器):

- 是一个 32 位的定时器,功能更灵活。

- 它可以工作在多种模式下,如自由运行模式、周期性模式、输入捕获模式、输出比较模式等。//在自由运行模式下,定时器从 0 开始不断递增计数;在周期性模式下,计数到设定值后产生中断并重新加载初始值;输入捕获可用于测量外部事件的时间间隔;输出比较可用于产生特定的时序信号,广泛应用于各种定时、计数和时序控制场景。