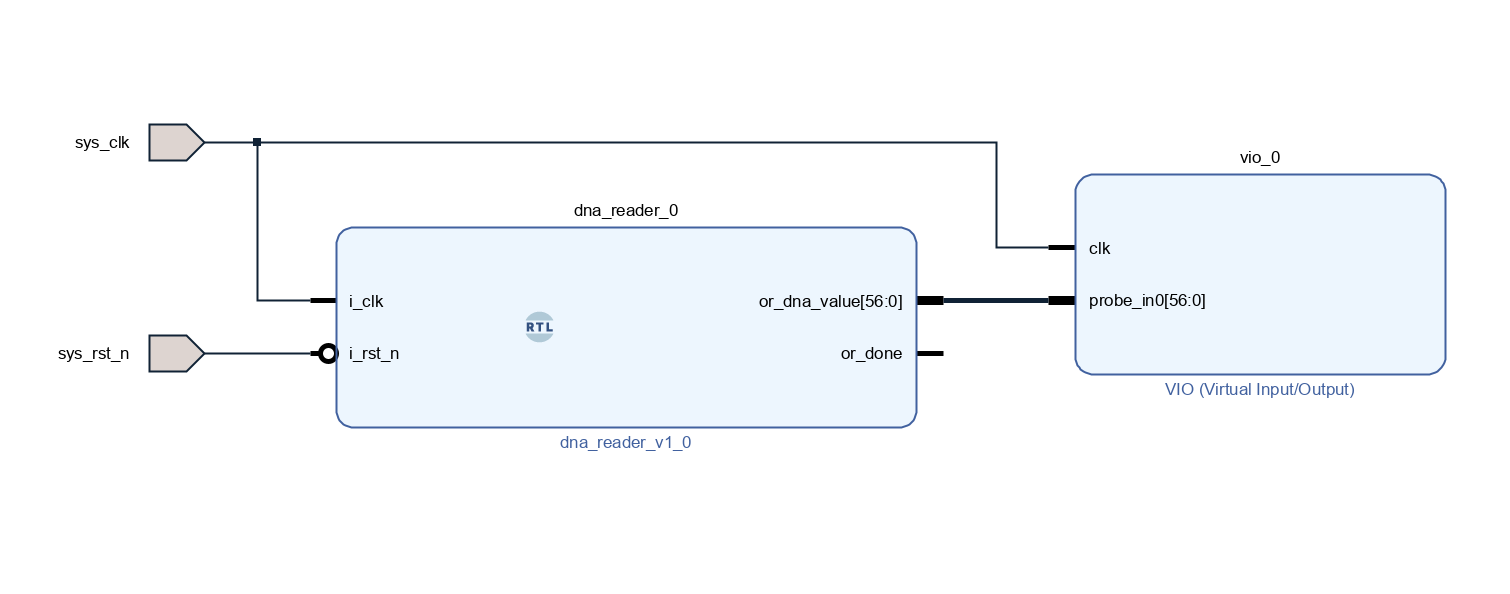

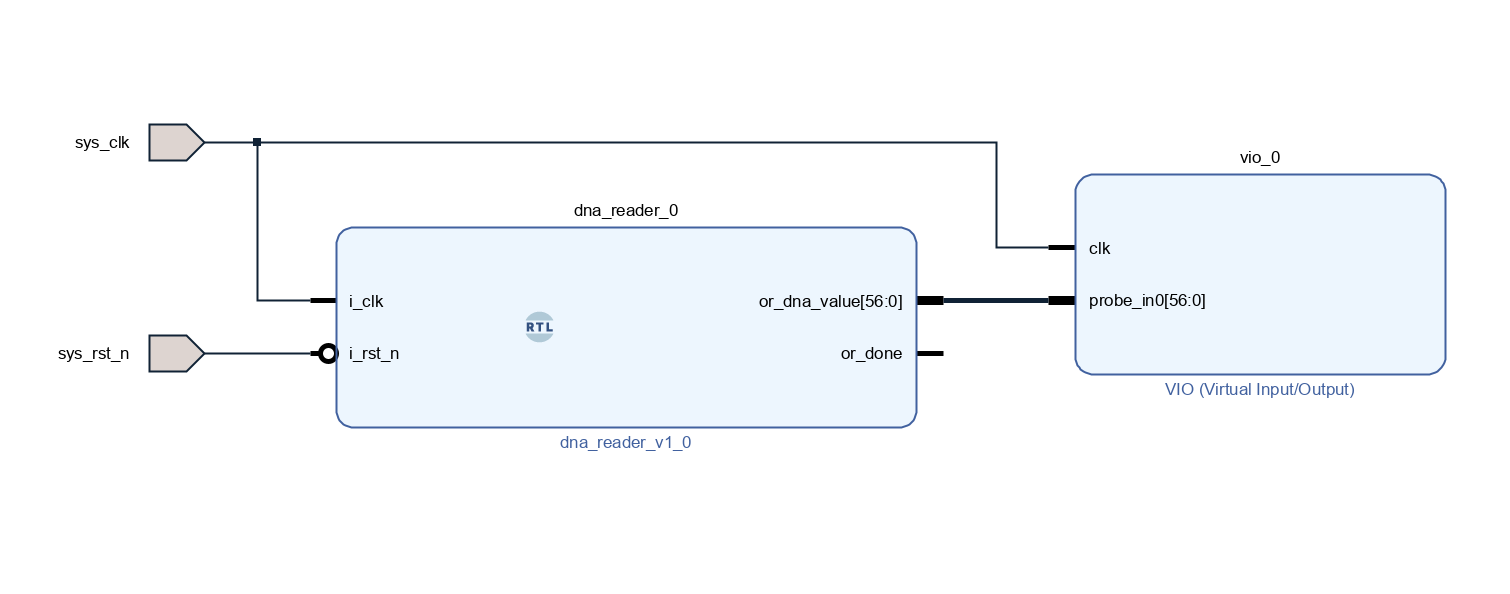

BD

create_clock -period 20.000 -name sys_clk [get_ports sys_clk]

set_property -dict {PACKAGE_PIN U18 IOSTANDARD LVCMOS33} [get_ports sys_clk]

set_property -dict {PACKAGE_PIN N16 IOSTANDARD LVCMOS33} [get_ports sys_rst_n]

dna_reader.v

/**读取DNA的8字节数据

**/

module dna_reader (input wire i_clk,input wire i_rst_n,output reg [56:0] or_dna_value,output reg or_done

);// DNA_PORT 原语信号reg r_read_en;reg r_shift_en;wire w_dout;// 读取 bit 计数reg [5:0] r_bit_cnt;// 实例化 DNA_PORT 原语DNA_PORT #(.SIM_DNA_VALUE(57'h123456789ABCDE) // 仿真用,综合时无效) u_dna (.CLK(i_clk),.READ(r_read_en),.SHIFT(r_shift_en),.DOUT(w_dout),.DIN(1'b0));// 状态机读取 DNAalways @(posedge i_clk or negedge i_rst_n) beginif (!i_rst_n) beginr_read_en <= 1'b1;r_shift_en <= 1'b0;r_bit_cnt <= 6'd0;or_dna_value <= 57'd0;or_done <= 1'b0;end else if (r_read_en) beginr_read_en <= 1'b0; // 只拉高一个周期启动读取r_shift_en <= 1'b1;end else if (r_shift_en && r_bit_cnt < 57) beginor_dna_value <= {or_dna_value[55:0], w_dout}; // 左移一位r_bit_cnt <= r_bit_cnt + 1;end else if (r_bit_cnt == 57) beginr_shift_en <= 1'b0;or_done <= 1'b1;endendendmodule

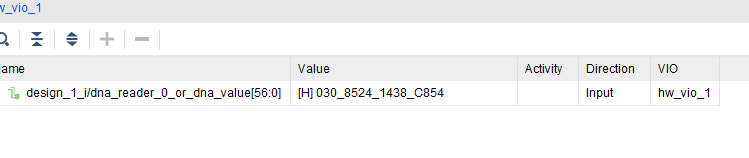

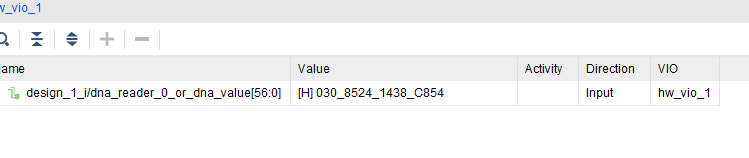

测试