Verilog语法学习EP11:串口发送模块

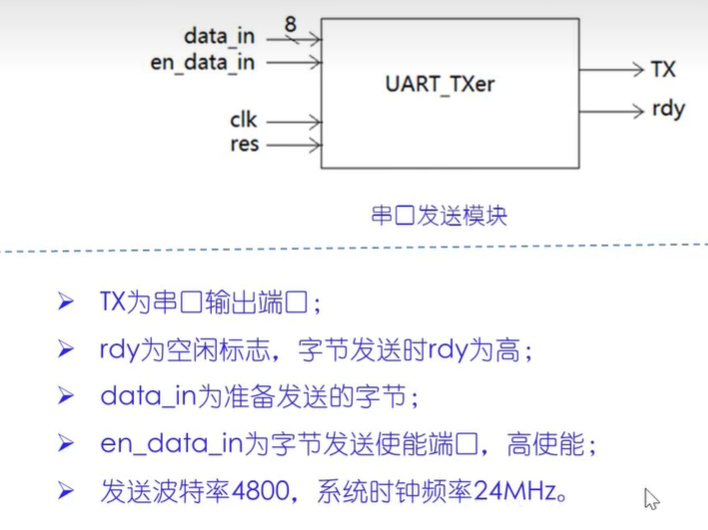

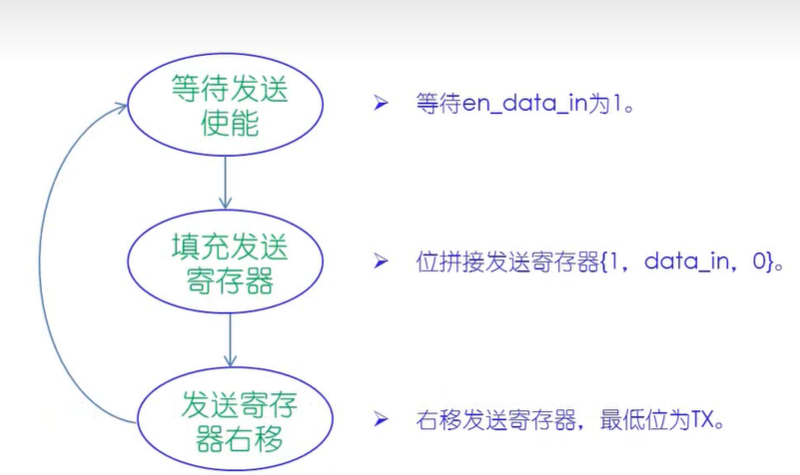

设计要求如下:

代码以及测试向量如下:

//2025.9.18

//串口发送模块

`timescale 1ns/10ps

module UART_TXer(clk,rst,data_in,en_data_in,TX,rdy

);

input clk;

input rst;

input[7:0] data_in;//准备发送的数据

input en_data_in;//发送使能

output TX;

output rdy;//空闲标志,0表空闲reg[3:0] state;//主状态机寄存器

reg[9:0] send_buf;//发送寄存器

assign TX=send_buf[0];//连接TXreg[12:0] con;//用于计算波特周期

reg[9:0] send_flag;//用于判断右移结束

reg rdy;always@(posedge clk or negedge rst) beginif(~rst) beginstate<=0;send_buf<=1;//TX空闲为1con<=0;send_flag<=10'b10_0000_0000;rdy<=0;endelse begincase(state)0://等待使能信号beginif(en_data_in) beginsend_buf={1'b1,data_in,1'b0};//结束 数据 起始send_flag<=10'b10_0000_0000;rdy<=1;state<=1;endend1://串口发送,寄存器右移beginif(con==5000-1) begincon<=0;endelse begincon<=con+1;endif(con==5000-1) beginsend_buf[8:0]<=send_buf[9:1];send_flag[8:0]<=send_flag[9:1];//不断右移endif(send_flag[0]) beginstate<=0;rdy<=0;endendendcaseend

endendmodule//-----testbench of UART_TXer----

module UART_TXer_tb;

reg clk,rst;

reg[7:0] data_in;

reg en_data_in;

wire TX;

wire rdy;UART_TXer UART_TXer(.clk(clk),.rst(rst),.data_in(data_in),.en_data_in(en_data_in),.TX(TX),.rdy(rdy)

);

initial beginclk<=0;rst<=0;data_in<=8'h0a;en_data_in<=0;#17 rst<=1;#30 en_data_in<=1;#10 en_data_in<=0;#2000 $stop;

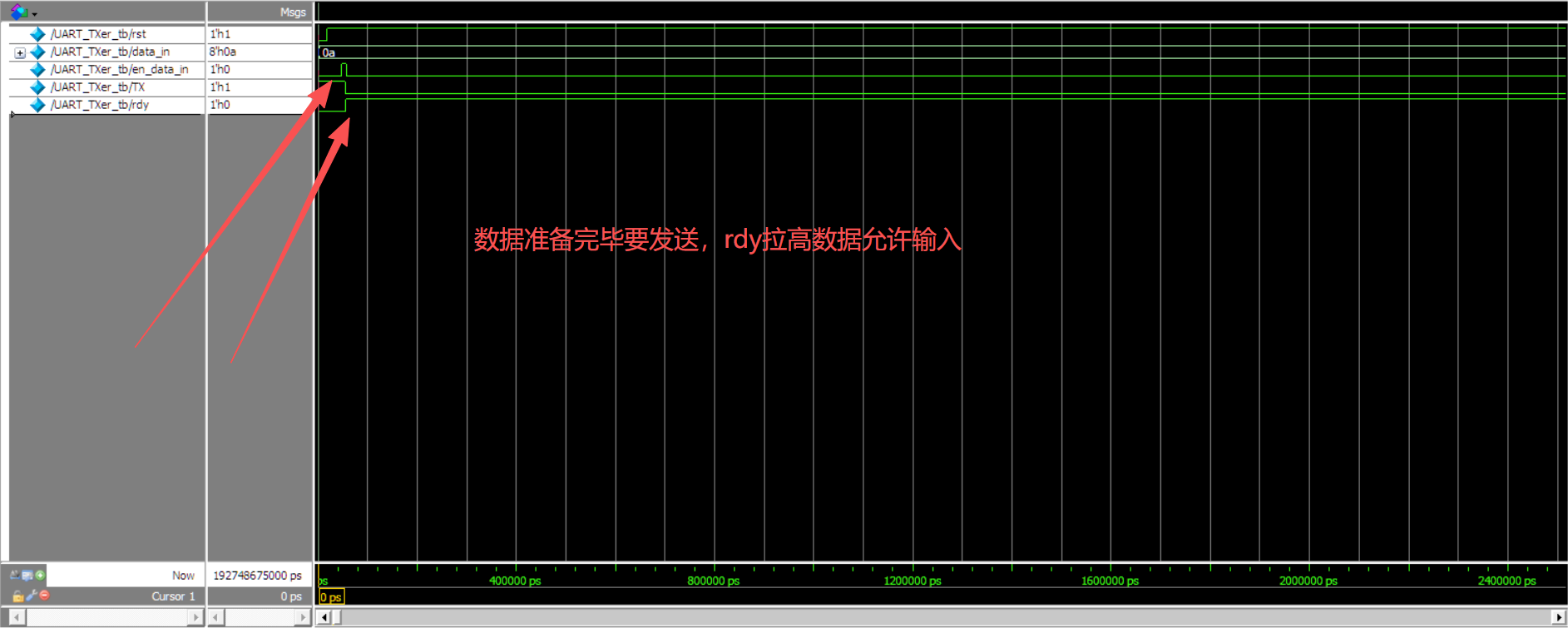

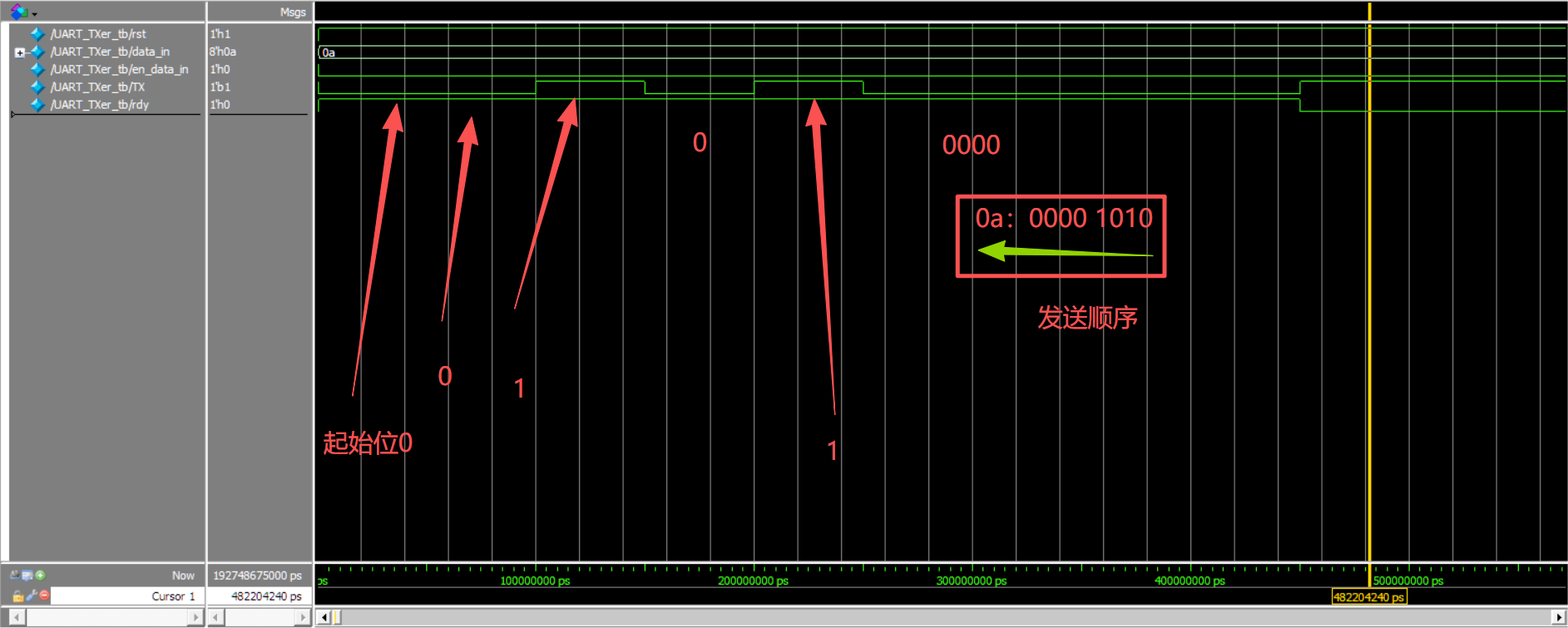

endalways #5 clk<=~clk;endmodule测试仿真波形图如下: