FPGA自学笔记--VIVADO RAM IP核控制和使用

本文主要学习在VIVADO软件中如何生成所需要的RAM IP核,以及相关的配置定义,并搭建tb对生成的IP读写控制时序进行仿真和测试。

一、sram ip生成与配置

1.1 ram ip创建方法

新建工程:打开 Vivado,创建一个新的工程项目。

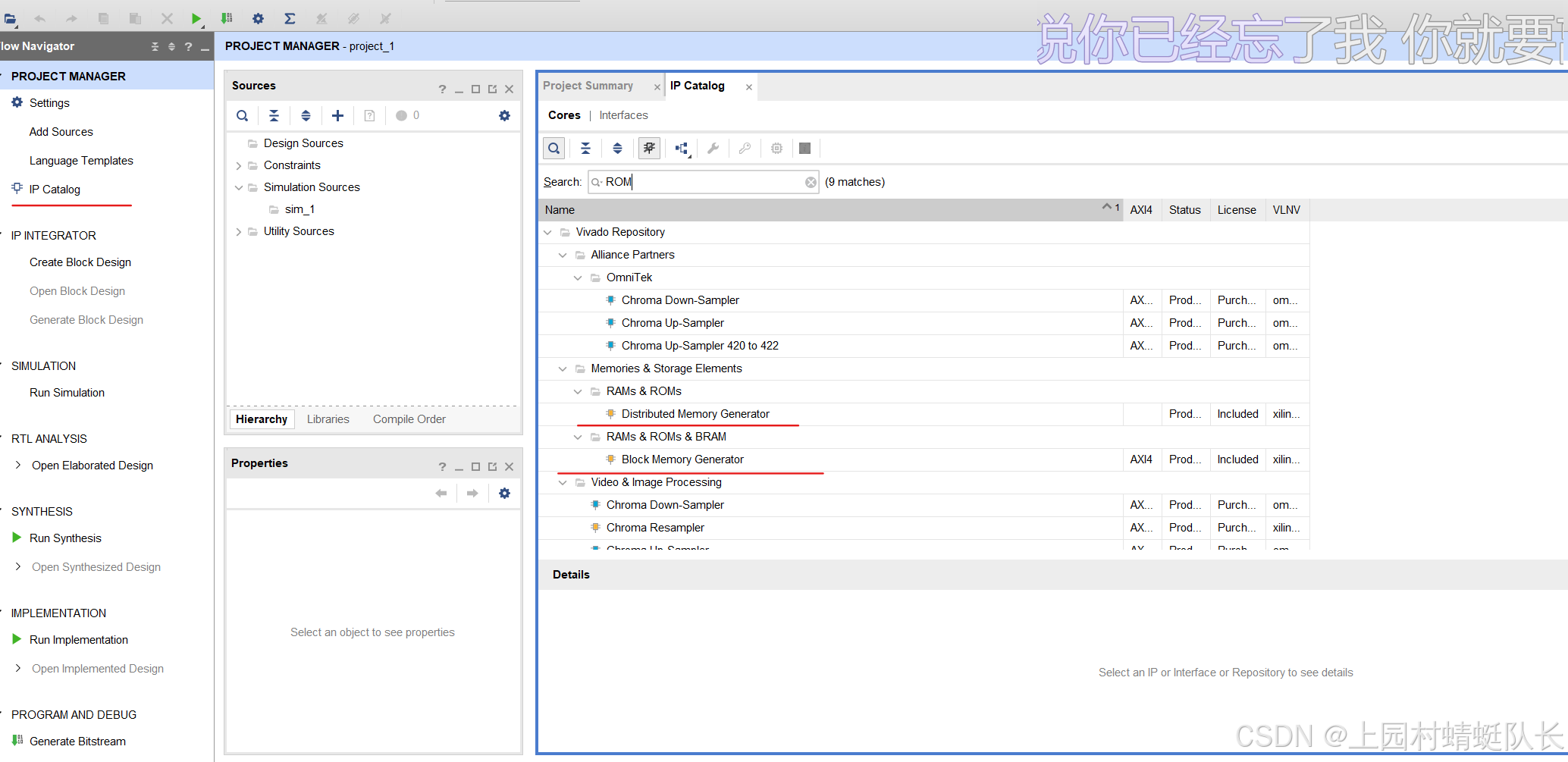

打开 IP Catalog:在 Vivado 主界面中,单击 IP Catalog。

搜索 RAM:在右侧窗口的 Search 框中输入

ram,会出现相关 IP 条目。RAM IP 类型:在 Memories & Storage Elements 分类下,可以看到两种主要的 RAM 创建入口:

Distributed Memory Generator

Block Memory Generator

主要差别:

Distributed Memory Generator:生成的 RAM/ROM 核心占用 FPGA 的 LUT(查找表) 资源。查找表本质上是一种小型 RAM,因此这种方式适合对存储容量要求不大但需要快速访问的场景。

Block Memory Generator:生成的 RAM/ROM 核心占用 FPGA 的 Block Memory(嵌入式硬件 RAM) 资源。适合需要较大容量存储、节省 LUT 资源的应用。

1.2 Xilinx RAM IP 配置选择说明

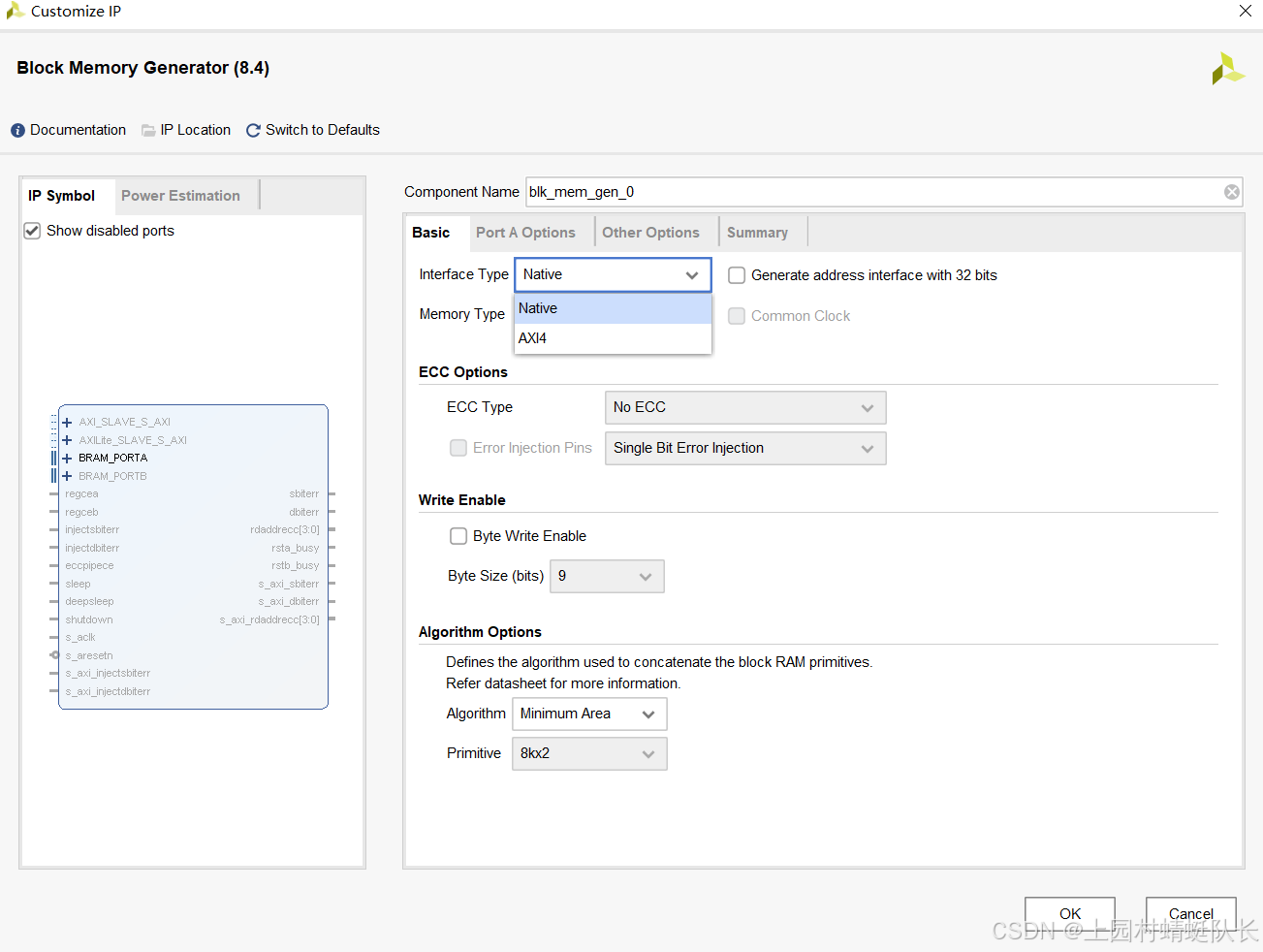

端口类型(Interface Type)

Xilinx 的很多 IP 核提供两种接口类型:在本例中,选择 Native 接口。

常规接口(Native):原生端口,直接控制信号。

AXI 接口:用于与 AXI 总线系统集成。

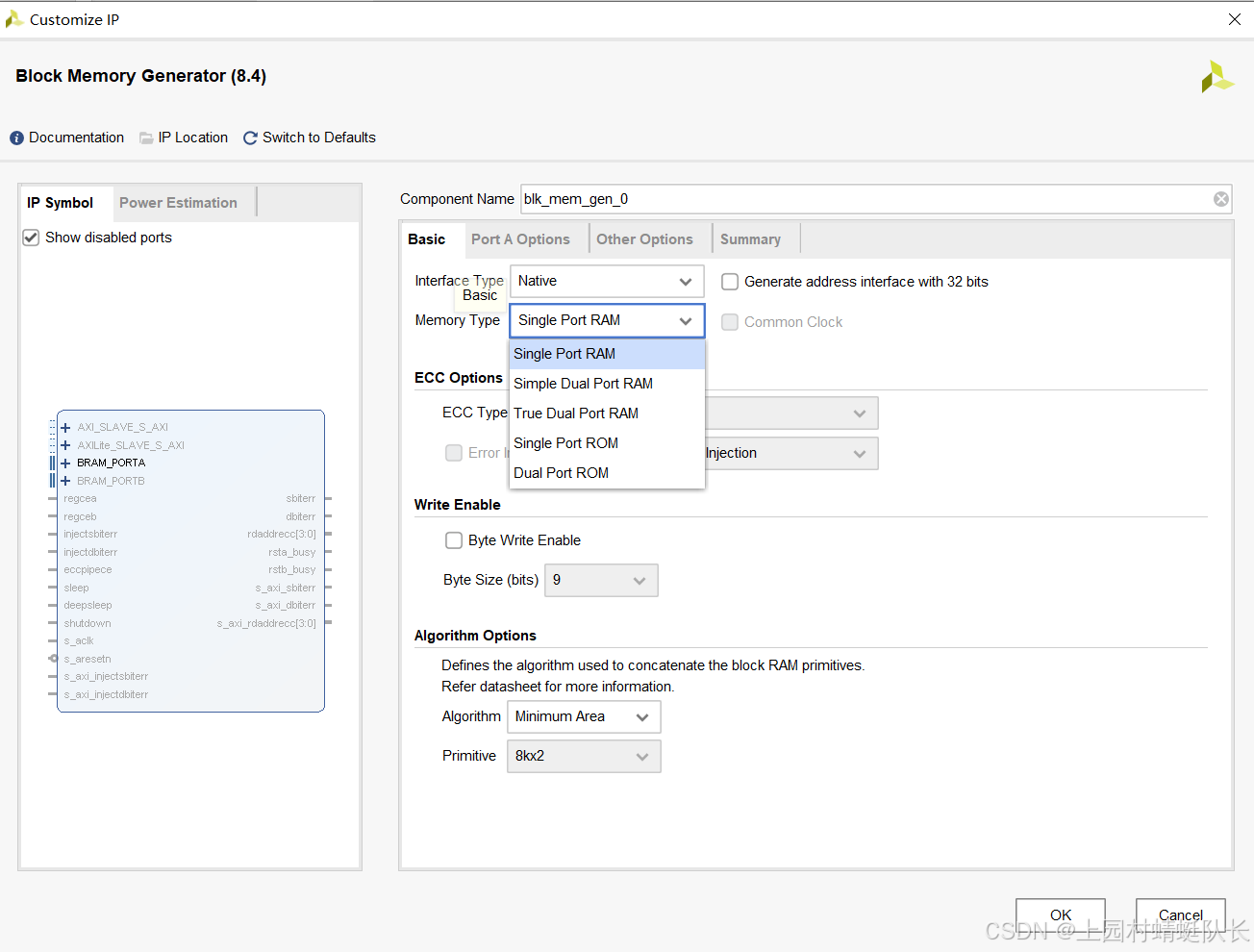

存储器类型(Memory Type)

对于 RAM,有三种类型可选:

类型 端口数量 时钟数量 读写特性 单端口 RAM 1 1 读写共享同一时钟,读写不能同时进行。 简单双端口 RAM 2(PORTA/PORTB) 2 PORTA 用于写,PORTB 用于读,可同时进行操作。 真双端口 RAM 2 2 两个端口各自独立,可同时读写,支持双向操作。

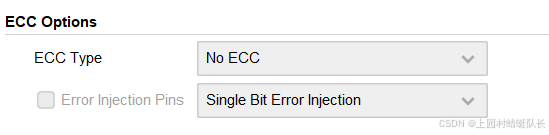

ECC 选项

ECC 全称是 Error Correction Capability,是在简单双端口 RAM 类型下的一种纠错功能,具体该功能的详细说明,可以查看 IP 手册,可以看到,只有在简单双端口RAM类型才是可以选择的,这里选择 NO ECC。ECC是FPGA和数字IC设计中一种经典数据校验和纠错的算法功能模块,以后单开一篇博客详细介绍其原理。

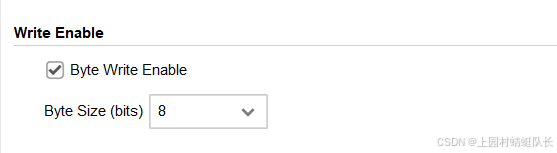

BYTE写使能

在配置 RAM 时,如果勾选写数据字节使能(Write Enable),写使能信号会按字节生成对应的位,使每个字节对应一个写使能位。字节大小可以设置为 8 或 9 位,因此输入输出数据的位宽必须是 8 或 9 的整数倍。由于这里需要一个位宽为 8bit 的 RAM,因此选择勾选 Write Enable 并将字节大小设置为 8bit。

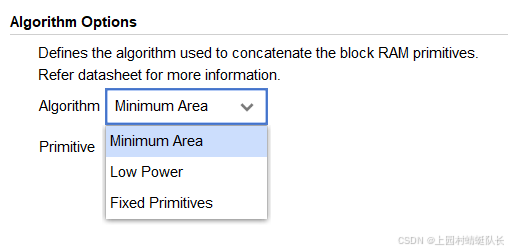

实现算法选择

在 RAM IP 的配置中,算法类型提供了三种选择:最小面积(Minimum Area)、低功耗(Low Power)以及固定原语(Fixed Primitives)。这些选项会影响生成的 RAM 的实现方式和性能特性,例如占用资源和功耗等。具体的实现细节可以参考 IP 手册,从第 42 页开始有详细说明。在当前配置中,我们保持默认的 最小面积 选项即可,不做额外修改。

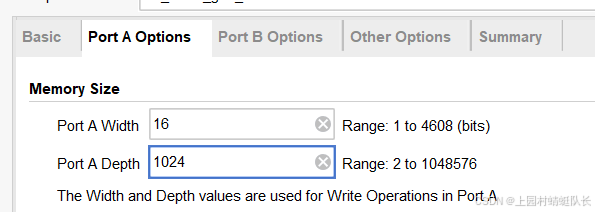

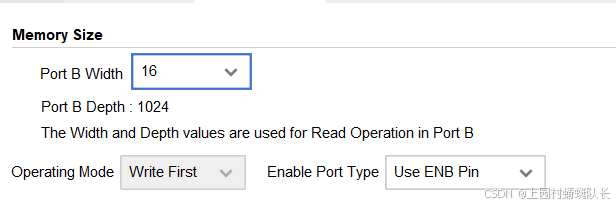

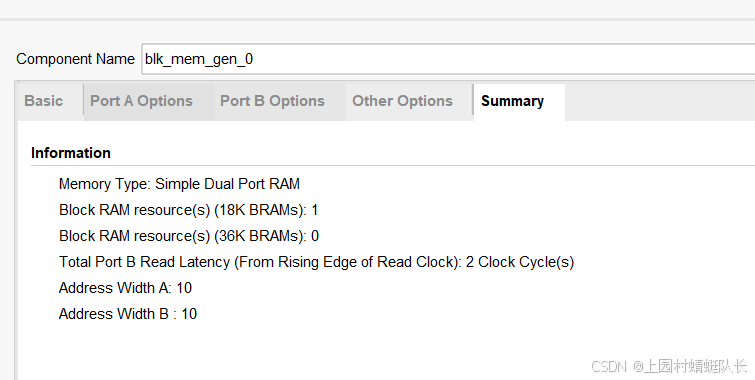

- RAM 数据位宽和深度设置(重要!!!)由于我们选择的是简单双端口ram,port A作为输入端口,我们这里配置数据位宽为16,数据深度1024,也就是最大存储1024个16bit数。

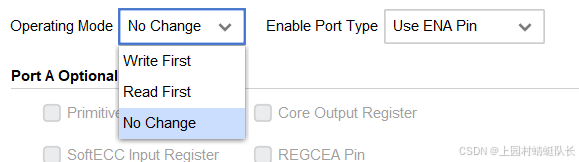

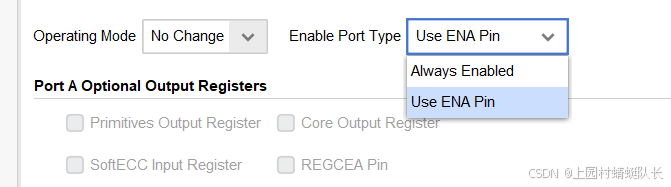

- 操作模式设置 在 RAM IP 的配置中,操作模式(Write Mode)提供三个选项,主要用于处理当同一地址在同一时钟周期同时发生读写操作时的行为。具体而言,这些选项决定了读出的数据是 写入的最新数据、该地址原有的数据,还是 读数据保持不变。选择合适的操作模式可以确保在读写冲突情况下的逻辑行为符合设计需求。Write First 模式下的波形,同时对同一地址读写,读出数据刚写入该地址的数据。Read First 模式下的波形,同时对同一地址读写,读出数据刚上次写入该地址的数据。No Change 模式下波形,读出的数据只有在进行读操作但未进行写操作时更新数据,在同时读写数据时,读出数据保持不变。

- 端口使能信号类型设置端口使能信号类型设置,一个是一直使能,一个是通过一个 ENA 信号管脚控制,这里选择 Always Enable。

- 端口 B 数据位宽和内存深度的设置 在简单双端口 RAM 中,端口 B 仅用于读操作,无法进行写操作,因此其操作模式不可修改。而在真双端口 RAM 中,端口 B 则可以进行操作模式设置。这里将端口 B 的使能设置为 Always Enable,确保该端口始终处于使能状态。

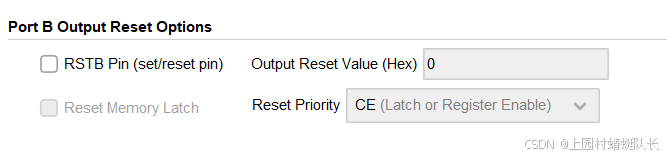

- 端口 B 输出置位/复位设置这里不创建置位/复位端口,需注意这里置位/复位并不复位 RAM 中的数据而是只复位寄存器上的值。

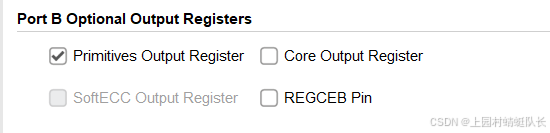

- 端口 B 输出寄存器配置 端口 B 的输出寄存器配置主要用于控制读出数据是否经过寄存器缓存,以改善时序性能或满足设计需求。在简单双端口 RAM 中,虽然端口 B 只能进行读操作,但仍可以配置其输出寄存器,通常可以选择 无寄存器(直接输出)或 有寄存器(输出数据经过寄存器打一拍),这样可以根据系统时序要求优化读数据的稳定性和延迟。在真双端口 RAM 中,同样可以独立配置端口 B 的输出寄存器,实现更灵活的时序控制。

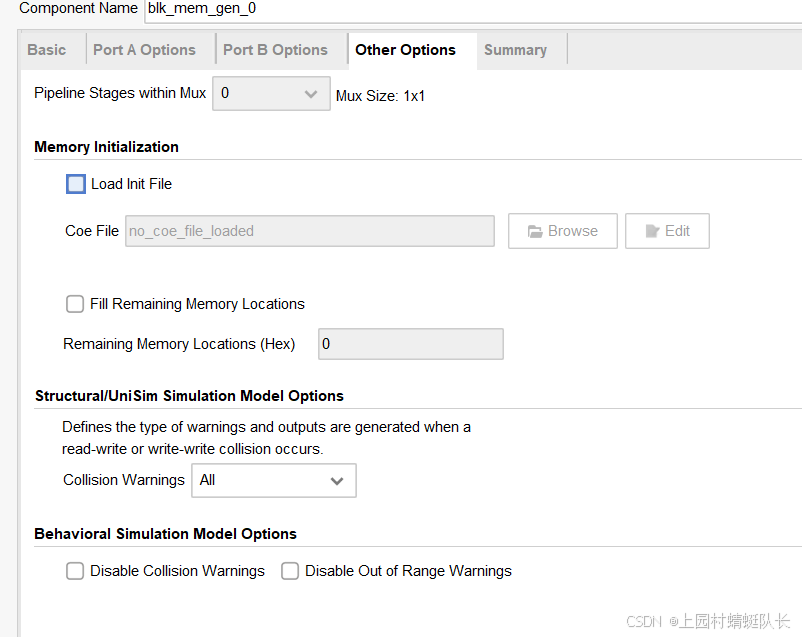

- 初始化设置 RAM IP 的初始化配置用于在 FPGA 上电或复位时为存储单元设置初始值,可以选择默认填充(如全 0 或全 1),也可以通过加载初始化文件(如

.mem或.coe文件)写入自定义数据。初始化可以在生成时包含初始内容,也可以通过逻辑模块在系统上电后写入,Vivado 常通过 COE 文件指定每个地址的初始数据。同时,可以配置是否在初始化时对输出端口进行寄存,以保证上电或复位期间读出的数据符合预期。这种初始化常用于存放查找表数据、系统默认值或测试仿真阶段的初始化数据。

- 全局summary ,点击OK

二、verilog例化模板

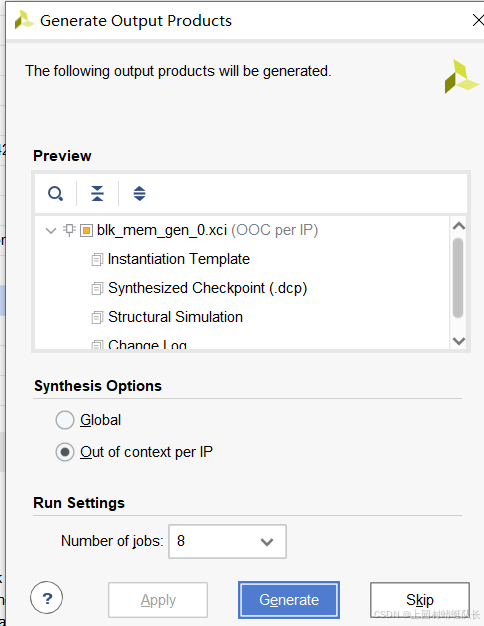

1、点击Generate,生成对应IP相关的文件。

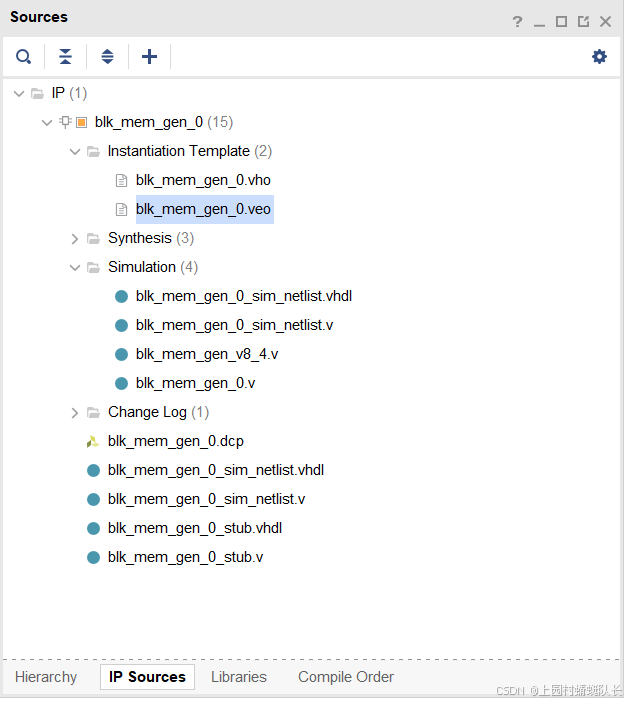

2、点击IP SOURCE一栏,查看例化文件,可以复制例化模块到自己的工程中使用。

blk_mem_gen_0 your_instance_name (.clka(clka), // input wire clka.ena(ena), // input wire ena.wea(wea), // input wire [0 : 0] wea.addra(addra), // input wire [9 : 0] addra.dina(dina), // input wire [15 : 0] dina.clkb(clkb), // input wire clkb.enb(enb), // input wire enb.addrb(addrb), // input wire [9 : 0] addrb.doutb(doutb) // output wire [15 : 0] doutb

);三、仿真TESTBENCH搭建。

由于本文中只会对ram ip 的行为进行测试,所以直接将模块例化到tb中仿真即可,添加tb文件如下。

`timescale 1ns/1ns`define clk_period 20module dpram_tb;reg clock;reg [15:0]data;reg [9:0]rdaddress;reg [9:0]wraddress;reg wren;wire [9:0]q;integer i;dpram dpram0(.clock(clock),.data(data),.rdaddress(rdaddress),.wraddress(wraddress),.wren(wren),.q(q));initial clock = 1;always#(`clk_period/2)clock = ~clock;initial begindata = 0;rdaddress = 30;wraddress = 0;wren = 0;#(`clk_period*20 +1 );for (i=0;i<=1023;i=i+1)beginwren = 1;data = 1024 - i;wraddress = i;#`clk_period;endwren = 0;#(`clk_period*20);for (i=0;i<=15;i=i+1)beginrdaddress = i;#`clk_period;end#(`clk_period*20);$stop; endendmodule