MIPI D-PHY布线规则

布线规则

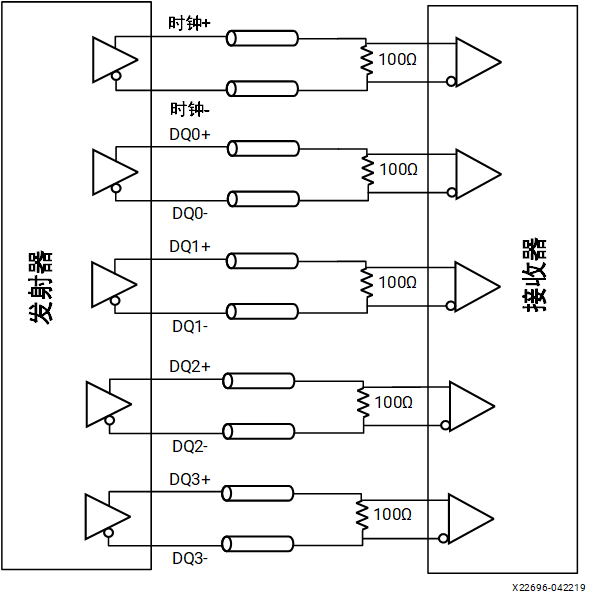

一组典型 MIPI D-PHY 核由 4 条差分数据通道和 1 条差分时钟通道组成,如下图所示。

MIPI D-PHY 发射器和接收器路径。

当前高频率显示器基本都是两组MIPI,master和slave,各含四条差分数据通道和一条差分时钟通道,总共八条差分数据线和两条差分时钟通道,20Pin。

上图显示了有关阻抗、走线长度、间隔、偏差和终端的 MIPI D-PHY PCB 准则。

| 参数 | 规格 |

|---|---|

| 走线类型 | 带状线 |

| 差分阻抗 | 95±10% Ω |

| 走线长度 | ≤ 10.0 英寸 1,2 |

| 走线对内间距 | 2 倍走线宽度 |

| 与其他 MIPI 对的间距 | 5 倍走线宽度 |

| 与其他非 MIPI 对的间距 | 6 倍走线宽度 |

| 每对 P/N 间的偏差 | ±5mil |

| 时钟与数据间的偏差 | ±10mil |

| 数据与数据间的偏差 | ±10mil |

| 多组MIPI差分线之间的间距 (maste、slave两组共八对数据差分线、两对时钟差分线) | ±10mil |

| 接收器终端 | 100 Ω 差分 |

其他链接: https://docs.amd.com/r/zh-CN/ug863-versal-pcb-design/MIPI-D-PHY https://pcbartists.com/design/pcb-design/mipi-dsi-pcb-layout-notes/?srsltid=AfmBOor6JdMtX1493Any7QYXumWMmDZhCGi6ZuSocUkgQ4wCGauY8z1C https://resources.pcb.cadence.com/blog/2021-efficient-differential-pair-routing-guidelines-to-speed-up-pcb-routing https://www.intel.com/content/www/us/en/docs/programmable/817561/24-1-2-2-0/mipi-interface-layout-design-guidelines.html | |