Zynq开发实践(SDK之第一个纯PS工程)

【 声明:版权所有,欢迎转载,请勿用于商业用途。 联系信箱:feixiaoxing @163.com】

学编程的时候,大家一般都比较重视第一个项目的创建和执行。第一个fpga程序一般是led闪烁,第一个c程序一般就是hello world程序。今天就介绍下,zynq下面的hello world应该怎么编写。和其他soc程序不一样,zynq编写c代码之前,需要先创建一个block design,这就是最大的不同。整个流程稍微多了一点,不过熟能生巧就好。

1、创建zynq工程

第一步还是创建zynq工程。这一步和之前fpga没有什么区别,唯一需要注意的地方就是对zynq芯片的选择。我们习惯于直接用020clg400-1搜索,搜到的最后一个结果就是我们需要的芯片。

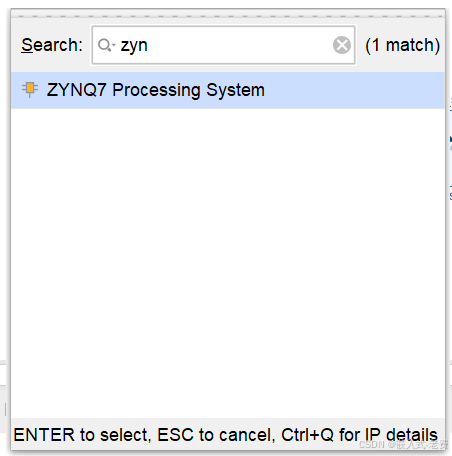

2、创建block design,添加cpu

fpga开发是添加verilog代码和约束文件。而zynq的软件,则是需要先添加block design,这是一个顶层设计的框架,这个框架里面有cpu、有总线、有复位,还有可能有各种各样的外设。当然目前为止,作为入门,我们一开始不弄那么复杂。添加block design之后,直接添加cpu即可。

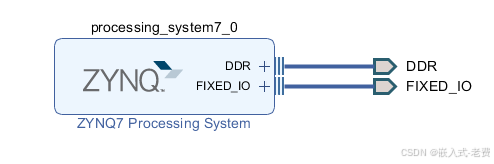

3、去除不必要的ps连接线

因为没有ps之外的其他外设,所以可以去除下面三部分内容,

1)FCLK_RESET0_N;

2)M_AXI_GP0 interface;

3)FCLK_CLK0。

去除之后,就是这样的形式,即只有ddr和54个fixed io,这些接口是不需要添加端口约束的。

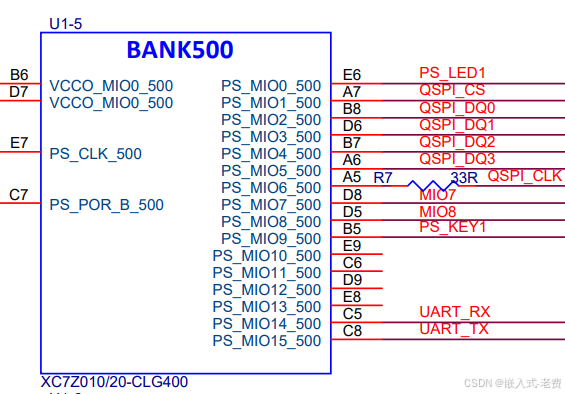

4、添加打印串口,配置ddr参数

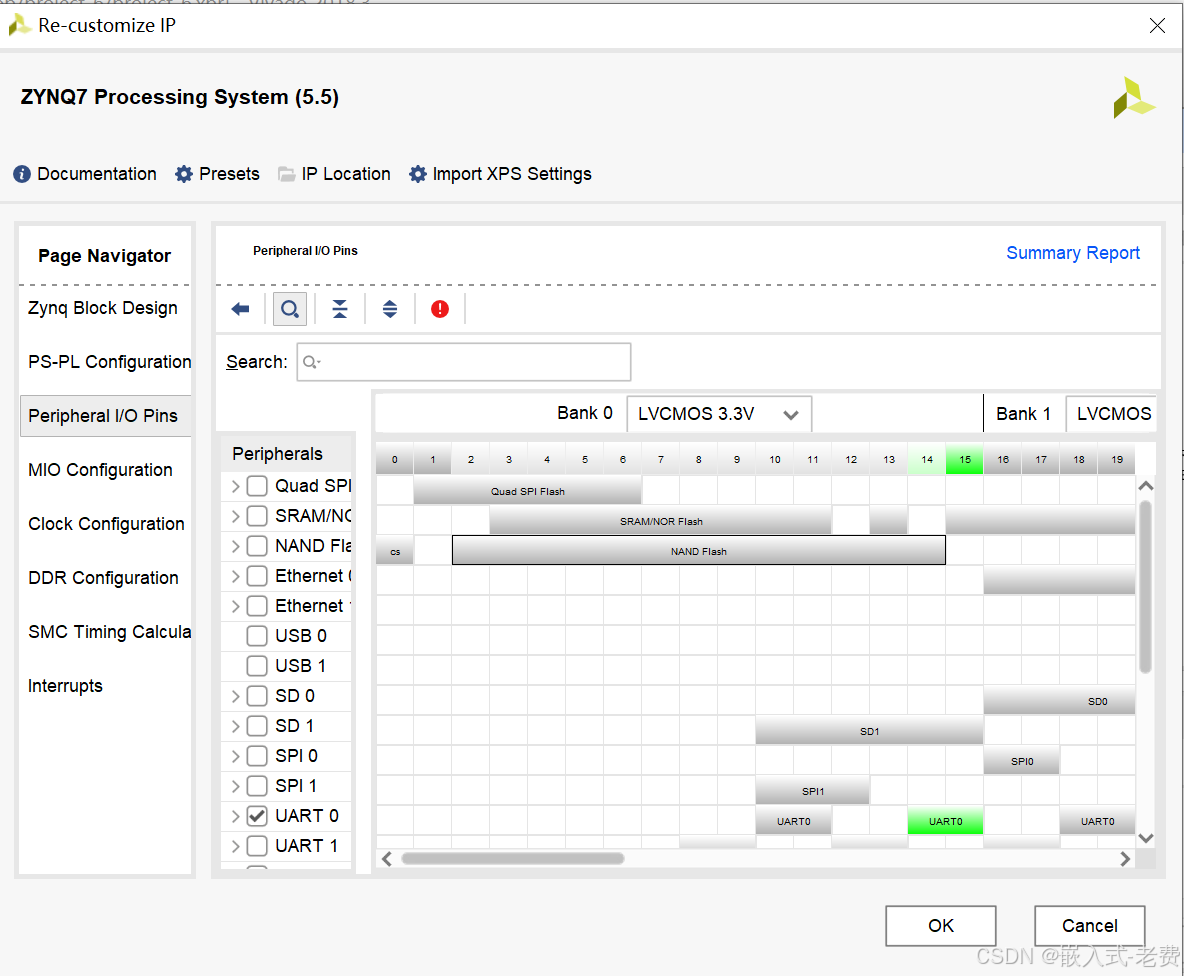

既然是hello world程序,那么串口肯定是少不了的。这里我们选择了uart0串口,作为输出的接口。但是uart0本身可以放在很多其它的位置,所以我们首先需要通过电路图,来确认最终的位置。

这里,我们把uart0放在了pin14、15引脚上面,即MIO14、MIO15。

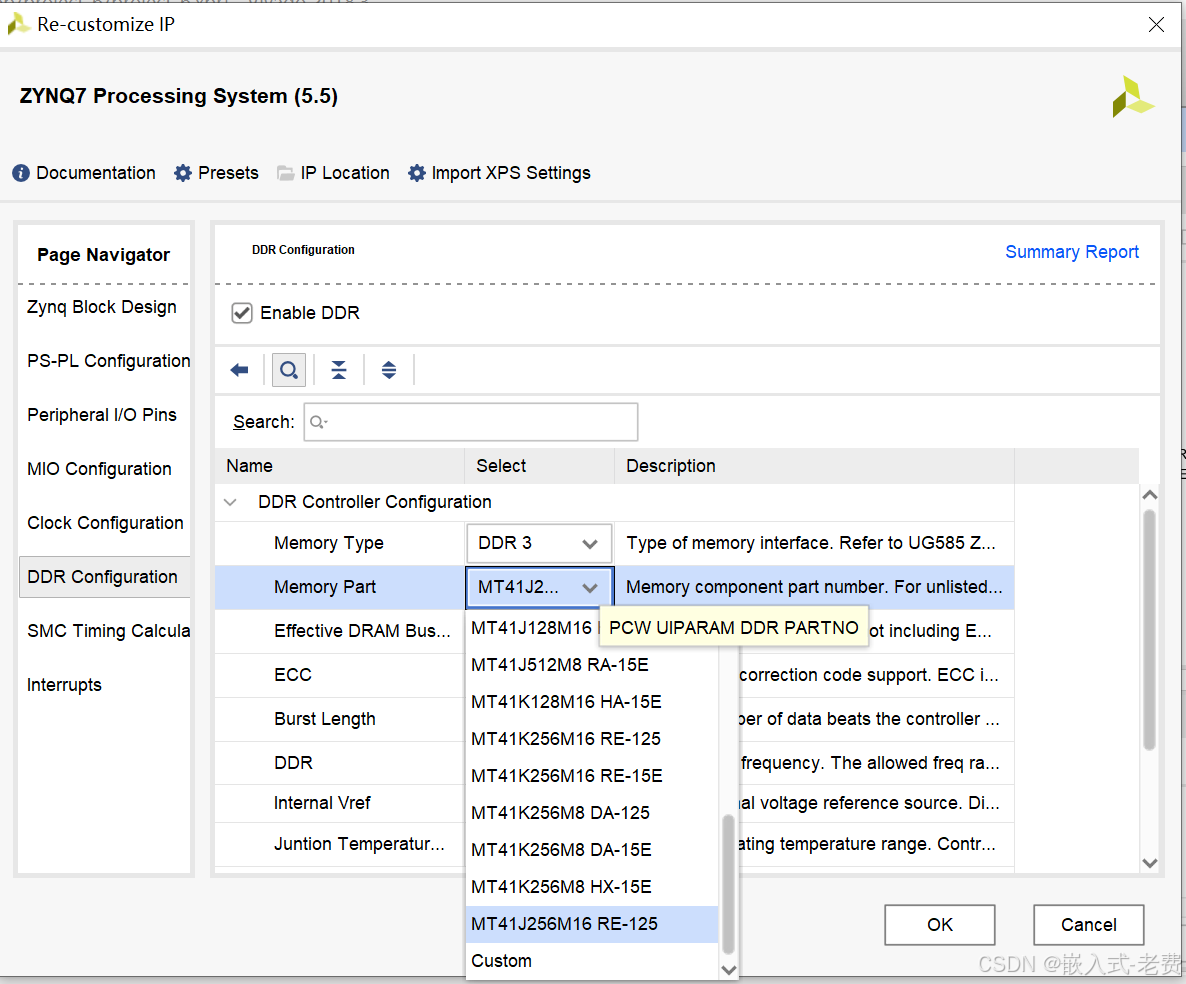

除了uart之外,ddr也是少不了的。因此哪怕用zynq做纯mcu开发,ddr也是很大的优势。一般来说,这里配置的是ddr3控制器。通常只要选择好ddr芯片型号即可,最多设置一下数据位。我们这里选用的是最后一个选项,即MT41J256M16 RE-125,数据宽度是16。大家可以根据自己的开发板,灵活做出选择。

5、保存block design,开始生成文件

block design保存好之后,最好利用validate 按钮确认下、保存下。接下来生成的文件有两个,一个是右击,选择“Generate Output Products”生成文件。结束之后,继续右击,选择“Create HDL Wrapper”生成文件。两个都ok之后,代表block designer就创建结束了。

6、导出硬件环境,打开sdk软件

这里导出硬件环境比较简单,直接单击“File”-》“Export”-》"Export Hardware"即可,不用包含bitstream文件,因为没涉及到pl开发。完毕之后,继续单击“File”-》“Launch SDK”,即可打开sdk软件。

7、创建hello world软件

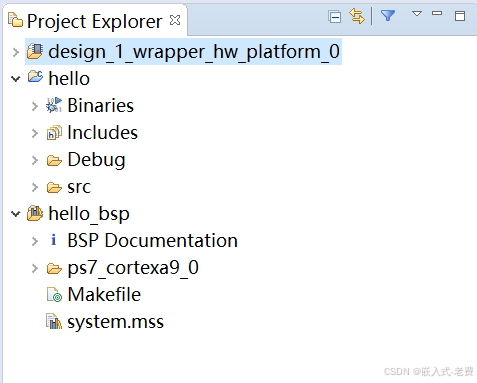

打开sdk之后,一般已经有一个design_1_wrapper_hw_platform_0工程了。我们只需要继续创建hello world工程即可。创建的过程中,系统会帮我们自动匹配一个bsp工程。而且工程创建以后,sdk会自动编译好,帮助生成elf文件。如果我们需要用jtag运行程序,只需要单击这个elf,右击选择“”Run as”-》“Launch on hardware(System Debug)”即可,这样程序就可以跑起来,用mobaxterm看到串口打印了。

当然在此之前,需要连接好两根type c线,一根是jtag,一根是usb转串口。

8、可能会出现的问题

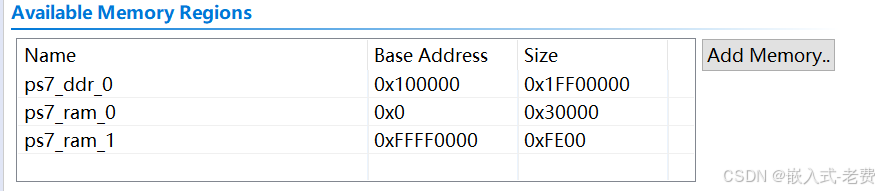

假设ddr没有初始化好的话,可能会出现write memory 0x100000 error这样的错误。出现错误之后,有两种解决办法,一种是继续去寻找ddr配置失败的原因。还有一种就是修改link file,删掉原来的ps7_ddr_0,把现在的ps7_ram_1修改成ps7_ddr_0,这样程序也是可以跑起来的。

大家不知道的是,zynq内部也有一段ram空间,同样可以跑代码、执行程序,不一定非得运行在ddr上面。改了之后,不需要初始化ddr,重新run一下jtag,自然就可以跑起来了。

9、jtag做了哪些工作

我们发现程序启动的时候,本身是运行在ddr上面的,那么ddr是谁初始化的? 答案就是jtag。jtag不仅可以初始化ddr,还可以初始化其他外设,甚至可以帮助debug程序。但是如果程序需要发布给客户的话,就不能依赖jtag了,这个时候就需要准备fsbl程序了。当然,这就是后面的话题了。