【硬件-笔试面试题-87】硬件/电子工程师,笔试面试题(知识点:解决浪涌电压)

题目汇总版--链接:

【硬件-笔试面试题】硬件/电子工程师,笔试面试题汇总版,持续更新学习,加油!!!-CSDN博客

【硬件-笔试面试题-87】硬件/电子工程师,笔试面试题(知识点:解决浪涌电压)

1、题目

解决浪涌电压

2、知识点

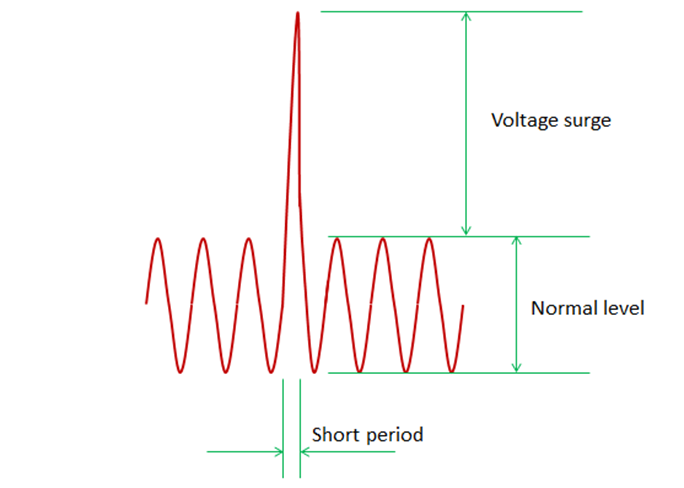

解决浪涌电压的核心是 **“抑制 + 泄放”**,需根据浪涌来源(如雷击、开关动作、电源波动)和应用场景(如电源入口、敏感芯片前端)选择适配方案,常见解决方法可分为 4 类:

一、电源入口级浪涌防护(应对外部强浪涌,如雷击、电网波动)

适用于设备总电源输入侧,目的是将大功率浪涌快速泄放,保护后级电路:

- 压敏电阻(MOV):并联在电源火线与零线 / 地线之间,浪涌电压超过其额定电压时迅速导通,将浪涌电流泄放至地;优点是响应快、成本低,缺点是单次浪涌后可能失效,需配合 fuse 防止烧毁。

- 气体放电管(GDT):同样并联使用,浪涌电压击穿内部气体后形成低阻通路泄放电流,适用于高电压、大通流量浪涌(如雷击);缺点是响应速度略慢(约 100ns),常与压敏电阻搭配使用,互补响应时间。

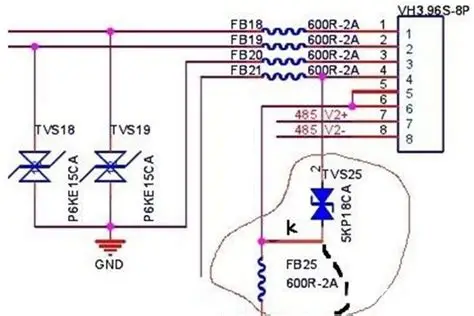

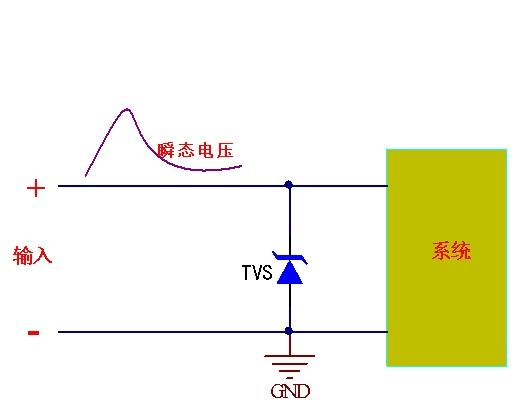

- TVS 二极管(瞬态抑制二极管):并联在电路中,浪涌到来时瞬间击穿,以极低的导通电压吸收浪涌能量;相比压敏电阻,其击穿电压更精准、漏电流更小,适合中低功率浪涌防护(如电源适配器入口)。

- 浪涌保护器(SPD):集成 MOV、GDT、TVS 等器件的模块化产品,按 “分级防护” 设计(如一级 SPD 防雷击、二级 SPD 防电网开关浪涌),常用于工业设备、建筑配电系统。

二、电路中间级浪涌抑制(应对内部开关浪涌,如 MOS 管、继电器动作)

适用于功率器件(如 H 桥 MOS 管、继电器)两端,抑制开关动作产生的电压尖峰:

- RC 吸收电路:并联在开关器件(如 MOS 管漏源极、继电器线圈两端),由电阻(R)和电容(C)串联组成;电容吸收浪涌电压的能量,电阻消耗能量并抑制电容谐振,有效缓解 “开关断开时的电压尖峰”(如电机驱动电路中 MOS 管关断时的浪涌)。

- 续流二极管:反向并联在感性负载(如电机、继电器线圈)两端,当负载断电时,线圈产生的反向浪涌电流通过二极管形成回路,避免高电压击穿开关器件;需选择快恢复二极管(如 FR 系列),匹配负载电流。

- 钳位二极管:将浪涌电压钳位在安全值(如芯片电源轨的上限电压),例如在 MCU 的 IO 口或电源引脚并联 TVS 二极管,防止外部信号浪涌击穿芯片。

三、接地与布线优化(从 PCB 设计层面减少浪涌影响)

- 单点接地:浪涌泄放路径需独立且短,避免泄放电流流经敏感电路(如模拟信号地、控制地);例如,压敏电阻、GDT 的接地端直接连接 “功率地”,并通过单独过孔到 PCB 地层,不与信号地共用走线。

- 功率回路布线:浪涌常伴随大电流,功率回路(如电源输入 - 浪涌防护器件 - 地)需用粗铜线(如 2mm 以上),减少寄生电感;寄生电感过大会导致浪涌电流流过时产生额外电压尖峰(U=L*di/dt),加剧浪涌危害。

- 隔离设计:通过光耦、磁耦或隔离电源将 “高压浪涌侧”(如电网端)与 “敏感控制侧”(如 MCU)隔离,避免浪涌通过共地或信号线窜入控制电路。

四、器件选型与参数匹配(确保防护有效,不失效)

- 选择防护器件时,需明确关键参数:

- 额定电压(Vr):大于电路正常工作电压(如 220V 电网用 MOV,Vr 选 275V AC),避免正常工作时误导通。

- 浪涌电流(Ipp):防护器件的最大泄放电流需大于实际可能的浪涌电流(如电机驱动电路,按电机启动电流的 2-3 倍选型)。

- 响应时间:敏感芯片(如 MCU)前端需选响应快的 TVS(ns 级),而电源入口可容忍 GDT 的 μs 级响应。

题目汇总--链接:

【硬件-笔试面试题】硬件/电子工程师,笔试面试题汇总版,持续更新学习,加油!!!-CSDN博客