ARM 体系结构与存储器

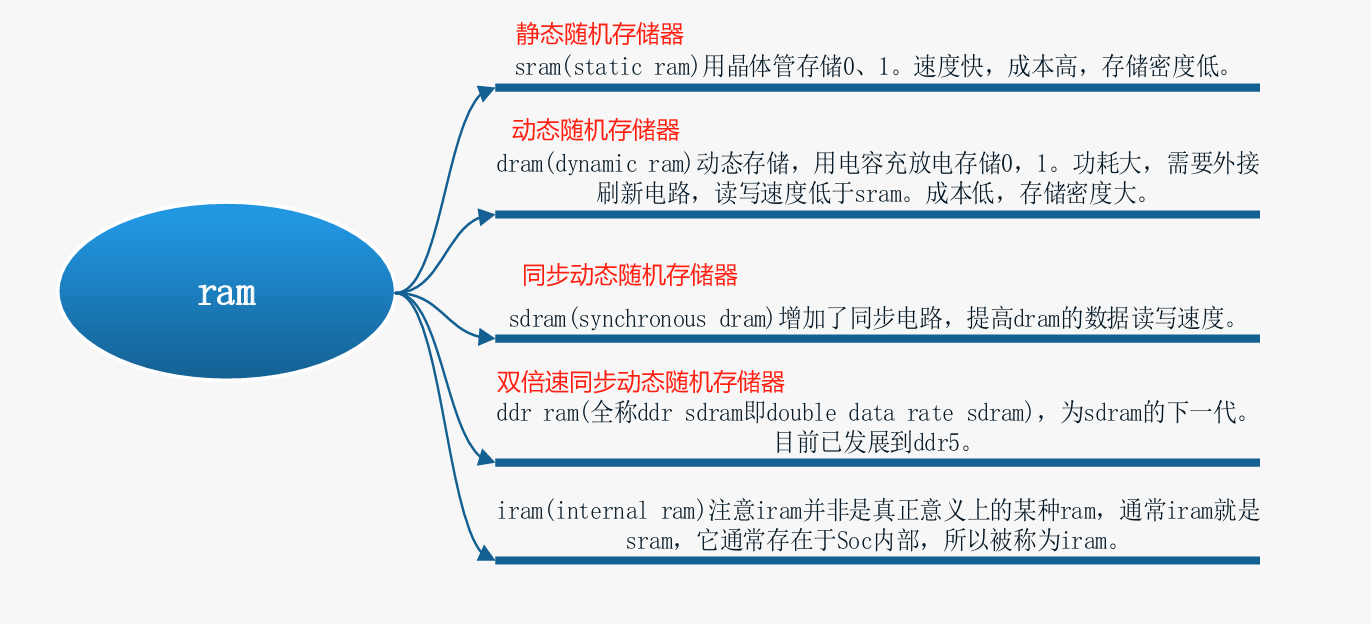

一、RAM 分类

SRAM (Static RAM)

用 触发器/晶体管 存储 0/1。

特点:速度快、功耗低(静态保持),但成本高、容量小。

应用:片上缓存、寄存器文件、单片机内存。

DRAM (Dynamic RAM)

用 电容充放电 存储 0/1。

特点:存储密度高、成本低,但需要刷新电路,速度低于 SRAM。

应用:PC 内存、大容量存储。

SDRAM (Synchronous DRAM)

在 DRAM 上增加时钟同步,提高读写速度。

DDR RAM (Double Data Rate SDRAM)

SDRAM 的升级版,在时钟上升沿和下降沿均可传输数据。

发展分支:DDR → DDR2 → DDR3 → DDR4 → DDR5。

IRAM (Internal RAM)

本质上是 片上 SRAM,直接集成在 SoC 内部,速度快、可直接被内核访问。

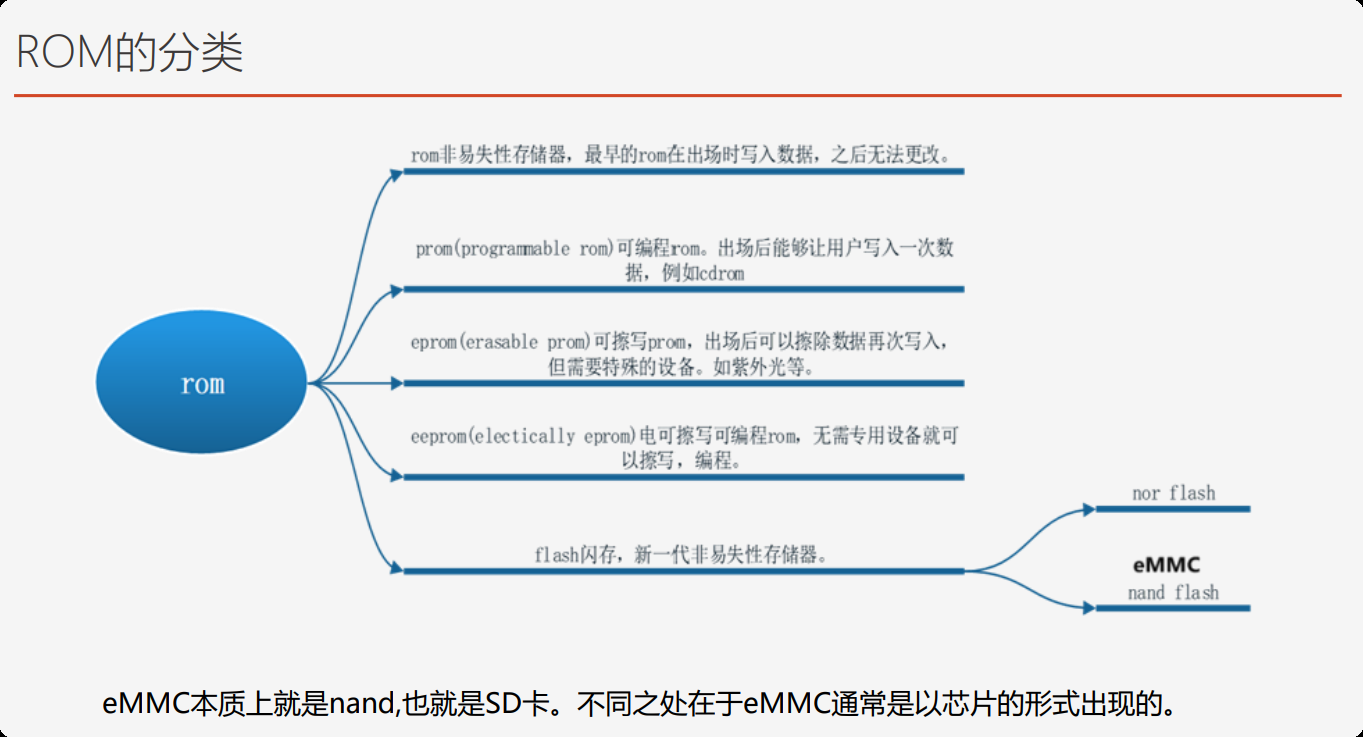

二、ROM 分类

ROM (Read Only Memory)

出厂时数据固定,不可更改。

PROM (Programmable ROM)

用户可写入一次数据。

EPROM (Erasable PROM)

可通过紫外线擦除后重新写入。

EEPROM (Electrically Erasable PROM)

电擦写方式,速度较慢,但方便修改少量数据(如配置参数)。

Flash 闪存

NOR Flash:字节寻址,可直接执行(XIP, Execute In Place)。

NAND Flash:页寻址,容量大、寿命长,需控制器管理。

eMMC:嵌入式 NAND,带控制器,简化接口。

UFS(Universal Flash Storage):新一代高速存储接口。

三、ARM 内核结构(Cortex-A7 为例)

基本信息

32 位架构,数据宽度 4 字节。

RISC(精简指令集)设计,流水线执行。

功能单元

ALU:算术逻辑运算。

通用寄存器 R0-R12:主要运算与数据存储。

专用寄存器:

PC (R15):程序计数器。

LR (R14):连接寄存器,保存返回地址。

SP (R13):栈指针寄存器。

CPSR:当前程序状态寄存器。

SPSR:保存的 CPSR(用于异常返回)。

存储与控制

MMU (Memory Management Unit):虚拟地址 → 物理地址映射。

Cache:

I-Cache(指令缓存)

D-Cache(数据缓存)

总线:

AHB:高性能总线(CPU ↔ 内存)。

APB:外设总线(低速外设)。

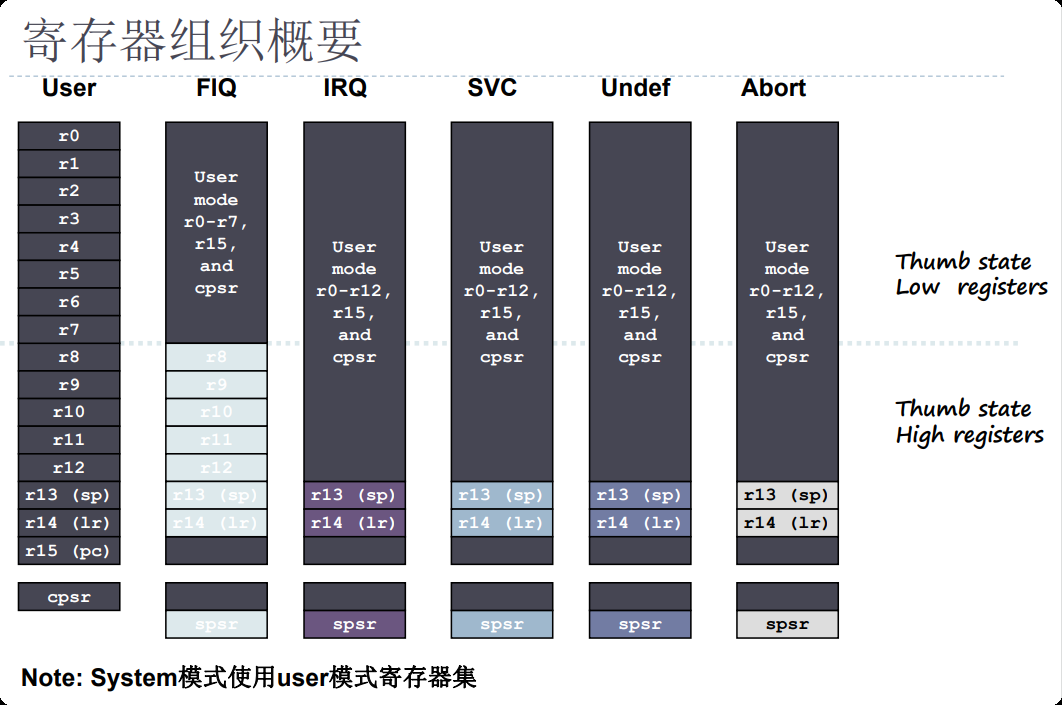

四、ARM 工作模式

Cortex-A7 有 9 种模式:

User:非特权模式,普通应用运行。

FIQ:快速中断模式,高优先级,专用寄存器多,适合实时处理。

IRQ:普通中断模式。

Supervisor (SVC):上电复位或软中断进入。

上电默认进入 SVC 模式,由启动代码切换到 User 模式。

Abort:存取异常模式。

Undef:未定义指令模式。

System:与 User 共用寄存器,但具备特权。

Monitor:安全监控模式(TrustZone)。

Cortex-A 特有模式(部分扩展架构支持)。

说明:

每种模式都有 独立 SP、LR,保证中断/异常隔离。

ARM 将 中断统一视为异常。

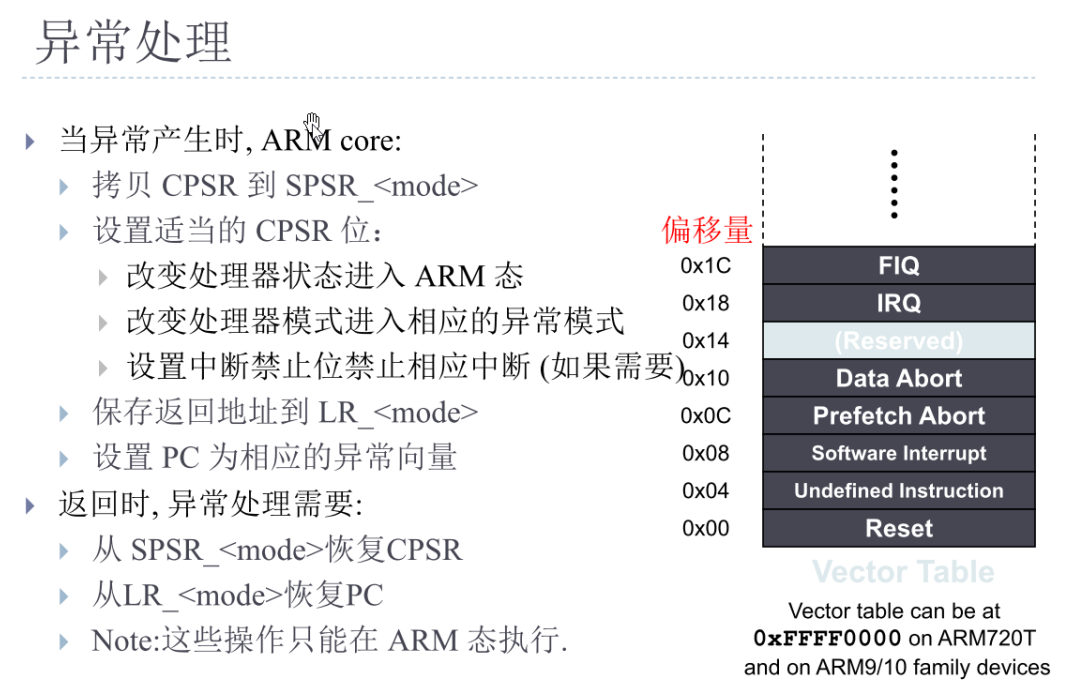

五、异常处理

异常类型

Reset(复位)

Undefined Instruction(未定义指令)

SWI(软中断)

Prefetch Abort(指令取指异常)

Data Abort(数据访问异常)

IRQ(普通中断)

FIQ(快速中断)

异常向量表

固定地址存放不同异常入口。

例如:复位向量通常在

0x00000000或0xFFFF0000。

底层流程

保存 CPSR → 切换模式 → 修改 PC → 跳转异常向量表地址。

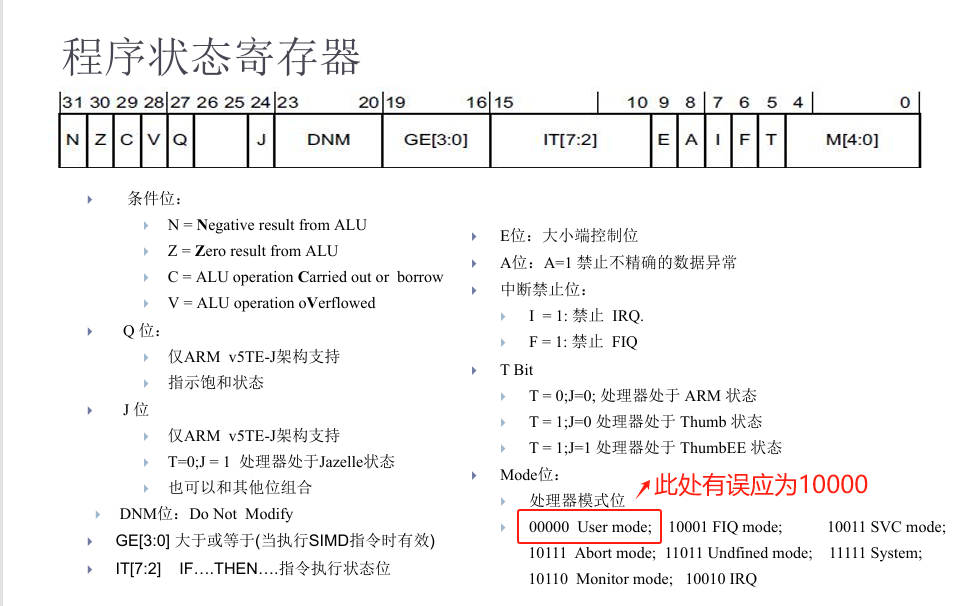

六、CPSR 程序状态寄存器

Mode 位:工作模式选择。

条件标志位:

N(Negative):结果为负数 → 1。

Z(Zero):结果为 0 → 1。

C(Carry):无符号运算进位/借位。

V(Overflow):有符号数溢出。

E 位:大小端标志(0 = 小端,1 = 大端)。

IRQ/FIQ 屏蔽位:控制中断响应。

七、ARM 指令

数据传送

MOV Rd, #const:立即数赋值。MOV Rd, Rm:寄存器传值。MVN Rd, #const:立即数取反。

算术运算

ADD Rd, Rn, #constSUB Rd, Rn, #constMUL Rd, Rn, Rm

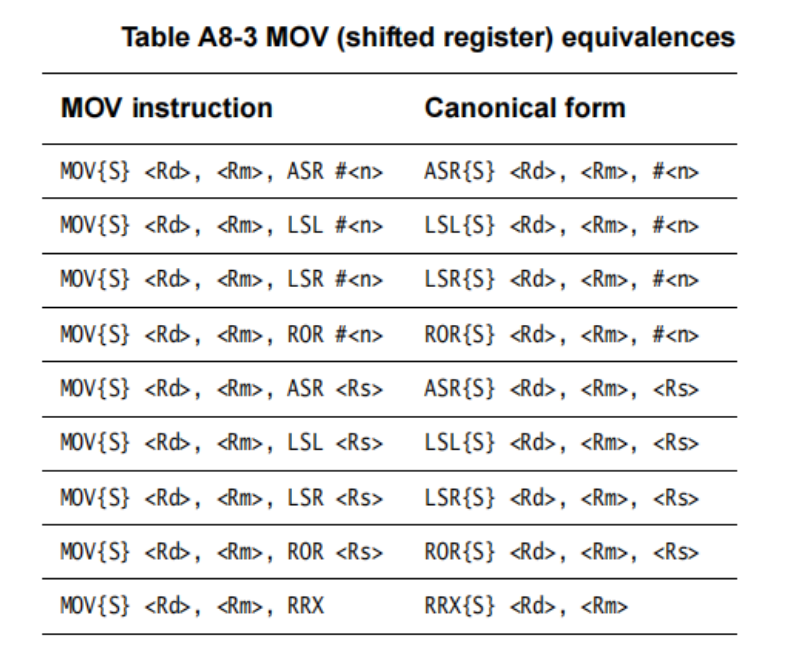

移位操作

LSL:逻辑左移。

LSR:逻辑右移。

ASL:算术左移(等价于 LSL)。

ASR:算术右移(符号位保持)。

ROR:循环右移。

立即数规则

ARM 立即数 = 8-bit 常数 + 4-bit 旋转。

可通过右旋实现更多常数表示。