*MOS 半导体功率器件简介 | 结构 / 制程 / 简史

注:本文为 “ * MOS” 相关合辑。

略作重排,未全校去重。

如有内容异常,请看原文。

BCD 工艺、CMOS 工艺、BiCMOS 工艺

模拟是个坑于 2020-06-05 18:46:07 发布

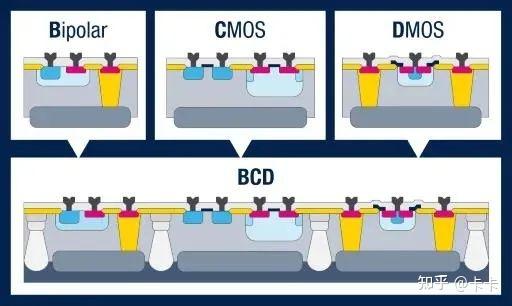

BCD 工艺:BCD 是一种单片集成工艺技术。1986 年由意法半导体(ST)公司率先研制成功,这种技术能够在同一芯片上制作双极管(bipolar)、CMOS 和 DMOS 器件,称为 BCD 工艺。

BCD 工艺技术的发展不像标准 CMOS 工艺那样,一直遵循 Moore 定律向更小线宽、更快的速度方向发展。BCD 工艺朝着三个方向分化发展:高压、高功率、高密度。

BCD 工艺集成了 Bipolar、CMOS 和 DMOS 器件,综合了高速、强负载驱动能力、集成度高和低功耗的优点,可提高系统性能,具有更好的可靠性。电子产品功能与日俱增,对于电压的变化、电容的保护和电池寿命的延长要求日益重要,而 BCD 所具备的高速节能的特点满足对高性能模拟/电源管理芯片的工艺需求。华虹 NEC 总裁刘文韬博士表示,“BCD 项目将进一步扩展丰富华虹 NEC 的工艺线,并且确立公司在模拟/电源管理领域的领先地位。”

CMOS 与 DMOS

Eren-Yu 已于 2024-06-17 16:14:34 修改

1. CMOS

CMOS(Complementary Metal Oxide Semiconductor, 互补金属氧化物半导体) 是把 NMOS 和 PMOS 制造在同一个芯片上组成集成电路。CMOS 工艺制程技术是利用互补对称电路来配置连接 PMOS 和 NMOS,从而形成逻辑电路。这个电路的静态功耗几乎接近为零,这一理论可以很好地解决功耗问题,为 CMOS 工艺制程技术的发展奠定了理论基础。

2. DMOS

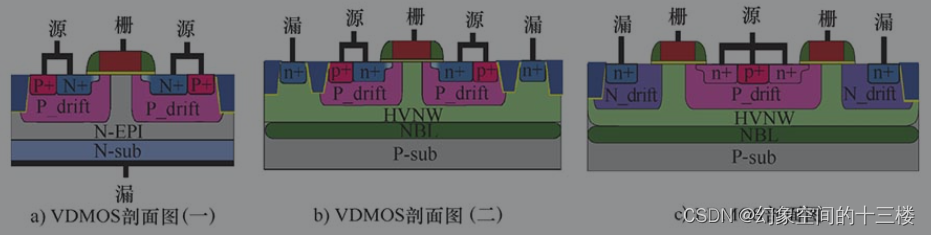

DMOS 与 CMOS 器件结构类似,也是由源、漏和栅组成,但 DMOS 器件的漏极击穿电压非常高。DMOS 器件主要有两种类型:一种是 VDMOS(Vertical Double Diffused MOSFET,垂直双扩散金属氧化物半导体场效应管),另一种是 LDMOS(Lateral Double Diffused MOSFET,横向双扩散金属氧化物半导体场效应管)。

3. 区别

3.1 构造

- CMOS:结构由 P 型和 N 型 MOSFET 组成。P 型 MOSFET 的源极和漏极都是 P 型半导体,体区是 N 型半导体;而 N 型 MOSFET 则正好相反。

- DMOS:结构则是一种 N 型 MOSFET,采用双扩散工艺,使得 N 型区域的掺杂浓度分布更加均匀,同时漏极和源极之间形成一个 P 型加强区。

3.2 工作原理

- CMOS:通过在 P 型和 N 型 MOSFET 之间交替组合,实现了电路的低功耗、高速度和高集成度。当输入信号为高电平时,只有 P 型 MOSFET 导通,而 N 型 MOSFET 截止,反之亦然。

- DMOS:是一种单极性结构,只有 N 型 MOSFET。其工作原理类似于普通的 MOSFET,但由于 P 型加强区的存在,DMOS 可以承受更高的电压和电流,因此被广泛应用于功率放大器和开关电源等领域。

3.3 应用

- CMOS:广泛应用于数字电路、微处理器、存储器等领域,因为它的功耗低、速度快、集成度高。

- DMOS:广泛应用于功率电子学领域,例如功率放大器、开关电源、马达驱动器等,因为它可以承受更高的电压和电流,同时具有较低的导通电阻和开关损耗。

newsDetail/3213)

BJT、CMOS、DMOS、BiCMOS 和 BCD 半导体制程技术简介

卡卡 发布于 2024-10-06 10:41・上海

随着半导体制程技术的不断突破,业界流传着一个被称为“摩尔定律”的著名论点。该论点由英特尔创始人之一戈登·摩尔于 1965 年提出,其核心内容为:集成电路上可以容纳的晶体管数目在大约每经过 18 个月到 24 个月便会增加一倍。摩尔定律不仅是对产业发展趋势的一种分析预测,同时也成了半导体制程发展的动力 —— 一切都是为了制造出更小尺寸且性能稳定的晶体管。从 20 世纪 50 年代至今约 70 年的时间,总共发展了 BJT、MOSFET、CMOS、DMOS 以及混合型的 BiCMOS 和 BCD 等制程技术。

1. BJT

双极性结型晶体管(Bipolar Junction Transistor,BJT),俗称三极管。晶体管中的电荷流动主要是由于载流子在 PN 结处的扩散作用和漂移运动,由于同时涉及电子和空穴两种载流子的流动,因此它被称为双极性元件。

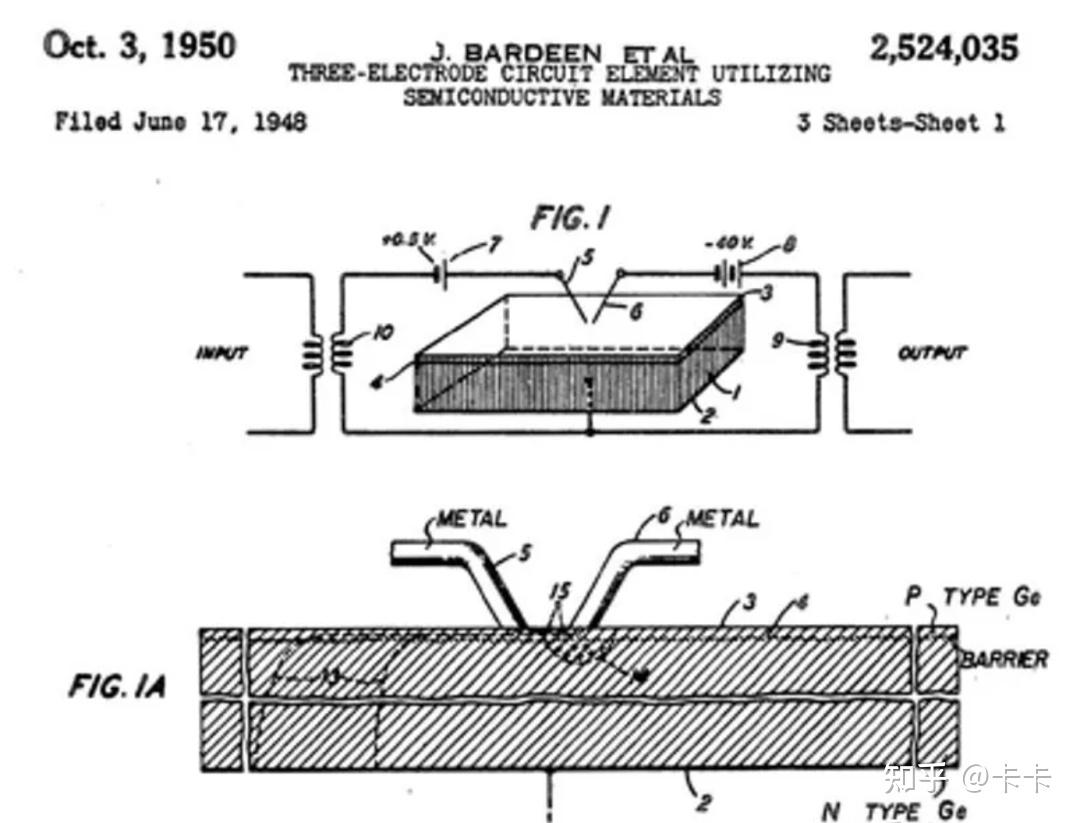

回顾其诞生的历史。由于存在着用固体放大器代替真空三极管这一想法,1945 年夏,肖克利(Shockley)提出开展半导体基础研究的建议。1945 年下半年,贝尔实验室成立了以肖克利为组长的固体物理学研究小组。该小组成员不仅包括物理学家,还有电路工程师和化学家,其中就有理论物理学家巴丁(Bardeen)和实验物理学家布拉顿(Brattain)。1947 年 12 月,一件被后世认为是里程碑式的事件发生了 —— 巴丁和布拉顿成功发明了世界上第一个具有电流放大作用的锗点接触晶体管。

巴丁和布拉顿的第一个点接触式晶体管

在此后不久,肖克利于 1948 年发明了双极结型晶体管。他提出了晶体管可以由两个 PN 结构成,一个正向偏置、另一个反向偏置,并在 1948 年 6 月取得了专利。1949 年,他将双极结型晶体管工作的详细理论发表了出来。两年多后,贝尔实验室的科学家和工程师开发出流程来实现双极结型晶体管的量产(1951 年为里程碑),开启了电子技术的新纪元。为了表彰在晶体管发明上的贡献,肖克利、巴丁和布拉顿共同获得了 1956 年诺贝尔物理学奖。

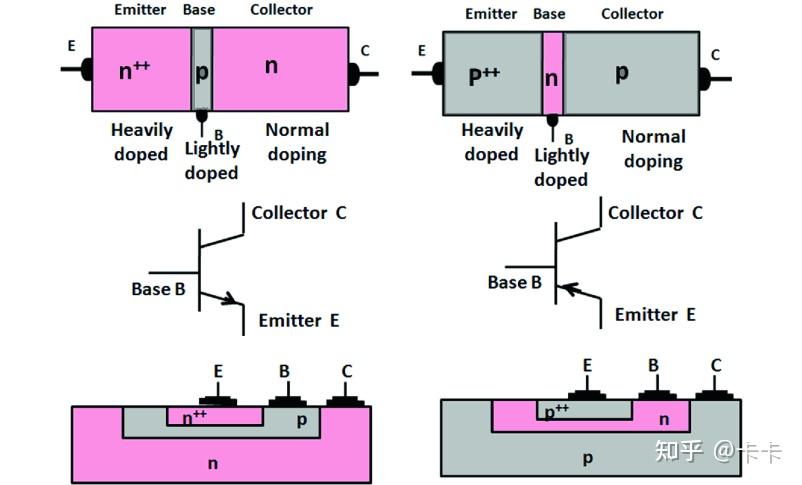

关于双极结型晶体管的结构,常见的 BJT 有 NPN 型和 PNP 型。

BJT 结构示意图及符号

其详细内部结构如下图所示。发射极对应的杂质半导体区域为发射区,该区域掺杂浓度较高;基极对应的杂质半导体区域为基区,该区域宽度很薄,掺杂浓度很低;集电极对应的杂质半导体区域为集电区,此区域面积大,掺杂浓度很低。

BJT 结构剖面图

BJT 技术的优点是高反应速度、高跨导(输入电压变化对应输出电流变化大)、低噪声、高模拟精度、强电流驱动能力;缺点是集成度低(纵向深度无法随横向尺寸缩小)、功耗高。

2. MOS

金属氧化物半导体场效应晶体管(Metal Oxide Semiconductor Field - Effect Transistor,MOSFET),即通过给金属层(M — 金属铝)的栅极和隔着氧化层(O — 绝缘层 SiO₂)的源极施加电压,产生电场的效应来控制半导体(S)导电通道开关的场效应晶体管。由于栅极与源极、栅极与漏极之间均采用 SiO₂绝缘层隔离,因此 MOSFET 又称为绝缘栅型场效应管。1962 年由贝尔实验室正式宣布成功开发,成为半导体发展史上最重要的里程碑之一,为半导体存储器的问世直接奠定了技术基础。

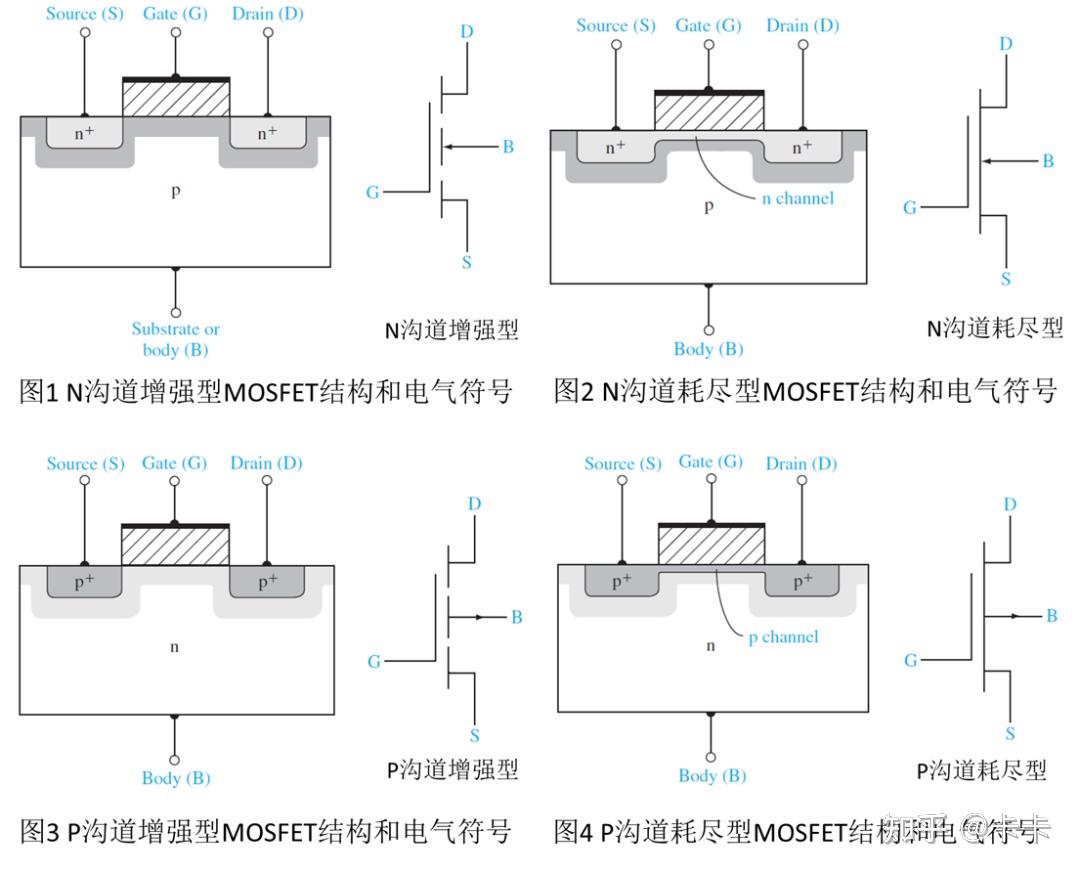

MOSFET 依导电通道类型可分为 P 通道和 N 通道。依栅极电压振幅可分为:

耗尽型 MOS — 当栅极电压为零时漏源极之间就存在导电通道;

增强型 MOS — 对于 N(P)通道元件,栅极电压大于(小于)零时才存在导电通道,功率 MOSFET 主要是 N 通道增强型。

MOS 结构示意图及符号

MOS 与三极管的主要区别包括但不限于以下几点:

- 三极管多子和少子同时参与导电,属于双极型元件;而 MOS 仅靠半导体中的多数载流子导电,又称为单极型晶体管。

- 三极管属于电流控制型元件,功耗比较高;而 MOSFET 属于电压控制型元件,功耗较小。

- 三极管导通电阻大,MOS 管导通电阻小,只有几百毫欧姆。在现在的用电器件上,通常会用 MOS 管做开关来用,主要是因为相对于三极管 MOS 的效率是比较高的。

- 成本上三极管就比较占优势,MOS 管相对价格较高。

在大部分场景下都是用 MOS 管取代三极管了,只有在一些小功率或对功耗不敏感的场景下,考虑到价格优势才会使用三极管。

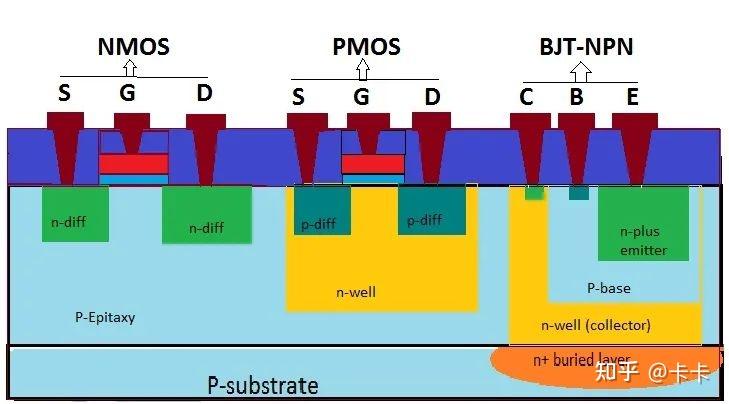

3. CMOS

互补型金属氧化物半导体(Complementary Metal Oxide Semiconductor,CMOS):CMOS 技术采用了互补的 P 型和 N 型金属氧化物半导体晶体管(MOSFET)来构建电子元件和逻辑电路。

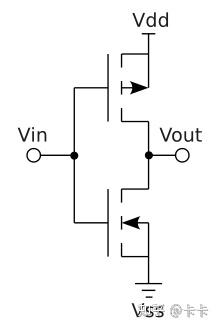

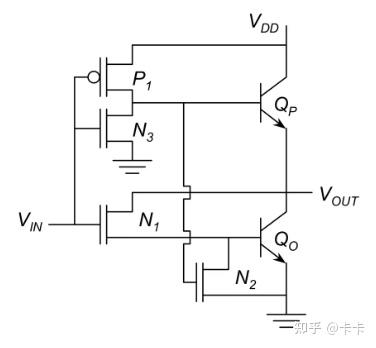

下图所示为常见的 CMOS 反相器,用于“1→0”或“0→1”的转换,典型电路图如下。

CMOS 电路图

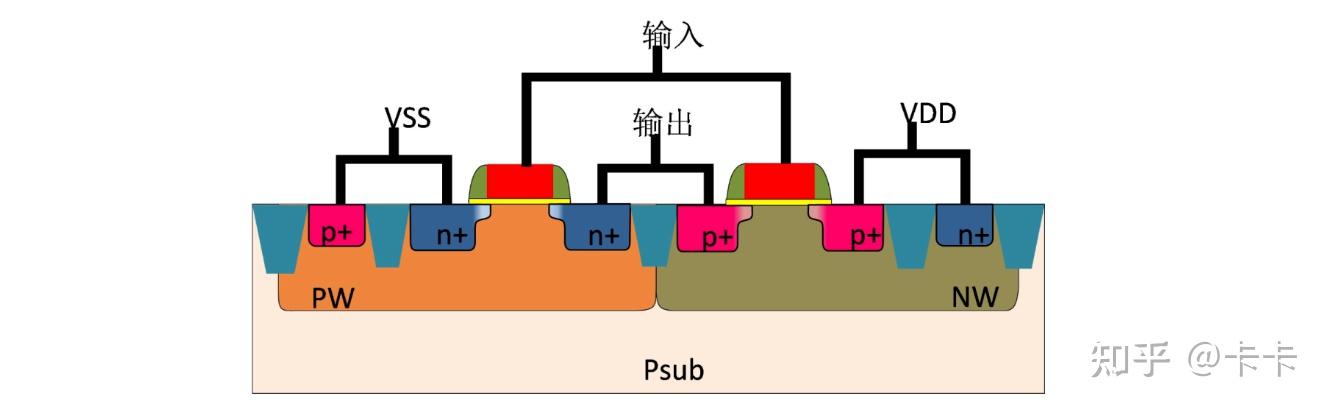

典型的 CMOS 剖面结构图如下,左边是 NMOS,右边是 PMOS,两个 MOS 的 G 极连在一起为共连栅极输入,D 极连在一起为共连漏极输出。VDD 接 PMOS 的源极,VSS 接 NMOS 的源极。

CMOS 结构剖面图

1963 年,仙童半导体公司的 Wanlass 和 Sah 发明了 CMOS 电路。1968 年,美国无线电公司(RCA)研发出第一个 CMOS 集成电路产品,此后 CMOS 电路获得了巨大的发展。它的优点是功耗低、高集成度(STI / LOCOS 制程可进一步提升集成度);缺点是存在锁定效应(MOS 管间采用 PN 结反偏作为隔离,受干扰易形成增强回路烧毁电路)。

CMOS 工艺目前已经发展到 3nm 的时代,目前基本上主要是数字电路在追求工艺节点。针对模拟电路为主或者数模混合电路居多的芯片,当前芯片主要分布在 180nm 到 28nm 之间。主要工艺节点有 180nm,130nm,110nm,90nm,65nm,55nm,40nm 和 28nm 等。如果电路中没有超高速转换器或者高速接口电路,基本 CMOS 工艺节点在 90nm 及以上比较多,65nm 及以下节点则更加适用于高速转换器,高速接口的电路中。CMOS 电路用于射频应用时,一般很难突破 6GHz 频率,超过 6GHz 之后,噪声和线性会快速下降。

更高的工艺节点有利于数字电路速度提高并且有效降低尺寸,但是也会带来漏电流变大,投片费用也较高。较低的工艺节点会限制运行速度,尺寸上也会比较大,但是漏电流更小,投片费用也更低。针对模拟电路,特别是数模混合电路而言,选择合适的工业节点是至关重要的。

4. DMOS、VDMOS 和 LDMOS

DMOS 器件是指双扩散金属氧化物半导体(Double - diffused Metal Oxide Semiconductor)器件,也被称为 VMOS(Vertical Metal Oxide Semiconductor)器件。DMOS 器件是一种用于功率放大和开关的半导体器件。

DMOS 器件的主要特点是具有低导通电阻、高电压承受能力、高速开关能力和高温性能等。由于这些特点,DMOS 器件广泛应用于功率放大、开关和 DC - DC 转换器等领域。

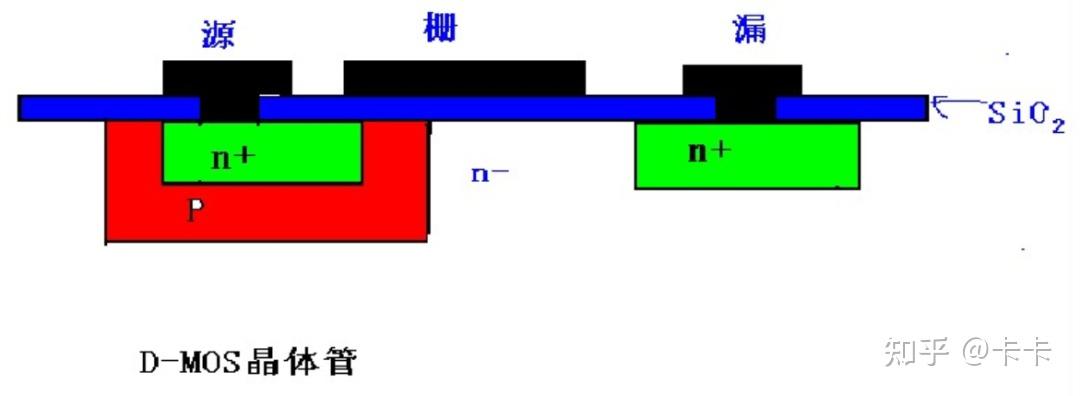

DMOS 器件的结构类似于 MOSFET(金属氧化物半导体场效应晶体管),但是在 DMOS 器件中,扩散区域比 MOSFET 更深,从而可以承受更高的电压。此外,DMOS 器件中的沟道是沿垂直方向延伸的,从而可以实现更高的电流密度和更低的导通电阻。

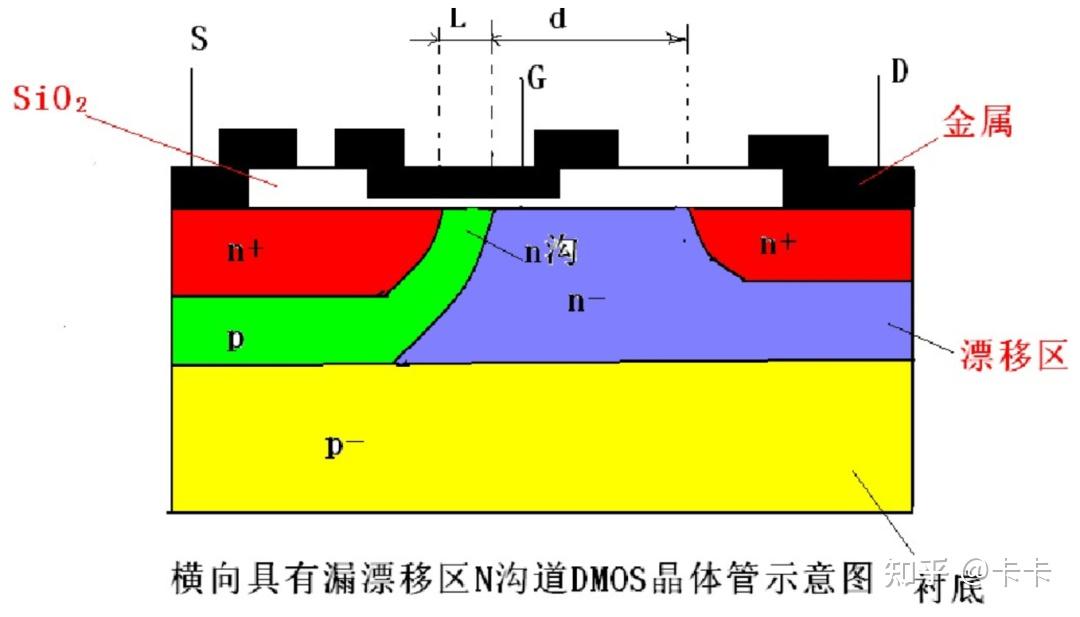

下图展示了标准 N 沟道的 DMOS 的剖面图,这种类型的 DMOS 元件通常用于开关应用,其中 MOSFET 的源极连接到接地。此外还有 P 沟道的 DMOS,这种类型的 DMOS 元件通常用于高侧开关应用,其中 MOSFET 的源极连接到正电压。类似 CMOS,互补 DMOS 元件在同一晶片上使用 N 通道和 P 通道 MOSFET 来提供互补的开关功能。

根据通道的方向,DMOS 可以分为两种类型,即垂直双扩散金属氧化物半导体场效应管 VDMOS(Vertical Double - Diffused MOSFET)和横向双扩散金属氧化物半导体场效应管 LDMOS(Lateral Double - Diffused MOSFET)。

VDMOS 元件设计有垂直通道,与横向 DMOS 元件相比它具有更高的击穿电压和电流处理能力,但是导通电阻仍然比较大。

LDMOS 元件设计有横向通道,是非对称功率 MOSFET 元件。与垂直 DMOS 元件相比,它允许更低的导通电阻和更快的开关速度。

DMOS 器件主要作用是在高功率电路中提供电流控制和开关控制功能。由于 DMOS 器件具有低导通电阻、高电压承受能力、高速开关能力和高温性能等优点,因此被广泛应用于各种功率电子应用中,如电源管理、电机驱动、照明控制、汽车电子、工业控制等。

- 在电源管理中,DMOS 通常用于 DC - DC 转换器、电源逆变器、电源管理单元等电路中,以实现高效率、高稳定性和高可靠性。

- 在电机驱动中,DMOS 通常用于马达控制器、电机驱动器等电路中,以实现高精度、高效率和高可靠性的马达控制。

- 在照明控制中,DMOS 还可以用于 LED 驱动器、照明调光器等电路中,以实现高效率、高亮度和高可靠性的照明控制。

- 在汽车电子和工业控制中,DMOS 通常用于电池管理、电力控制、电源变换、电机驱动、照明控制等电路中,以实现高稳定性、高安全性和高可靠性的控制功能。

不难发现,DMOS 器件的作用是在高功率电路中实现电流控制和开关控制功能,以提高电路的效率、稳定性和可靠性。

5. BiCMOS

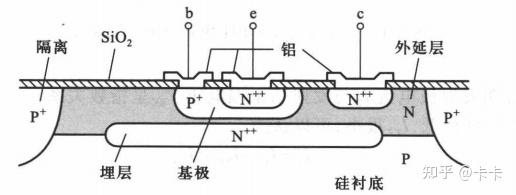

BiCMOS 就是 CMOS 和 Bipolar 的混合,即在 CMOS 的基础上生长 Bipolar。由于 Bipolar 可以做到非常低的漏电电流和噪声,针对数模混合电路,特别是低噪声或者低偏移的数模混合电路,使用 BiCMOS 即可以发挥 CMOS 的低功耗优势,又可以兼顾模拟高性能特性。

将双极型晶体管(BJT)和 CMOS 器件同时集成在同一块芯片上的新型工艺技术,它集中了上述单、双极型器件的优点,两者“交叉”结合,取长补短,调和折衷,为发展我国高速、高性能的各种通信、信息处理和网络电路、通信用模拟 / 数字混合微电子电路和数字通信用超大规模集成电路(数字通信 VLSI)开辟了一条崭新的道路。

CMOS 工艺和 Bipolar 工艺是两种主要的硅集成电路工艺,它们有各自的优点。CMOS 器件有集成度高、功耗低、输入阻抗高等优点。Bipolar 器件有截止频率高、驱动能力大、速度快、噪声低等优点。它们的优缺点正好互相补充,将它们集成同一芯片上形成 BiCMOS 工艺,制得的器件性能定将超出单一工艺。

形成 BiCMOS 工艺的方案现有很多,大致可归纳为两大类:一类是以 CMOS 工艺为基础,另一类是以 Bipolar 工艺为基础。采用原有的 2um N 阱 CMOS 工艺基础上选用双埋层、双阱、外延结构来形成 BiCMOS 工艺。

BiCMOS,BiCMOS = Bipolar + CMOS,一般有两种类型的 BiCMOS,一种是以 Bipolar 工艺为基础,将 CMOS 加入到 Bipolar 工艺中,这种 BiCMOS 工艺的器件特性以 Bipolar 器件为主,CMOS 器件为辅,CMOS 器件特性并不是最佳,Bipolar 器件特性可以达到很好的程度;另一种以 CMOS 器件为主,Bipolar 器件为辅,CMOS 器件特性可以达到比较好的程度,Bipolar 特性一般,简单的甚至直接只是加一个 Base 区域,Bipolar 器件只是起到最基本的作用,比如做 bandgap 用,提供一个参考电压。两种 BiCMOS 工艺不论侧重点如何,只要满足设计的需求即可,在这个客户导向的时代,只要你能给代工厂足够的订单,代工厂就能拿出足够诚意来满足客户的各种需求。

下图是一个 BiCMOS 的反相器原理图,输出端口使用了 BJT 的对管,主要逻辑部分都是 MOS 管。

BiCMOS 反相器原理图

BiCMOS 结构剖面图

BiCMOS 可在单颗芯片上融合两种不同工艺技术的优势:双极晶体管可达到较高的速度和增益,满足高频模拟部分的要求,而 CMOS 技术则非常适合构成简单的低功耗门逻辑电路。意法半导体的 BiCMOS SiGe(硅锗)技术将射频、模拟和数字部分集成在单颗芯片上,能够大幅减少外部元器件的数量,同时优化功耗。

6. BCD

Bipolar - CMOS - DMOS,这种技术能够在同一晶片上制作双极管 Bipolar,CMOS 和 DMOS 元件,称为 BCD 工艺,1986 年由意法半导体(ST)率先开发成功。

Bipolar 适用于精密的模拟电路,CMOS 适用于大规模数字逻辑电路,DMOS 适用于功率和高压元件。BCD 则结合了三者的优点。

BCD 工艺广泛使用在电源,电池检测,LED 驱动等高压电路中。目前 BCD 工艺主要工艺节点有 0.25um,0.18um,130nm,90nm 和 55nm。耐压等级根据应用不同,最低为 5V,其次是 12V,40V,60V,80V,120V,最高达到 6KV 等。BCD 除了不断提高工艺的制程和耐压等级之外,通过结构改善如 DTI(Deep Trench Isolation,深沟槽隔离)降低尺寸,也通过 SOI(Silicon - on - Insulator,绝缘体上硅)工艺提高隔离等级降低尺寸。

ST 公司是 BCD 工艺的发明者,从 ST 官网数据可以看出,ST 的 BCD 工艺已经发展到 90nm(100V),最高耐压到 6KV,发展到第 9 代,工艺涉及到 SOI 和 DTI 等。其他厂商如 TI 的 BCD 工艺已经支撑 110nm(85V)耐压,采用 DTI 实现。NXP 主要基于 SOI 的 BCD 工艺上开发汽车电源类和音频功放等产品。晶圆代工厂中,TSMC,TOWER,Global Foundries,SMIC 和华虹都有开发 BCD 工艺。

7. 参考说明

-

BJT、CMOS、DMOS 等半导体制程技术

https://hao.cnyes.com/post/75758 -

BiCMOS - Best of Both Worlds? - Bicoms | PDF

https://www.slideshare.net/slideshow/bicoms/247086190 -

半导体工艺与工厂 - 工艺篇 - 行业资讯 - 昆山润石智能科技有限公司

https://www.aie-tec.com/%3Fnews_7/763.html -

【万字干货】一文详述半导体工艺与分类-电子工程专辑

https://www.eet-china.com/mp/a295656.html -

[什么是 DMOS?DMOS 器件工作原理和工艺流程介绍 - IC 先生

https://www.mrchip.cn/newsDetail/3213

DMOS 算法介绍及算法原理

mazhitong1227 于 2017-08-02 14:22:43 发布

1. 图像质量评价方法概述

图像质量评价主要分为两类:主观评价方法和客观评价方法。

1.1 主观评价方法

主观评价由观察者对图像质量进行主观评分,通常采用以下两种方式表示:

- 平均主观得分(Mean Opinion Score, MOS):观察者对图像质量的整体评分。

- 平均主观得分差(Differential Mean Opinion Score, DMOS):人眼对无失真图像和有失真图像评价得分的差异。

然而,主观评价存在明显的不足:

- 工作量大:需要大量人力对图像质量进行评分。

- 耗时长:评价过程耗时,尤其当图像数量巨大时。

- 受主观因素影响:评价结果容易受到个人主观因素的影响,缺乏客观性。

1.2 客观评价方法

客观评价方法则是由计算机根据一定算法计算得到图像的质量指标。根据评价时是否需要参考图像,客观评价方法可以分为以下三类:

-

全参考(Full Reference, FR):在评价失真图像时,需要提供一个无失真的原始图像,通过对二者的比对,得到对失真图像的评价结果。常见的评价指标包括:

- 信噪比(Signal-to-Noise Ratio, SNR)

- 峰值信噪比(Peak Signal-to-Noise Ratio, PSNR)

- 均方误差(Mean Square Error, MSE)

- 平均结构相似度(Mean Structural Similarity, MSSIM)

- 视觉信息保真度(Visual Information Fidelity, VIF)

- 视觉信噪比(Visual Signal-to-Noise Ratio, VSPR)

- 最显著失真(Most Apparent Distortion, MAD)

- 图像差异预测(Image Difference Prediction, IDP)

-

半参考(Reduced Reference, RR):仅需要部分参考图像信息进行评价。

-

无参考(No Reference, NR):不需要任何参考图像,直接对失真图像进行评价。

1.3 客观评价方法的优缺点

随着研究的发展,全参考方法的准确性越来越高,但其缺点是需要提供无失真的参考图像,这在实际应用中往往很难得到。

2. 算法评价标准

通常以算法评价值和人眼主观打分值(MOS 或 DMOS)的误差和相关性来进行评价。MOS 值越大(DMOS 值越小),说明图像质量越高;相反,MOS 值越小(DMOS 值越大),说明图像质量越差。算法评价值与 MOS 或 DMOS 的误差越小、相关性越强,说明评价越准确。

3. DMOS 算法介绍

3.1 DMOS 计算

平均主观得分差(DMOS)是建立在平均主观分值法(MOS)分值基础上的,其计算公式如下:

di,j=MOSoriginal−MOSdistortedd_{i,j} = \text{MOS}_{\text{original}} - \text{MOS}_{\text{distorted}}di,j=MOSoriginal−MOSdistorted

di,j′=di,j−min(di,j)max(di,j)−min(di,j)d'_{i,j} = \frac{d_{i,j} - \min(d_{i,j})}{\max(d_{i,j}) - \min(d_{i,j})}di,j′=max(di,j)−min(di,j)di,j−min(di,j)

这里,di,jd_{i,j}di,j 代表观测者对于参考图像和失真图像评分的差异值。最后对 di,j′d'_{i,j}di,j′ 取平均值,可以得到 DMOS 值。

主观评价算法也有很大的不足之处。首先,需组织人力对图像质量进行评价,评价结果很容易受到个人主观因素的影响,并且当图像数量巨大时,该方法就更为耗费时间,因此不利于在工程实践中的应用;其次,该方法不能自动实现,不能嵌入实际的图像或视频处理系统中,比如流媒体播放、视频会议等。但是为了评测客观图像质量评价算法,仍然需要用到主观评价算法的辅助,所以对于主观评价算法的介绍也是很有必要的。

[笔记] A Brief History of the MOS transistor, MOS 晶体管简史

杨正瓴 2025-5-7 22:33

Steve Leibson

- An Interview with Steve Leibson - Impavid Ideopraxist Insider

https://theamphour.com/the-amp-hour-99-impavid-ideopraxist-insider/

Part 1: Early Visionaries

https://www.eejournal.com/article/a-brief-history-of-the-mos-transistor-part-1-early-visionaries/

In 1939, Shockley wrote: “It has today occurred to me that an amplifier using semiconductors rather than vacuum is in principle possible.” Shockley appears to have been unaware of the earlier patents granted to Lilienfeld and Heil.

1939 年,肖克利写道:“今天我突然想到,原则上使用半导体而不是真空的放大器是可能的。” 肖克利似乎不知道 Lilienfeld 和 Heil 之前获得的专利。

When Bell Labs announced the junction transistor in 1951, it quickly became the dominant transistor in the industry because it was superior in every way to the original point-contact device. However, it was still a bipolar transistor and not a MOSFET.

当贝尔实验室于 1951 年宣布推出结型晶体管时,它迅速成为行业中的主导晶体管,因为它在各个方面都优于最初的点接触器件。然而,它仍然是双极晶体管,而不是 MOSFET。

Significantly, the Bell Labs practice was to remove the silicon dioxide layer after diffusion because it was considered “dirty,” as in “laced with contaminants.” Two months after the Frosch and Derick article appeared, Jean Hoerni at Fairchild Semiconductor realized that the silicon dioxide layer was important for several reasons and that it should be left in place. A pure silicon dioxide layer became an integral part of Hoerni’s planar manufacturing process and would be a key element of IC manufacturing.

值得注意的是,贝尔实验室的做法是在扩散后去除二氧化硅层,因为它被认为是 “脏的”,就像 “夹杂着污染物” 一样。在 Frosch 和 Derick 的文章发表两个月后,Fairchild Semiconductor 的 Jean Hoerni 意识到二氧化硅层的重要性有几个原因,应该留在原地。纯二氧化硅层成为 Hoerni 平面制造工艺不可或缺的一部分,并将成为 IC 制造的关键要素。

Atalla further refined this discovery into a more formal silicon dioxide passivation technology that permitted the silicon to be doped far more precisely in specific locations when coupled with newly developed photolithographic and etching techniques. Using this technology, Atalla and Kahng managed to build a working MOSFET by the beginning of 1960, three decades after Lilienfeld first conceived of the device. Although the device worked, after a fashion, this first MOSFET had several problems. Notably, it was 100 times slower than contemporary bipolar transistors, mainly because of its relatively large channel length of 20 µm.

Atalla 进一步将这一发现改进为一种更正式的二氧化硅钝化技术,当与新开发的光刻和蚀刻技术结合时,该技术允许硅在特定位置更精确地掺杂。使用这项技术,Atalla 和 Kahong 在 1960 年初成功构建了一个工作的MOSFET,这是 Lilienfeld 首次构思该器件的三十年后。尽管该器件工作正常,但在某种程度上,第一个 MOSFET 存在几个问题。值得注意的是,它比当代双极晶体管慢 100 倍,主要是因为其 20µm 的相对较大的沟道长度。

Part 2: Fairchild – The Big Engine that Couldn’t

Shockley’s autocratic management style and ego fractured his team, causing a showdown on May 29, 1957. The research team’s demand was for the “Shockley Problem” to be solved. It wasn’t, and eight members of Shockley’s research team – which became known as the Traitorous Eight – left in September 1957. That core group cut a deal with Sherman Fairchild and founded Fairchild Semiconductor on October 1, 1957.

肖克利的专制管理风格和自我意识使他的团队四分五裂,导致 1957 年 5 月 29 日的摊牌。研究小组的要求是解决 “肖克利问题”。事实并非如此,肖克利研究小组的八名成员 —— 后来被称为叛徒八人组(八叛逆)—— 于 1957 年 9 月离开。该核心小组与 Sherman Fairchild 达成协议,于 1957 年 10 月 1 日成立了 Fairchild Semiconductor。

Bell Labs thought this oxide was too dirty to leave in place but Hoerni realized that a sufficiently clean insulating layer would prevent contamination from dust, dirt, and water. With few changes, Hoerni filed for a patent on the planar process on January 14, 1959.

The second important step towards the semiconductor breakthrough that was needed to allow MOSFETs to achieve their destiny occurred on January 23, 1959. That was the day that Fairchild Semiconductor’s founder Robert Noyce wrote down the ideas for a monolithic integrated circuit in his lab notebook. He’d been spurred to think of ways to use Hoerni’s planar process to make more than discrete transistors. He realized that the silicon dioxide layer was a perfect insulator and allowed metal interconnect to be deposited on top to complete the connections among multiple devices on the IC. With that flash of insight, Noyce changed the electronics industry forever and transformed soldering and wiring into a high-tech printing process.

贝尔实验室认为这种氧化物太脏了,不能留在原地,但霍尼意识到,一个足够干净的绝缘层可以防止灰尘、污垢和水的污染。几乎没有什么变化,霍尼于 1959 年 1 月 14 日申请了平面工艺的专利。

1959 年 1 月 23 日,MOSFET 实现其命运所需的半导体突破的第二个重要步骤发生了。就在那天,飞兆半导体的创始人罗伯特・诺伊斯在他的实验室笔记本上写下了单片集成电路的想法。他一直在思考如何利用霍尼的平面工艺制造出不仅仅是分立晶体管。他意识到二氧化硅层是一种完美的绝缘体,允许在顶部沉积金属互连,以完成 IC 上多个器件之间的连接。凭借这一瞬间的洞察力,诺伊斯永远改变了电子行业,将焊接和布线转变为高科技印刷工艺。

In February, 1963, Wanlass and his manager C.T. Sah presented a paper at ISSCC that revealed that Wanlass had conceived of circuits that combined p- and n-channel MOSFETs on the same IC. He’d invented CMOS as a mere byproduct of his work.

1963 年 2 月,Wanlass 和他的经理 C.T.Sah 在 ISSCC 上发表了一篇论文,揭示了 Wanlass 已经构思出将 p 沟道和 n 沟道 MOSFET 组合在同一 IC 上的电路。他发明 CMOS 只是他工作的副产品。

Part 3: Frank Wanlass – MOS Evangelist, Inventor of CMOS

It’s hardly surprising that semiconductor companies were reluctant to invest much energy into MOSFET development in the early 1960s. Early MOSFETs were 100 times slower than bipolar transistors, and they were considered unstable, for good reason: their electrical characteristics drifted badly and unpredictably with time and temperature. A lot of research and development work would be needed to transform MOSFETs into reliable electronic components.

毫不奇怪,在 20 世纪 60 年代初,半导体公司不愿意在 MOSFET 的开发上投入太多精力。早期的 MOSFET 比双极晶体管慢 100 倍,并且它们被认为是不稳定的,这是有充分理由的:它们的电特性随着时间和温度的变化而严重漂移,且不可预测。将 MOSFET 转化为可靠的电子元件需要大量的研究和开发工作。

Along the way, Wanlass and his manager C.T. Sah patented the idea for CMOS circuits, which combine p- and n-channel MOSFETs on one silicon die. CMOS is the foundational transistor technology for nearly every IC now manufactured. (Note: Sah is often listed as the sole inventor of CMOS, but his name is on the patent because he was Wanlass’s manager, and it was customary to list the manager along with the inventor on the patent application.)

在此过程中,Wanlass 和他的经理 C.T.Sah 为CMOS 电路的想法申请了专利,该电路将 p 沟道和 n 沟道 MOSFET 结合在一个硅管芯上。CMOS 是目前制造的几乎所有 IC 的基础晶体管技术。(注:Sah 通常被列为 CMOS 的唯一发明人,但他的名字出现在专利上,因为他是 Wanlass 的经理,通常在专利申请中会将经理和发明人一起列出。)

In an interview, Wanlass said, “I was driving down the 101 freeway one day, on a Sunday, and it hit me. It’s got to be sodium, and I had sent out some aluminum wire to be spectroscopic analyzed. I knew from my college work, some of my thesis work, that sodium… I knew for a fact that sodium, with just a little help from temperature and voltage, would diffuse right through quartz. It had a very high diffusion quotient. I knew that. That was from experiments in college.”

在一次采访中,Wanlass 说:“有一天,在一个星期天,我在 101 高速公路上开车,它撞到了我。它一定是钠,我送了一些铝线进行光谱分析。我从我的大学工作,我的一些论文工作中知道钠…… 我知道一个事实,即钠在温度和电压的帮助下,会直接通过石英扩散。它有很高的扩散系数。我知道。这是从大学的实验中知道的。”

Eventually, the industry would understand that sodium ion contamination causes drift and kills p-channel MOSFETs over time, while making it impossible to build working n-channel MOSFETs. The aluminum was being contaminated with sodium when it was drawn through wire dies to make the aluminum wire that served as the feed stock for the vapor deposition. The wire dies were lubricated with sodium. Electron-beam vaporization employs a shutter mechanism that shields the wafers from the crucible of molten aluminum until the aluminum reaches its evaporation temperature. Sodium has a much lower boiling point than aluminum, so the sodium boiled off and dissipated before the shutter in the evaporation chamber opened and exposed the wafer to the aluminum vapor.

最终,业界会明白,钠离子污染会导致漂移,并随着时间的推移杀死 p 沟道 MOSFET,同时使其无法构建工作的 n 沟道 MOSFET。当铝被拉过线材模具以制造用作气相沉积原料的铝线时,铝被钠污染了。金属丝模具用钠润滑。电子束蒸发采用一种快门机制,将晶片与熔融铝的坩埚隔开,直到铝达到其蒸发温度。钠的沸点比铝低得多,因此钠在蒸发室中的闸门打开并将晶片暴露于铝蒸气之前沸腾并消散。

Part 4: IBM Research, Persistence, and the Technology No One Wanted

IBM’s bipolar transistor problem was one of reliability. Some of the transistors in its SLT devices would fail due to electrical leakage, and CD’s work on the problem uncovered the culprit and the solution. The culprit was sodium, and the solution was phosphorus. By 1964, IBM had discovered that adding trace amounts of phosphorus to the silicon dioxide layer in the planar process, the phosphorus bonds with the sodium and prevents it from descending into and poisoning the silicon below. A further development determined that applying a negative voltage to the silicon substrate further alleviated the problem of sodium contamination by increasing the MOSFET’s threshold voltages.

IBM 的双极晶体管问题是可靠性问题。其 SLT 器件中的一些晶体管会因漏电而发生故障,CD 在这个问题上的工作揭示了罪魁祸首和解决方案。罪魁祸首是钠,溶液是磷。到 1964 年,IBM 发现,在平面工艺中向二氧化硅层中添加微量磷,磷会与钠结合,防止其落入下方的硅中并中毒。进一步的发展确定,通过增加 MOSFET 的阈值电压,向硅基板施加负电压进一步缓解了钠污染的问题。

IBM’s systems development group in Poughkeepsie then identified the perfect vehicle for MOS ICs: memory. The competing memory technology, magnetic cores, was incredibly slow. Magnetic memory’s access and cycle times were on the order of microseconds. MOS memory ICs would be faster than that. In addition, the use of MOS memory ICs could significantly cut memory’s cost per bit while speeding access times.

IBM 位于波基普西的系统开发团队随后确定了 MOS IC 的完美载体:内存。与之竞争的内存技术,磁芯,速度慢得令人难以置信。磁存储器的访问和循环时间大约为微秒。MOS 存储器 IC 将比这更快。此外,使用 MOS 存储 IC 可以显著降低存储器的每比特成本,同时加快访问时间。

Currently, IBM Research has developed a 2nm MOS process technology and is in partnership with Rapidus in Japan to commercialize the process. The history of IBM Research’s involvement with MOSFETs is nearly synonymous with the MOSFET’s history, and IBM Research’s work was clearly instrumental in finding a home for MOSFETs, the technology that no one wanted.

目前,IBM Research 已经开发出一种 2nm MOS 工艺技术,并与日本 Rapidus 合作将该工艺商业化。IBM Research 参与 MOSFET 的历史几乎与 MOSFET 的历史同义,IBM Research 的工作显然有助于为 MOSFET 找到一个家,这是一种没有人想要的技术。

Part 5: RCA – The Persistent CMOS Contrarian

RCA Labs also started developing “integrated semiconductor devices,” ICs, during this period. It appears that RCA Labs was well on its way to developing ICs before Texas Instruments (TI) and Fairchild but apparently failed to build fully functional devices. RCA Labs then took a wrong turn and started looking at Shockley’s unipolar transistor as a candidate for making ICs. That work turned out to be a dead end.

在此期间,RCA 实验室也开始开发 “集成半导体器件” IC。看起来,RCA 实验室在德州仪器(TI)和飞兆半导体(Fairchild)之前就已经在开发 IC,但显然未能制造出功能齐全的设备。RCA 实验室随后误入歧途,开始将肖克利的单极晶体管视为制造 IC 的候选者。那项工作最终被证明是一条死胡同。

Throughout the 1970s, RCA was the only major semiconductor company to stick with CMOS, or COSMOS, because CMOS circuits were still slow when compared with both bipolar and NMOS ICs. Most projects called for speed. By the middle of the 1970s, PMOS devices had fallen by the wayside and NMOS was the new MOS king. Ultimately, however, RCA would prove to have been right all along, because CMOS got fast.

在整个 20 世纪 70 年代,RCA 是唯一一家坚持使用 CMOS 或 COSMOS 的大型半导体公司,因为与双极型和 NMOS IC 相比,CMOS 电路仍然很慢。大多数项目都要求速度。到 20 世纪 70 年代中期,PMOS 器件已经半途而废,NMOS 成为新的 MOS 之王。然而,最终,RCA 将被证明一直是正确的,因为 CMOS 发展得很快。

Hitachi’s Central Research Laboratories made a breakthrough when Yoshio Sakai and Toshiaki Masuhara developed twin-well CMOS, which cured CMOS of its speed handicap. Makimoto and his group adopted the twin-well CMOS process and took aim at Intel’s fastest static RAM (SRAM): the NMOS, 4-kbit 2147 SRAM. Intel’s 2147 memory had a minimum access time of 55 nsec and consumed 115 milliamps.

当酒井义雄和 Toshiaki Masuhara 开发出双井 CMOS 时,日立中央研究实验室取得了突破,解决了CMOS 的速度障碍。Makimoto 和他的团队采用了双井 CMOS 工艺,并瞄准了英特尔最快的静态 RAM(SRAM):NMOS,4-kbit 2147 SRAM。英特尔的 2147 存储器的最小访问时间为 55 纳秒,消耗 115 毫安。

These two Hitachi CMOS SRAMs were big sellers and they electrified Hitachi’s competitors in the semiconductor industry by proving that low-power CMOS ICs could also be fast. Within a few years, thanks to RCA’s persistence and Hitachi’s innovative process, NMOS joined PMOS on the ever-growing heap of obsolete semiconductor technologies, and CMOS became the king of the hill.

这两款日立 CMOS SRAM 是畅销产品,它们通过证明低功耗 CMOS IC 也可以很快,使日立在半导体行业的竞争对手感到振奋。几年内,由于 RCA 的坚持和日立的创新工艺,NMOS 加入了 PMOS 不断增长的过时半导体技术堆,CMOS 成为了王者。

参考资料:

[1] Steven Leibson. 2023-04-03, A Brief History of the MOS transistor, Part 1: Early Visionaries

https://www.eejournal.com/article/a-brief-history-of-the-mos-transistor-part-1-early-visionaries/

[2] Steven Leibson, 2023-04-05, A Brief History of the MOS transistor, Part 2: Fairchild – The Big Engine that Couldn’t

https://www.eejournal.com/article/a-brief-history-of-the-mos-transistor-part-2-fairchild-the-big-engine-that-couldnt/

[3] Steven Leibson, 2023-04-10, A Brief History of the MOS transistor, Part 3: Frank Wanlass – MOS Evangelist, Inventor of CMOS

https://www.eejournal.com/article/a-brief-history-of-the-mos-transistor-part-3-frank-wanlass-mos-evangelist-inventor-of-cmos/

[4] Steven Leibson, 2023-04-17, A Brief History of the MOS transistor, Part 4: IBM Research, Persistence, and the Technology No One Wanted

https://www.eejournal.com/article/a-brief-history-of-the-mos-transistor-part-4-ibm-research-persistence-and-the-technology-no-one-wanted/

[5] Steven Leibson, 2023-04-24, A Brief History of the MOS transistor, Part 5: RCA – The Persistent CMOS Contrarian

https://www.eejournal.com/article/a-brief-history-of-the-mos-transistor-part-5-rca-the-persistent-cmos-contrarian/

[6] Electronics Timeline, 20th century’s greatest engineering achievements

http://www.greatachievements.org/?id=3956

[7] Greatest Engineering Achievements of the 20th Century

http://www.greatachievements.org/

[8] Computer History Museum, TIMELINES

https://computerhistory.org/

https://computerhistory.org/timelines/

[9] Computer History Museum,

https://computerhistory.org/timelines/

https://www.computerhistory.org/siliconengine/

[10] Computer History Museum, Timeline of Computer History

https://computerhistory.org/timelines/

https://www.computerhistory.org/timeline/

相关链接:

[1] 2025-01-04 19:40,电子学(1):硬件(晶体管、集成电路、等)相关博文目录

https://blog.sciencenet.cn/blog-107667-1467362.html

[2] 2023-09-06 21:55,[小资料] 1963 年万拉斯(Frank Wanlass)、萨支唐(Chih-Tang Sah)申请的 CMOS 专利和论文

https://blog.sciencenet.cn/blog-107667-1401741.html

[3] 2023-09-05,[小资料] 1963 年霍夫施泰因(Steven Hofstein)、海曼(Frederic Heiman)的 MOS 场效应

https://blog.sciencenet.cn/blog-107667-1401577.html

[4] 2023-09-04,[小资料] 1960 年阿塔拉(Martin Atalla)、江大原(Dawon Kahng)申请的 MOS 场效应管专利(图

https://blog.sciencenet.cn/blog-107667-1401453.html

[5] 2023-09-03,[小资料] 1922~23 年洛舍夫(Oleg Vladimirovich Losev)发现固体放大作用

https://blog.sciencenet.cn/blog-107667-1401338.html

[6] 2023-09-02,[小资料] 1935 年海尔(Oskar Heil)的场效应管专利(图片)

https://blog.sciencenet.cn/blog-107667-1401242.html

[7] 2023-09-01,[小资料] 1926 年利林费尔德(Julius Edgar Lilienfeld)的场效应半导体专利(图片)

https://blog.sciencenet.cn/blog-107667-1401136.html

*MOS 技术发展

一、早期奠基阶段(1960 年代 - 1980 年代):功率 MOSFET 基础结构成型

此阶段的核心是解决传统 MOSFET 在功率应用中的局限性,逐步形成垂直 / 横向导电的基础功率结构,为后续技术迭代奠定框架。

- 传统 MOSFET(1960 年代)

金属 - 氧化物 - 半导体场效应晶体管(MOSFET)的基础结构实现实用化,首次实现“栅极电压控制沟道导电”,是所有 MOSFET 衍生结构的理论与技术源头,开启了场效应晶体管的应用时代。 - VMOS(V 型槽 MOSFET,1970 年代中期)

针对传统 MOSFET 电流密度低、导通电阻大的问题,创新性地采用“V 型槽”垂直导电结构,缩短电流路径,提升功率承载能力。它是首款功率 MOSFET 结构之一,推动 MOSFET 应用于中低功率领域。 - DMOS(双重扩散 MOSFET,1970 年代末 - 1980 年代初)

优化了 VMOS 工艺复杂、良率低的缺陷,通过双重扩散工艺形成短沟道。其结构简化且成本降低,同时保留了垂直导电的高功率特性,迅速成为主流,广泛用于电机驱动、电源管理等领域。

二、技术分化与拓展阶段(1980 年代中期 - 1990 年代):场景化结构与集成工艺突破

此阶段围绕“高频”“低压大电流”“工艺集成”三大需求,形成多分支技术路线,MOSFET 从单一功率器件向“结构定制化 + 工艺集成化”演进。

- LDMOS(横向扩散 MOSFET,1980 年代中期)

针对射频(RF)、微波等高频大功率场景,创新采用“横向导电”结构,在硅衬底上实现高击穿电压,同时兼顾高频信号处理能力,弥补了 DMOS 高频性能不足。它成为射频功率器件的关键技术,至今仍在通信领域广泛应用。 - 沟槽型 MOSFET(Trench MOSFET,1980 年代末 - 1990 年代初)

聚焦低压大电流场景,通过沟槽刻蚀工艺将栅极嵌入硅片,增大了栅极对沟道的控制面积,同时减小了芯片体积,降低导通电阻、提升电流密度。这推动了便携式电子设备的电源小型化。 - BiCMOS(双极 - CMOS 集成工艺,1990 年代中期)

这并非单一 MOSFET 结构,而是“双极晶体管(BJT)+ CMOS(互补 MOS)”的工艺集成技术。它将功耗低的 CMOS 与驱动能力强的 BJT 优势融合,通过精细化工艺实现,主要用于高性能模拟电路、射频前端,标志着 MOSFET 从“单一器件”向“系统级工艺”跨越。

三、前沿创新阶段(1990 年代末 - 至今):材料、结构与封装的全方位突破

此阶段核心是突破硅基材料极限,通过新结构、宽禁带材料、先进封装,满足“高压低损耗”“高频高效”“极致微型化”等高端需求,覆盖新能源、5G、AI 等新兴领域。

- 超结 MOSFET(1998 年,以英飞凌 CoolMOS 为代表)

这是硅基功率 MOSFET 的一项里程碑突破:在 N-漂移区交替制造高掺杂 P 型柱与 N 型柱,形成周期性 PN 结。在相同耐压下,N 柱掺杂浓度比传统 DMOS 高,导通损耗与开关损耗大幅降低,解决了高压场景中“耐压与低损耗不可兼得”的难题。至今,它仍是硅基高压功率器件的主流方案。 - 先进封装技术革新(1990 年代 - 2000 年代)

- 1990 年代:DPAK(TO-252)、D2PAK(TO-263)等表面贴装封装普及,满足了车用电子、工业设备的散热需求,替代了传统插装封装,推动功率模块小型化。

- 2000 年代:铜夹封装技术(如LFPAK)通过增大芯片与引出端的接触面积,提升电流承载与散热能力,适配新能源汽车、大功率电源等高温高功率场景。

- 逻辑 MOSFET:从平面到立体结构(2010 年代 - 2020 年代)

针对 IC 微型化中“短沟道效应”难题,逻辑 MOSFET(用于 CPU、GPU 等)开启了结构革命:- 2011 年:英特尔推出 22nm FinFET(鳍式场效应晶体管),以“三面栅极包裹沟道”的立体结构,强化静电控制。在同等性能下,其功耗和速度均有显著提升,成为先进工艺的核心架构。

- 2020 年代:GAA(环绕栅极)晶体管技术实现量产,以“全包围沟道”结构进一步提升电流驱动能力和静电控制,在不增大面积的前提下突破性能极限,适配 AI 芯片等高端算力需求。

- 宽禁带半导体器件(2010 年代 - 至今)

突破硅基材料物理极限,针对高压、高频、高温场景(如新能源汽车、储能、5G 基站):- SiC MOSFET:具备高耐压、耐高温、开关速度快等特性,用于高铁牵引变流器、储能逆变器,有效降低系统体积与能耗。

- GaN HEMT(氮化镓高电子迁移率晶体管):具备高功率密度、高开关频率的特点,广泛用于快充、5G 基站功放,推动设备小型化与高效化。

MOSFET / VMOS / DMOS / LDMOS / UMOS / BiCMOS / SJ-MOSFET / SiC-MOSFET / GaN-HEMT

| 时间段 | 缩略词 | 全称 | 描述 |

|---|---|---|---|

| 1960 年代初 | MOSFET | Metal-Oxide-Semiconductor Field-Effect Transistor | 金属 - 氧化物 - 半导体场效应晶体管,基础结构实用化,首次实现 “栅极电压控制沟道导电”。 |

| 1970 年代中期 | VMOS | Vertical MOS | 垂直 MOS,通过 “V 型槽” 结构实现垂直导电,显著提升功率承载能力。 |

| 1970 年代末 - 1980 年代初 | DMOS | Double-Diffused MOS | 双重扩散 MOS,通过两次离子注入形成短沟道,结构简化且成本降低。 |

| 1980 年代中期 | LDMOS | Laterally Diffused MOS | 横向扩散 MOS,创新 “横向导电” 结构,适用于射频(RF)、微波等高频大功率场景。 |

| 1980 年代末 - 1990 年代初 | UMOS | U-groove MOS | 沟槽型 MOS,通过 “U 型沟槽刻蚀” 将栅极嵌入硅片,增大栅极对沟道的控制面积。 |

| 1990 年代中期 | BiCMOS | Bipolar-CMOS | 双极型晶体管与 CMOS 集成工艺,融合了 CMOS 的低功耗和 BJT 的强驱动能力。 |

| 1998 年 | SJ-MOSFET | Super Junction MOSFET | 超结 MOSFET,通过在 N - 漂移区交替制造高掺杂 P 型柱与 N 型柱,形成周期性 PN 结,大幅降低导通损耗。 |

| 2010 年 | SiC-MOSFET | Silicon Carbide MOSFET | 碳化硅 MOSFET,耐压高、耐高温、开关速度快,适用于高铁牵引变流器、储能逆变器。 |

| 2010 年代 | GaN-HEMT | Gallium Nitride High Electron Mobility Transistor | 氮化镓高电子迁移率晶体管,功率密度高,广泛用于快充、5G 基站功放。 |

via:

-

BJT、CMOS、DMOS、BiCMOS 和 BCD 半导体制程技术简介 - 知乎

https://zhuanlan.zhihu.com/p/834913392 -

BCD 工艺、CMOS 工艺、BiCMOS 工艺_bcd 工艺与 cmos 工艺的区别 - CSDN 博客

https://blog.csdn.net/weixin_43205692/article/details/106558449 -

CMOS 与 DMOS:结构、工作原理与应用 - CSDN 博客

https://blog.csdn.net/weixin_45293089/article/details/129634654 -

DMOS 算法介绍及算法原理_dmos 的计算公式 - CSDN 博客

https://blog.csdn.net/mazhitong1020/article/details/76576771 -

科学网—[笔记] A Brief History of the MOS transistor, MOS晶体管简史 - 杨正瓴的博文

https://blog.sciencenet.cn/blog-107667-1484850.html -

V-Groove MOS,vmos structure, vertical mos features,v-mos applications

https://circuitstoday.com/v-groove-mos-vmos -

VMOS FET vs UMOS FET: Key Differences Explained | RF Wireless World

https://www.rfwireless-world.com/terminology/vmos-fet-vs-umos-fet -

DMOS vs VMOS vs LDMOS: Understanding the Differences | RF Wireless World

https://www.rfwireless-world.com/terminology/dmos-vs-vmos-vs-ldmos