FPGA|Quartus II 中pll IP核的具体使用方法

在FPGA设计中,时钟管理是至关重要的一部分,而Quartus II提供的PLL(Phase-Locked Loop)IP核是实现精确时钟控制和频率转换的强大工具。PLL IP核可以帮助设计者生成多个时钟信号、调整时钟频率,甚至进行时钟域之间的同步。本文主要纪录我常用的操作步骤以防时间长不用遗忘。

1 什么是 PLL IP 核

PLL(Phase-Locked Loop,锁相环)是 FPGA 中常用的时钟管理工具,能够从输入时钟中生成不同频率的输出时钟。PLL 可以调节频率、改变相位,甚至实现时钟的分频和倍频,广泛应用于时钟信号的同步、去抖动和频率转换等任务。

在 Quartus II 中,PLL 是通过使用其提供的 PLL IP 核实现的。PLL IP 核不仅简化了时钟管理的流程,还为用户提供了丰富的配置选项,帮助实现各种复杂的时钟设计需求。

2 创建 PLL IP 核具体步骤

2.1 设置pll保存位置

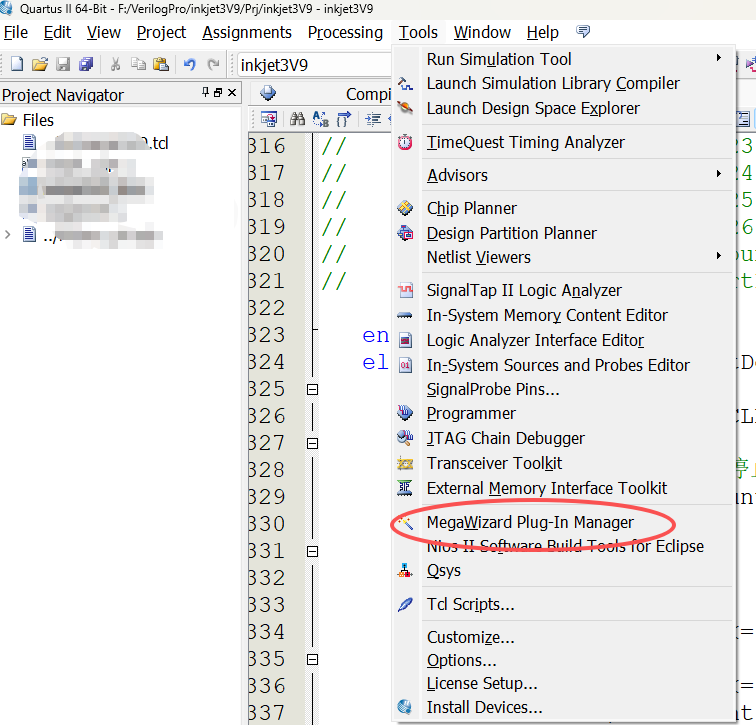

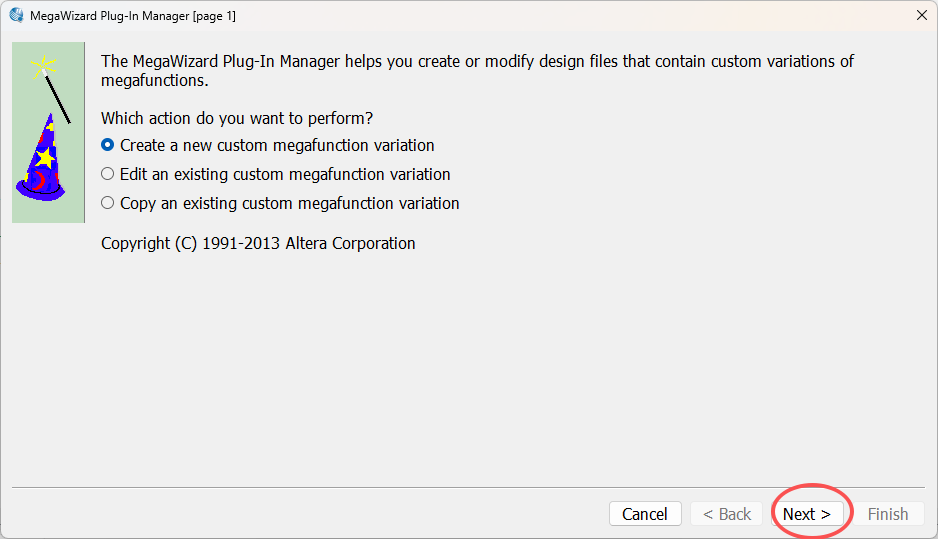

首先选择Tools–>MegaWizard Plug-In Manager,进入MegaWizard Plug-In Manager进行下一步创建步骤:

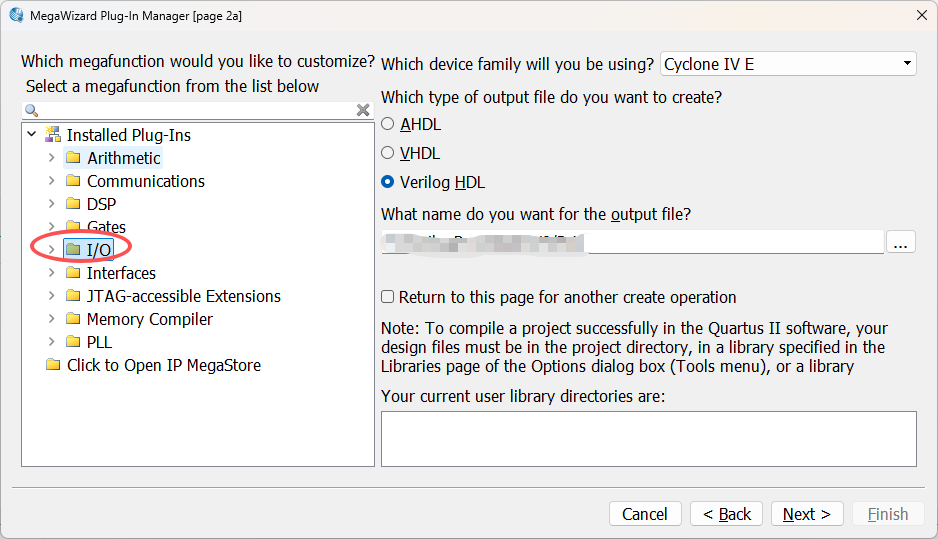

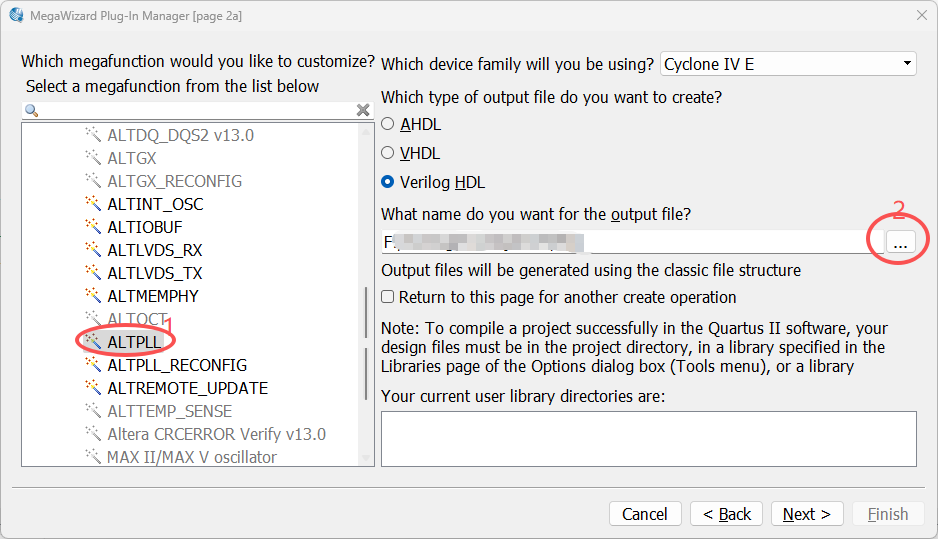

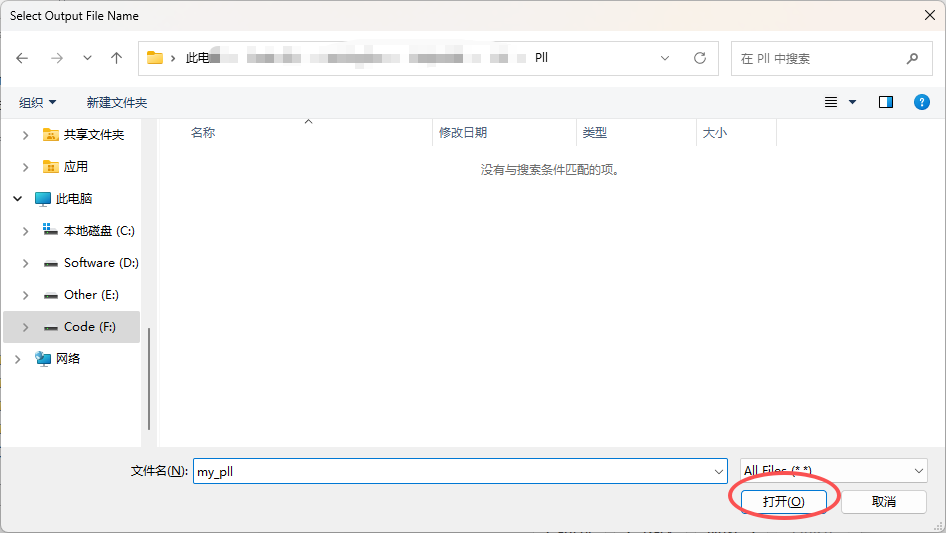

这里选择I/O下面的ALTPLL,然后选择pll保存的路径:

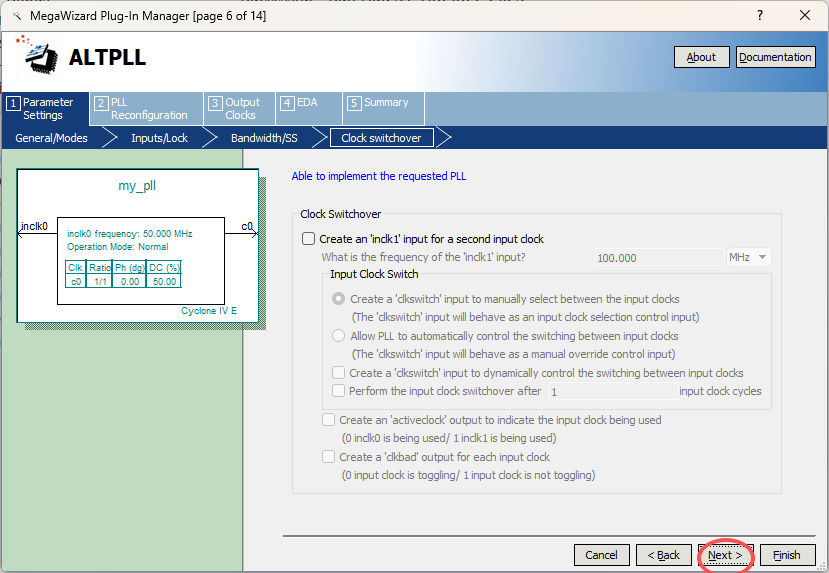

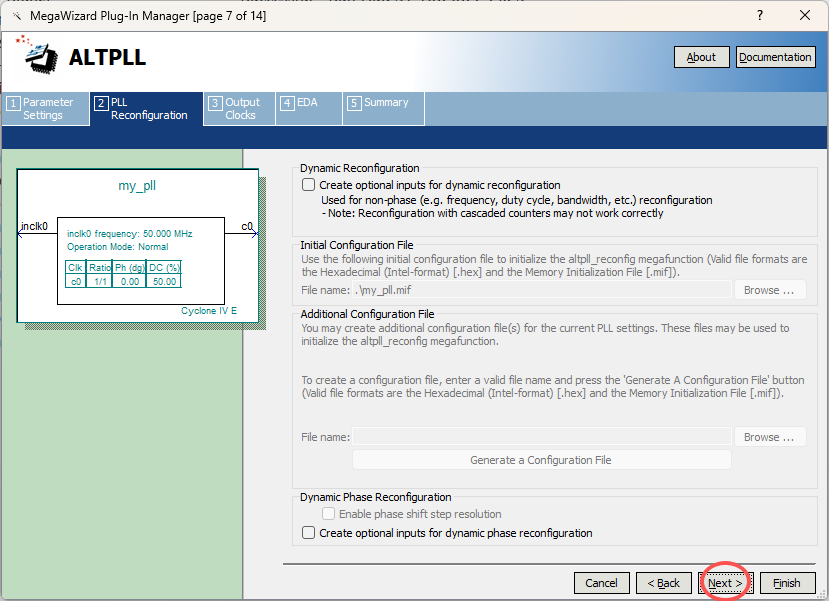

2.2 配置 PLL IP 核

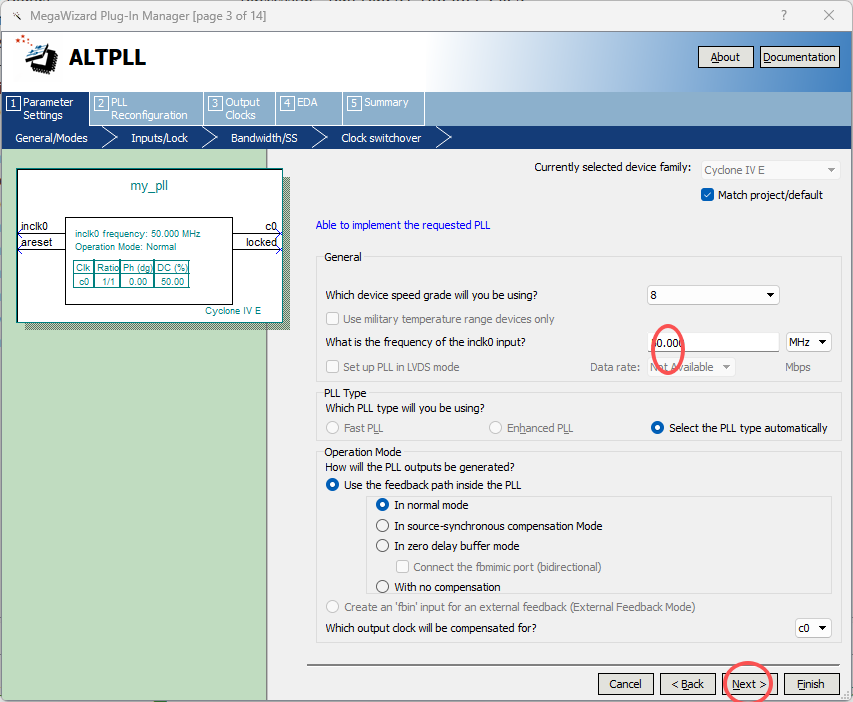

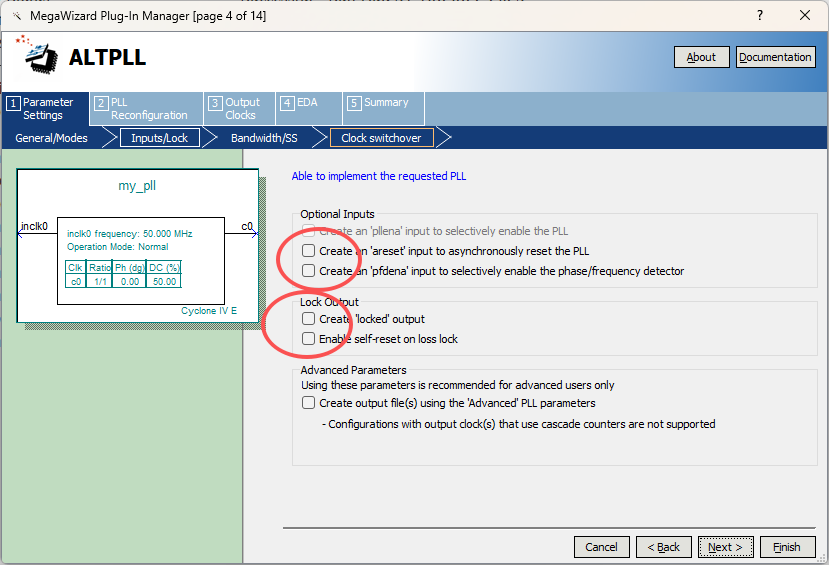

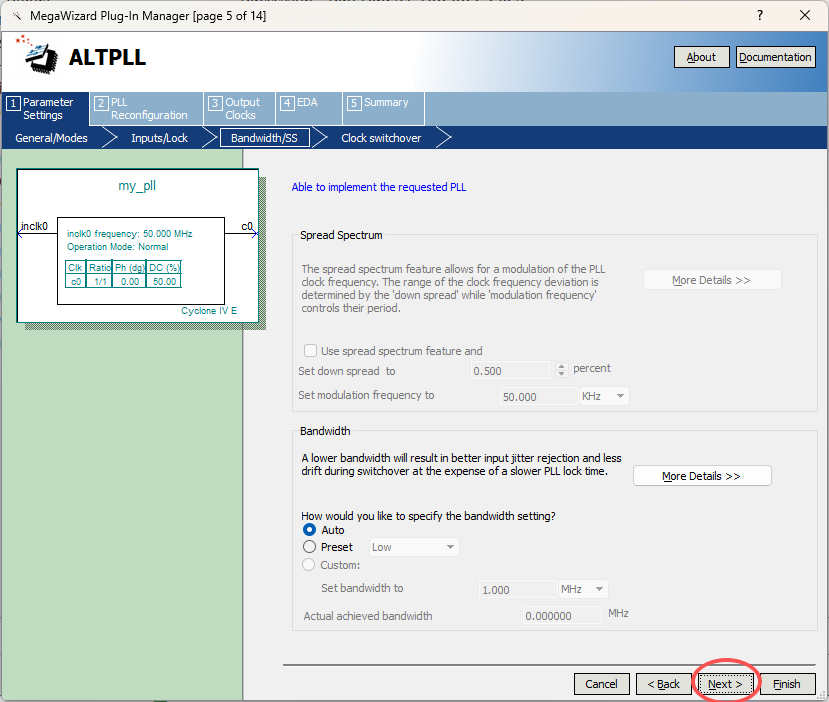

这里设置的是你的输入时钟频率,一般设置成你的开发板的主时钟频率。

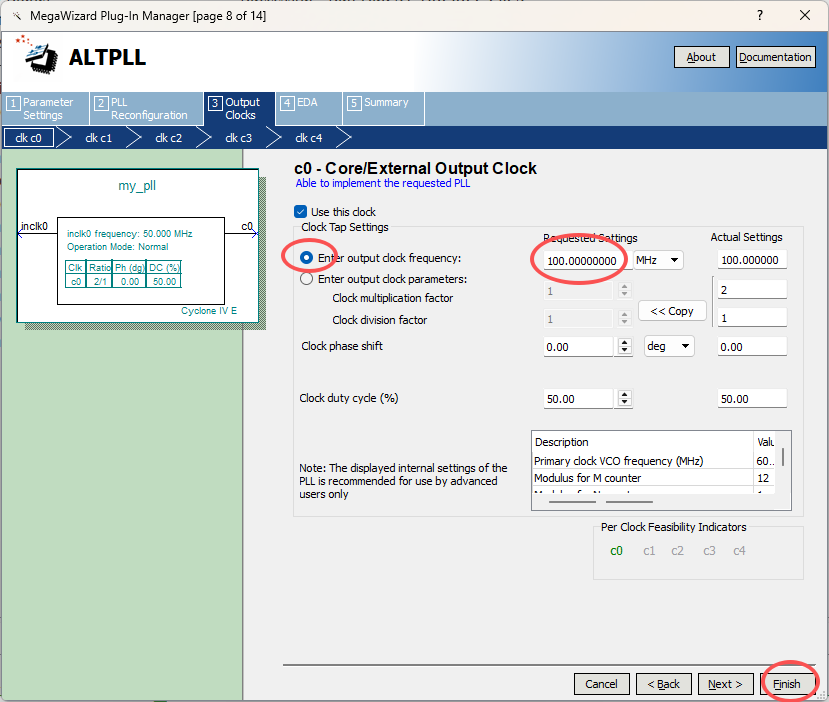

这里设置的是你的输出时钟,可以修改成你所需要的时钟频率。

这里注意,我设置完成一个输出时钟就点Finish了,如果想继续配置多个输出时钟可以继续点击Next。

3 具体项目中使用

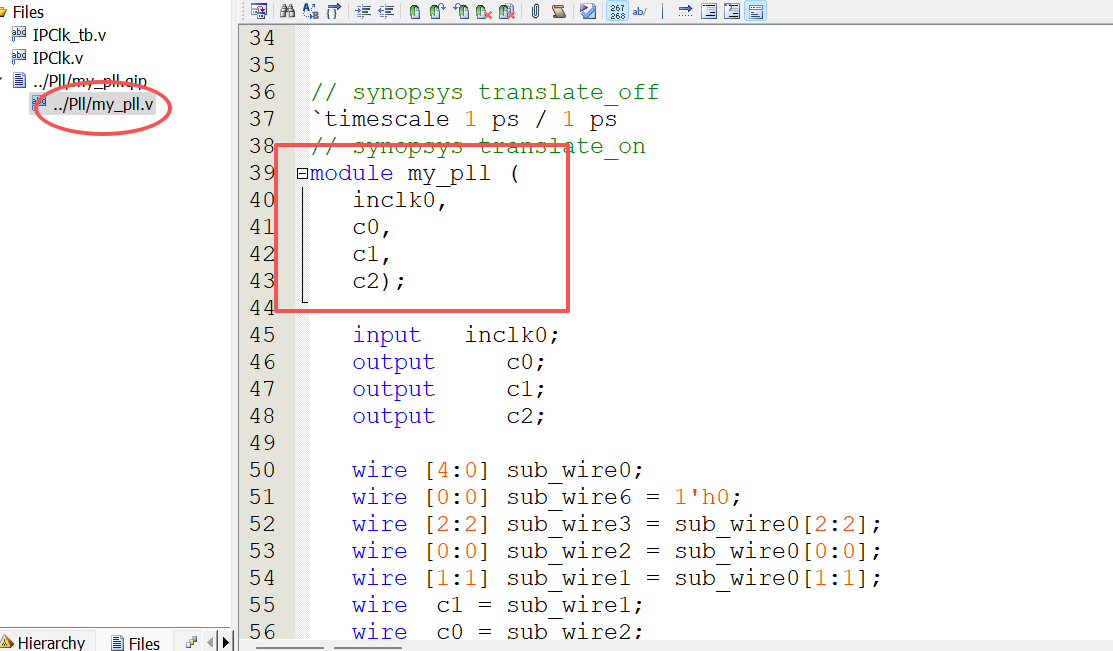

3.1 打开IP源文件

这里打开生成pll源代码,将代码复制到你的项目里面,并将其实例化。

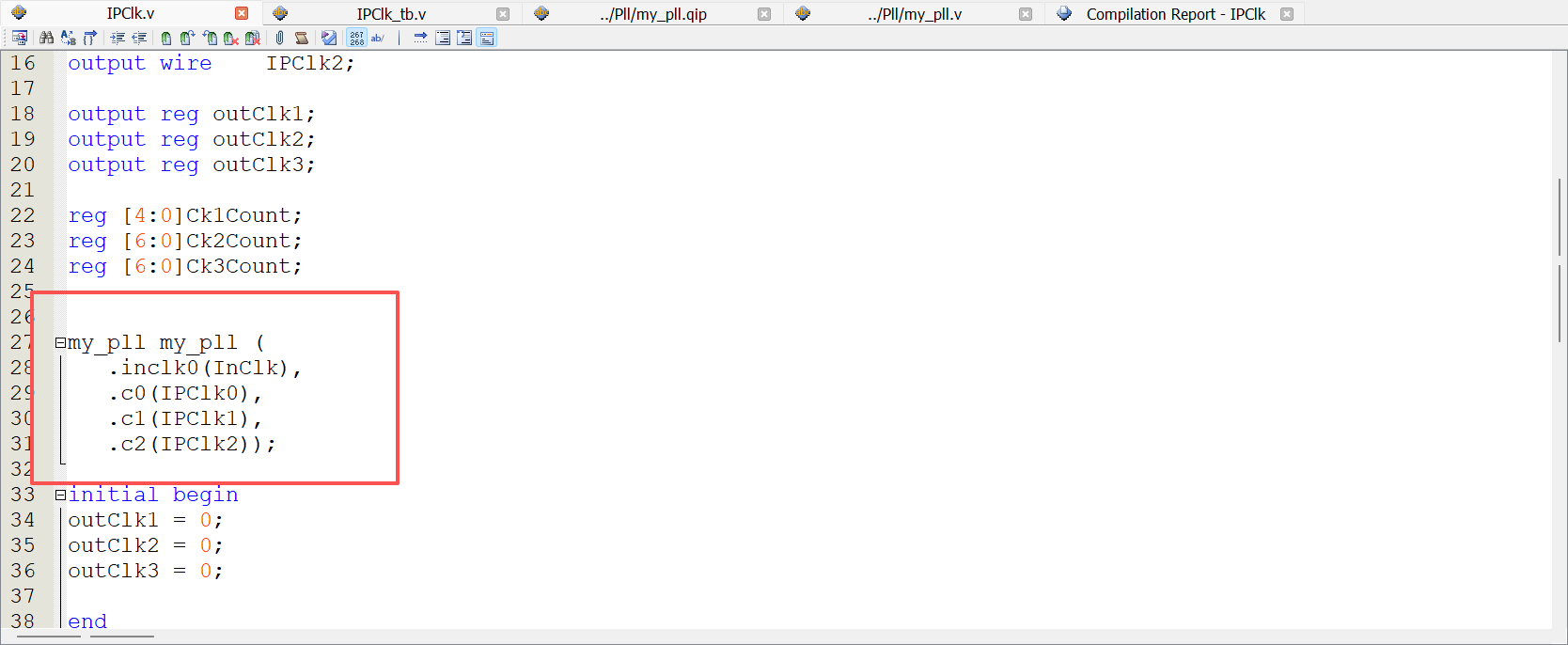

3.2 实例化PLL

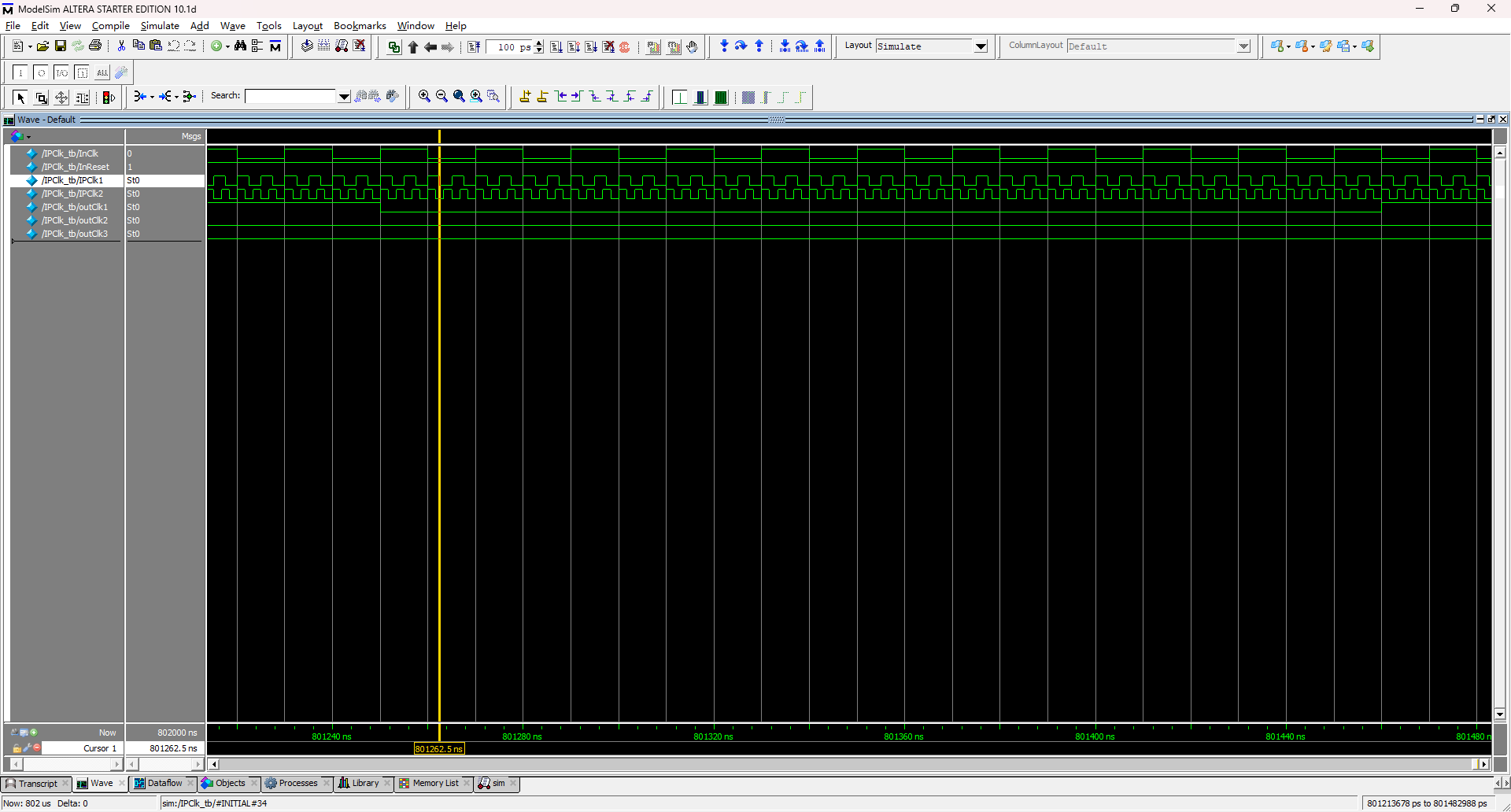

3.3 仿真看时钟是否正确

总结

在 Quartus II 中使用 PLL IP 核进行时钟管理,能够简化设计流程并提高时钟系统的稳定性。通过本文的介绍,设计者可以掌握 PLL IP 核的创建、配置和集成方法,更加高效地完成时钟管理工作。合理利用 PLL 的特性,能够在复杂的 FPGA 设计中确保时钟信号的精确控制,从而提升整个系统的性能与可靠性。