【DC工具GUI入门】

DC工具GUI入门

- 1 DC启动流程

- 1.1 DC启动方式

- 1.2 设置相关环境变量

- 1.2.1 symbol_library

- 1.2.2 link_library

- 1.2.1 target_library

- 1.3 读入分析RTL

- 1.3.1 read design file

- 1.3.2 link

- 1.3.3 以ddc格式保存未映射的设计

- 1.3.4 查看内存中的设计和库

- 1.3.5 看symbol和Schematic视图

- 1.4 Constrain the .con

- 1.5 compile the degin

- 1.6 generate reports and analyze timing

Synopsis综合工具DC使用入门,在这里为以DC_Labs为基础使用GUI工具来入门;

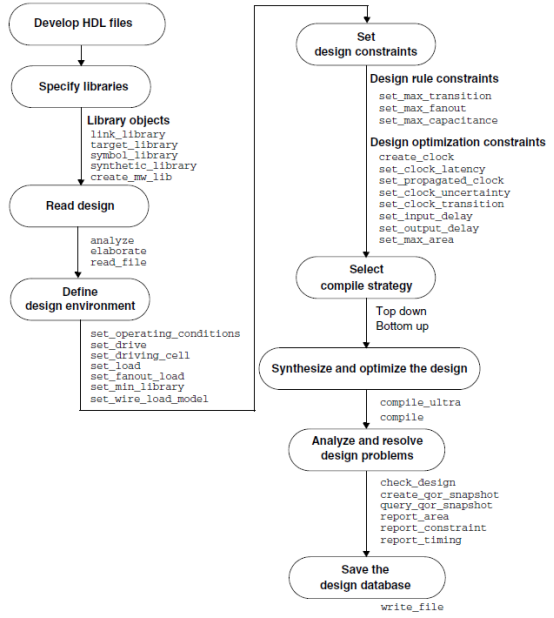

基本流程如下:

1 DC启动流程

Baisc Steps in Synthesis Flow

1.设置SETUP相关变量

2.read the RTL code.

3.constrain ghe design(source a .con file)

4.syntheisze the design(compile)

5.generate the reports(report_*)

6.save the resulting netlist(write)

《tupian 》

1.1 DC启动方式

- dc_shell:命令行/design_analyzer(对应的gui)

- dc_shell_t:拓展tcl实现dc命令; --design_vision(对应的GUI)

本篇文章基于design_vision的方式来介绍使用DC。

1.2 设置相关环境变量

set serach_path "$search_path ../ref/db ./scripts" ##来追加环境变量搜录路径

set target_library "sc_max.db"

set link_library "* sc_max.db"

set symbol_library "sc.sdb"

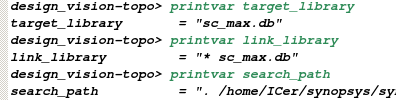

验证是否设置正确:

有的时候会添加synthesic_library(算术库):在初始化DC时,不需要设置标准的DesignWare库standard.sldb用于实现verilog描述的运算符,DC会把加法、乘法等运算综合成性能较差的电路。如果需要扩展DesignWare,需要在synthetic_library中设置,同时需要在link_library中设置相应的库以使得在链接的时候FC可以搜索到相应运算符的实现。

search_path: 说白了就是给项目library提供搜素路径位置;

1.2.1 symbol_library

符号库:定义了单元电路显示的原理图库。查看分析电路图时,需要设置sdb格式的符号库。

1.2.2 link_library

链接库是设置模块或单元电路的引用。对于所有DC可能用到的库,我们都需要在link_library中指定,也包括要用到的IP。

在link_library的设置中必须包含“*”,表示DC在引用实例化模块或者单元电路时首先搜索已经调进DC memory的模块和单元电路。

1.2.1 target_library

读入的HDL代码首先由Synopsys自带的GTECH库转成DC内部交换的格式,然后经过映射到目标库,最后生成优化的门级网表。

目标库一般是db格式,由lib格式转化而来。目标库包含了各个门级单元的行为、引脚、面积、时序信息等,有的还包含了功耗方面的参数。

DC在综合时就是根据目标库中给出的单元路径的延迟信息来计算路径的延时,并根据各个单元的延时、面积和驱动能力的不同选择合适的单元来优化电路。

目标库是综合后电路网表要最终映射到的库。

1.3 读入分析RTL

1.3.1 read design file

read_file -format verilog ./rtl/TOP.v

GUI: file->read…

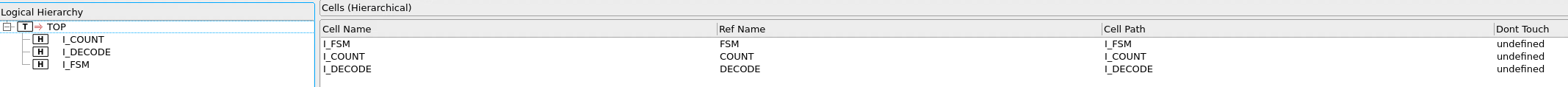

读取RTL设计文件;读取完成后可以看到相关显示:

Note: 这这里确认一下是否为正确的TOP顶层;

current_design # 来查看current_design xxx # 设置顶层

1.3.2 link

link # 查看当前要综合的设计是否缺少子模块; 返回值为1,说明子模块完整;

GUI: file->link_design->ok.

1.3.3 以ddc格式保存未映射的设计

write -hierarchy -f ddc -out unmapped/TOP.ddc

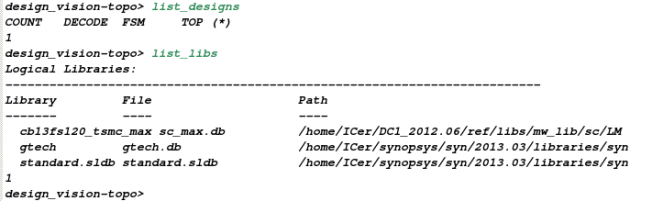

1.3.4 查看内存中的设计和库

list_designs

list_libs

1.3.5 看symbol和Schematic视图

1.在Hierarchy窗口下,选择哪一个模块直接点击工具栏相应工具;

2.select Symbol View 和Sche来查看视图;

1.4 Constrain the .con

source xxx.con

1.5 compile the degin

通过敲击命令-compile后,会得到一个able出来;

compile #compile_ultra是在编译的过程中为了更优的选择,取消了子模块的概念,就没有了层次划分的概念;

The area col:

The Worst Neg Slack:

The Total Neg Slack:

1.6 generate reports and analyze timing

rc is the alias of “reprot_constraint -all_violators” in the .synopsys_dc.setup file.

rc # report_constraint -all_violators

rt # report_timing

ra # report_area

以上是基本DC的启动流程;