FPGA 时序分析(五)

接上一篇文章 :

8、时序约束例外

时序例外约束,指的是告知时序分析工具对特定的路径执行特殊的时序分析方式。默认情况下,时序分析工具对于某些路径的分析可能不符合实际情况,造成时序太紧或者太松,这就需要时序例外约束,使时序分析工具做出正确的分析。通过时序例外约束,工具可以放松特定位置的时序分析,以专注于其他路径的时序分析,实现更好的时序收敛。

下面的情况,可以使用时序例外约束:

1、异步跨时钟路径应该予以忽略;

2、通过组合单元的路径为静态路径;

3、逻辑单元并不是在每个时钟周期都需要采样数据。

注意不能使用多个时序例外约束,对同一路径进行约束。使用时序例外约束时,必须遵守优先级原则,优先级由高到低为:

set_false_path > set_max_delay/set_min_delay > set_multicycle_path

8.1 伪路径分析set_false_path

伪路径约束用来处理非功能路径或没有时序要求的路径,可以减少时序分析工具的运行时间,可以使其他路径实现更好的时序收敛。伪路径约束后,时序分析工具将不再对该路径进行时序分析。

伪路径约束的格式如下:

#注意,-from -to -through,可以只使用一个,表示只要经过该节点的路径都为伪路径

set_false_path [-setup| -hold] -from <node_list> -to <node_list> -through <node_list>伪路径的常用使用场景:

1、两级寄存器跨时钟处理电路

2、上电后写入一次的寄存器,或者长时间更新一次,不影响其他电路功能的寄存器,

3、复位或者测试逻辑

4、实际不存在的路径

5、忽略异步DRAM的写时钟和读时钟之间的路径

8.2 多周期约束

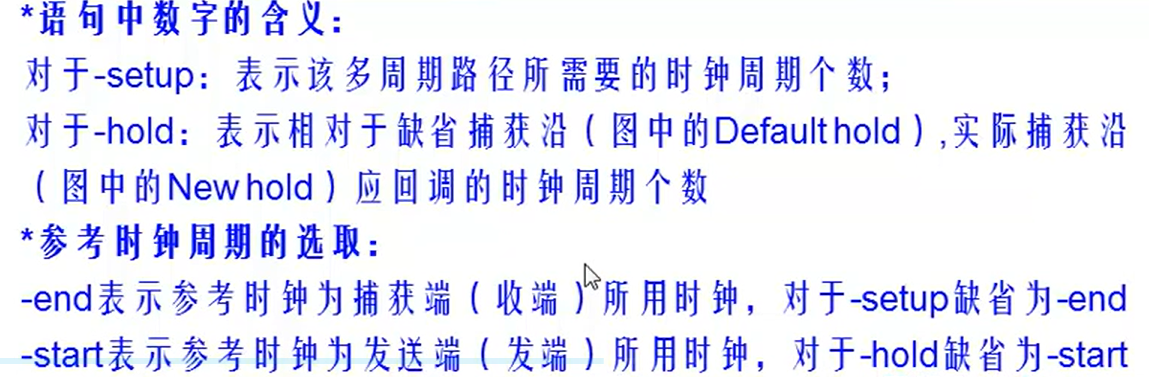

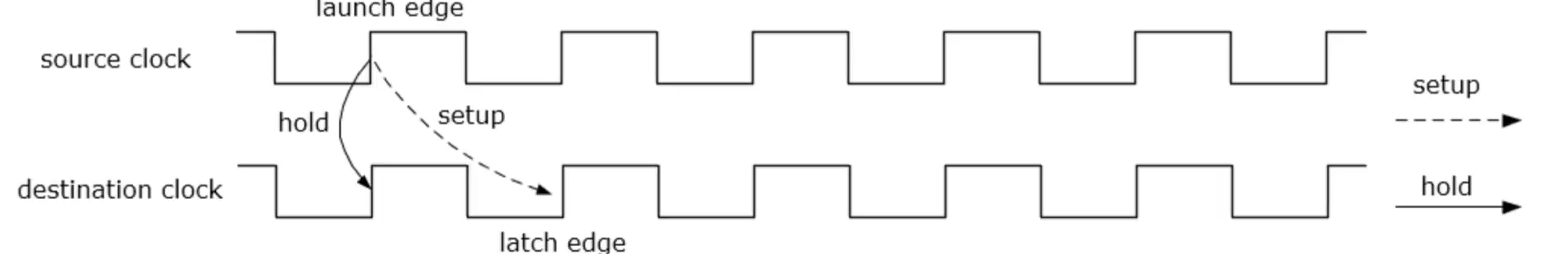

先说明一下单周期路径,单周期路径下的模型如下:

正常的单周期路径下的时序分析过程中,源寄存器时钟在时钟上升沿发送后,抵达目的寄存器,目的寄存器在下一个时钟进行数据的接收(在发射沿后的微小时间,数据发生了更新)。基于此时钟下的数据变化,此时我们可以在锁存沿处分析next data的建立时间,在发射沿处分析prev data的保持时间。

即,建立时间检查在发射沿的1个时钟周期后的位置;

即,保持时间检查在建立时间边沿的前一个时钟的位置,即发射沿本身的位置;

多周期约束是在正常的时序分析中进行的扩展,比如一些路径需要下面具体介绍。

8.2.1 多周期约束的语法

多周期约束的语法,使用指令set_multicycle_path。

语法命令如下:

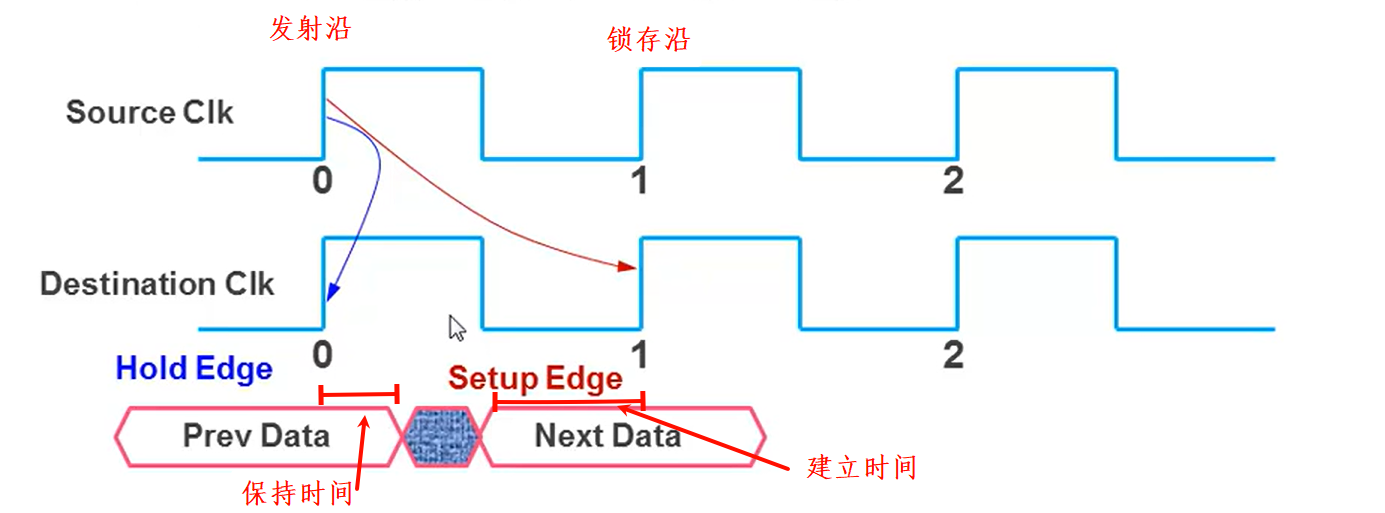

set_multicycle_path <path_multiplier> [-setup|-hold] [-start|-end] [-from <startpoints>] [-to <endpoints>] [-through <pins|cells|nets>]| 参数名称 | 含义 |

| -setup | 多周期路径所需要的时钟数目 |

| -hold | 相对于缺省锁存沿(default hold),实际捕获沿应回调的时钟周期数 |

| -start | 表示以源时钟作为参考时钟 |

| -end | 表示以目的时钟作为参考时钟 |

默认情况下,对于建立时间的分析,以目的时钟为参考时钟,使用-setup和-end搭配使用;

默认情况下,对于保持时间的分析,以源时钟为参考时钟,使用-hold和-start搭配使用;

在不进行多时钟周期约束时,实际vivado中对单时钟模型有默认的约束,其默认的约束语句如下:

set_multicycle_path 1 -setup -end -from [get_clocks src_clk] -to [get_clocks dest_clk]

set_multicycle_path 0 -hold -start -from [get_clocks s_clk] -to [get_clocks d_clk]8.2.2 end multicycle setup

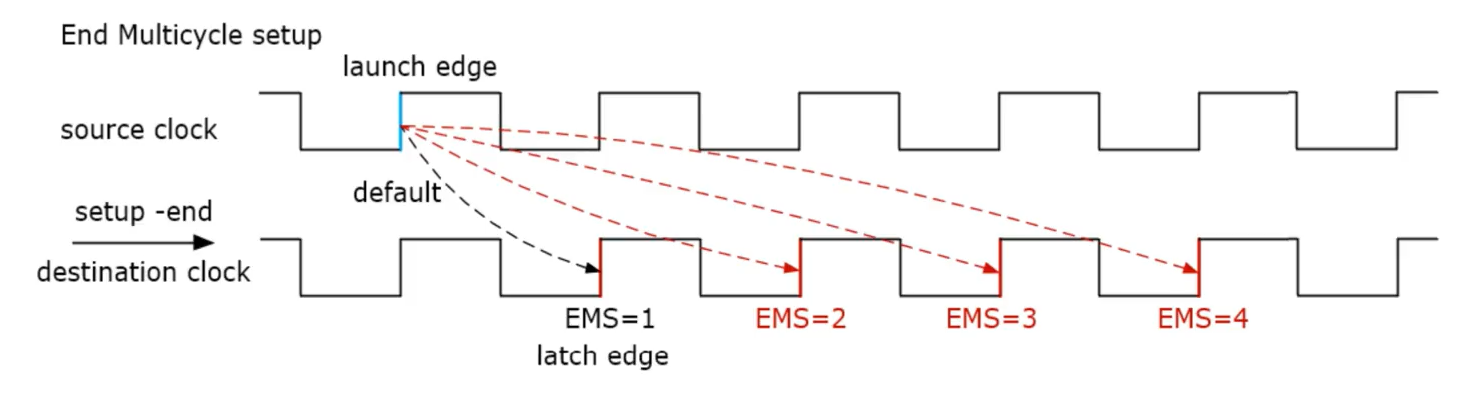

使用end命令,分析基于目的寄存器的时钟的建立时间,设置不同的path_multiplier参数,可以获得如下所示的建立时间分析边沿位置。

set_multicycle_path EMS -setup -end -from [get_clocks src_clk] -to [get_clocks dest_clk]

注意,仅设置-setup的约束时,hold的默认分析边沿,自动变化为setup分析边沿的上一个边沿。若需要进行调整,则需要增加-hold约束命令。

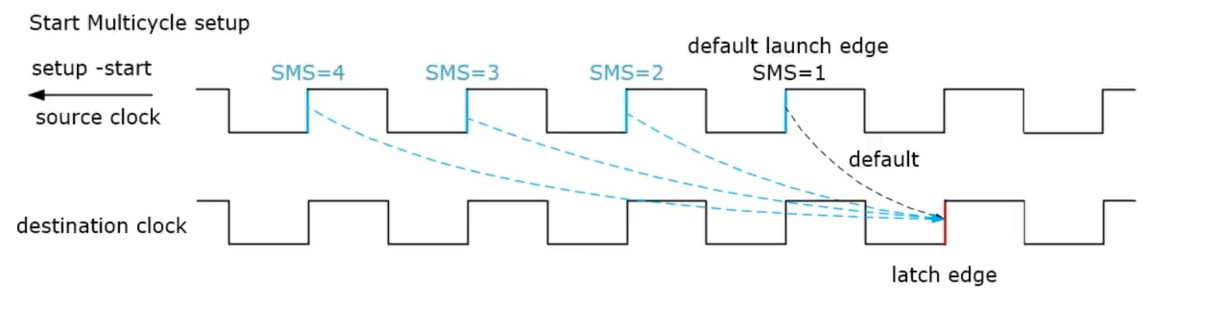

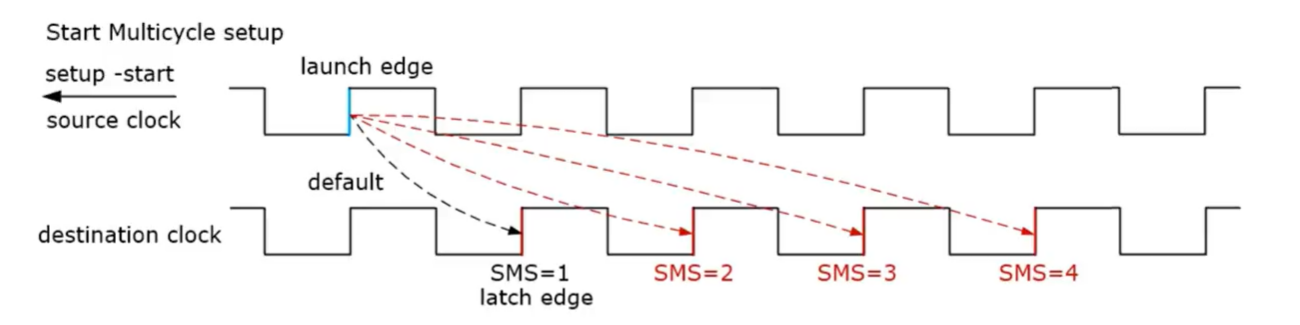

8.2.3 start multicycle Setup

使用start命令,设置不同的path_multiplier参数,可以获得如下所示的建立时间分析边沿位置。

set_multicycle_path SMS -setup -start -from [get_clocks s_clk] -to [get_clocks d_clk]

上图中,SMS越大,回调的时钟数目越多。

当然,理论上会按照上图进行分析,但是设计上,vivado时序工具会按照下图进行分析。

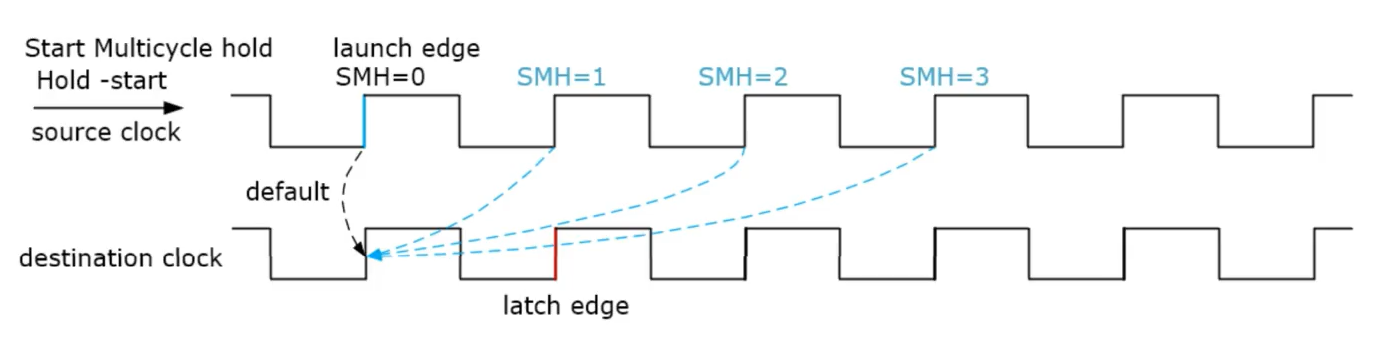

8.2.4 start multicycle Hold

使用start命令,设置不同的path_multiplier参数,可以获得如下所示的保持时间分析边沿位置。

set_multicycle_path SMH -hold -start -from [get_clocks s_clk] -to [get_clocks d_clk]

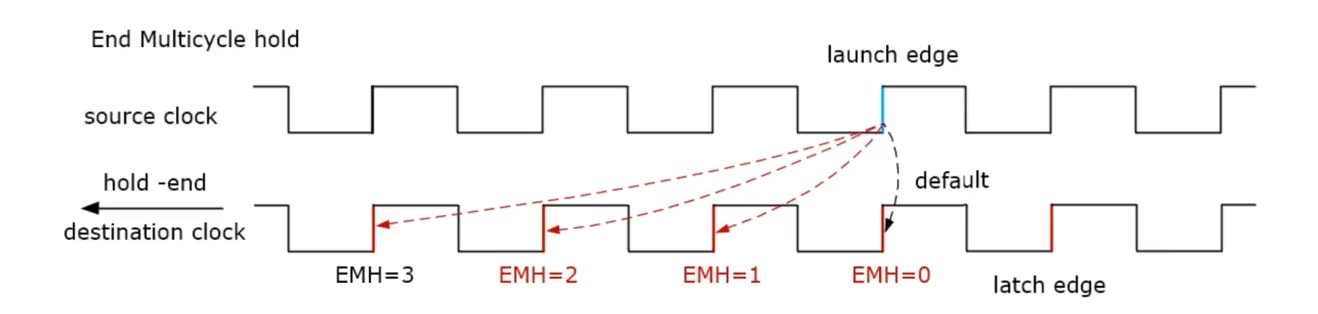

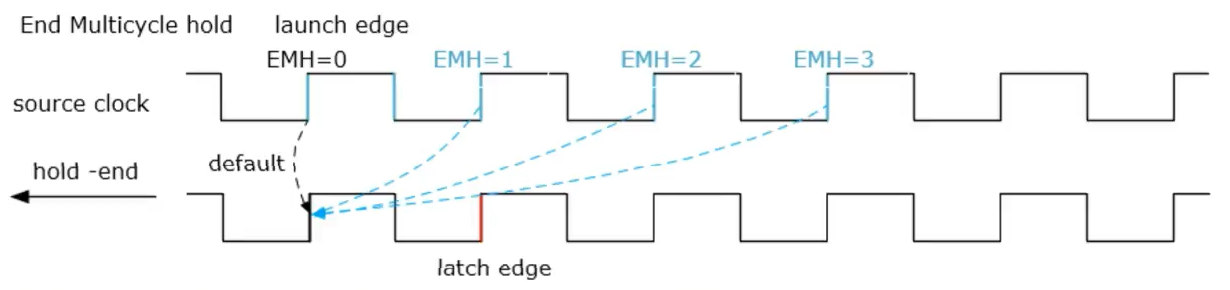

8.2.5 end multicycle Hold

使用end命令,设置不同的path_multiplier参数,可以获得如下所示的保持时间分析边沿位置。

set_multicycle_path EMH -hold -end -from [get_clocks s_clk] -to [get_clocks d_clk]

当然,理论上会按照上图进行分析,但是设计上,vivado时序工具会按照下图进行分析。

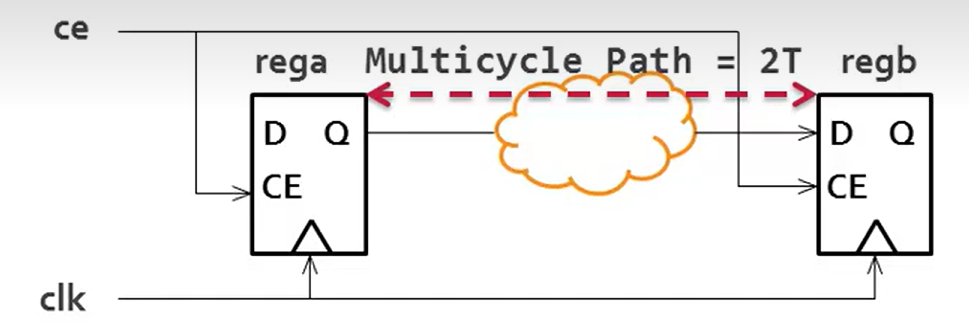

8.2.6 举例

多时钟周期路径的一个例子:

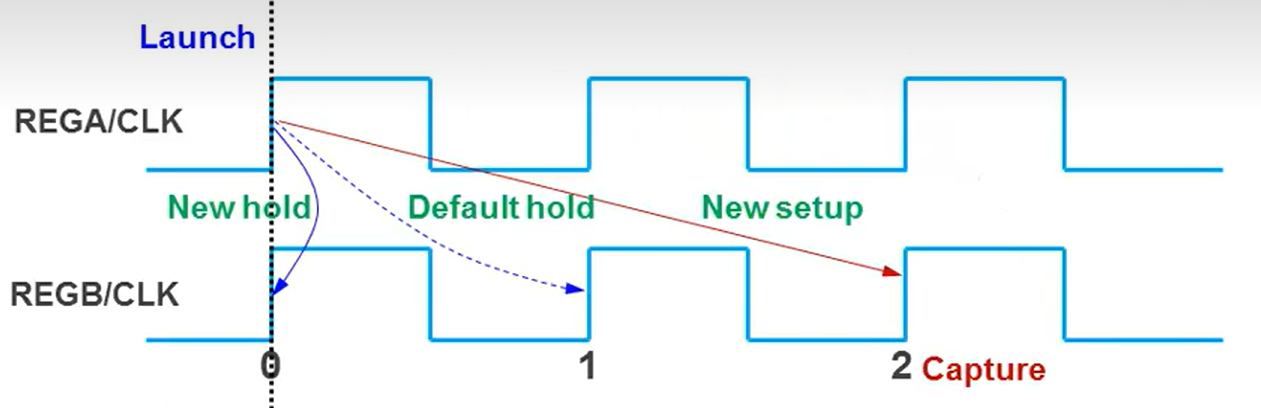

此时序路径中,CE信号2个时钟有效1次,即此时rega的Q信号会保持2个时钟的数据不变,在这2个时钟内,可以进行多时钟周期约束,减轻时序收敛压力。

若不进行约束,则时序工具默认的处理方式是这样的;

set_multicycle_path 1 -setup -end -from [get_cells rega] -to [get_cells regb]

set_multicycle_path 0 -hold -start -from [get_cells rega] -to [get_cells regb]

若进行多周期约束,时序工具的处理方式时这样的:

set_multicycle_path 2 -setup -end -from [get_cells rega] -to [get_cells regb]

set_multicycle_path 1 -hold -end -from [get_cells rega] -to [get_cells regb]