硬件-时钟学习DAY5——石英晶体负载电容设计全解析

每日更新教程,评论区答疑解惑,小白也能变大神!"

目录

一.负载电容的基本概念

二.负载电容的组成与定义

三.负载电容的计算方法

四.设计注意事项

五.实例分析

六.常见问题与解决

七.总结

一.负载电容的基本概念

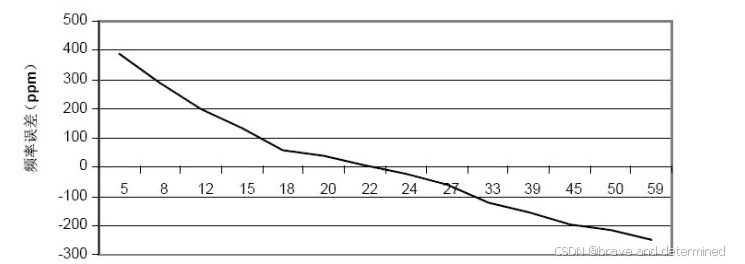

负载电容是石英晶体谐振器工作频率调整的关键参数,常见标准值为12.5 pF、16 pF、20 pF、30 pF等。它与晶体共同决定振荡器的实际工作频率。负载电容的变化对频率偏差有直接影响:容值减小时频率偏差增大,容值增大时偏差减小。

二.负载电容的组成与定义

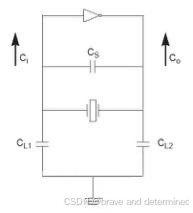

负载电容是从晶体引脚两端向振荡电路看进去的全部有效电容,包括以下部分:

- CG:晶体输入引脚(如XI)对地总电容,包括芯片输入引脚寄生电容(Ci)、PCB走线寄生电容(CPCBXI)和外加负载电容(CL1)。

- CD:晶体输出引脚(如XO)对地总电容,包括芯片输出引脚寄生电容(Co)、PCB走线寄生电容(CPCBXO)和外加负载电容(CL2)。

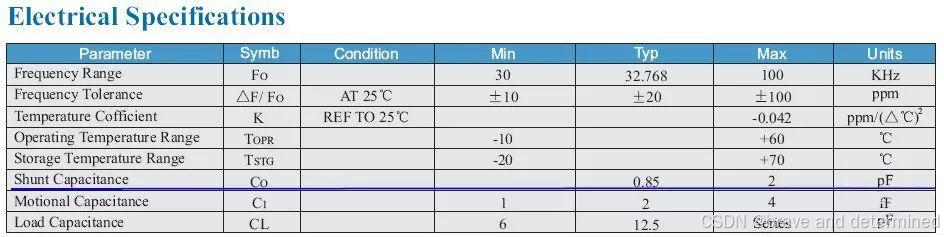

- CS:晶体两引脚间的寄生电容(Shunt Capacitance),由晶体规格书给出,典型值为0.2 pF~8 pF。

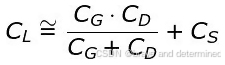

三.负载电容的计算方法

-

公式推导

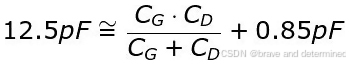

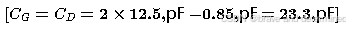

若标称负载电容 ( C_L = 12.5 pF}),晶体寄生电容 ( C_S = 0.85pF}),则:

-

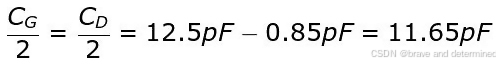

为了保持晶体的负载平衡,在实际应用中,一般要求CG=CD,所以进一步可以得到下式:

-

-

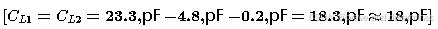

实际电容值计算

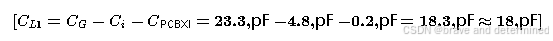

以芯片输入电容 ( C_i = 4.8 pF )、PCB走线电容 ( C_PCBXI = 0.2 pF) 为例,外加负载电容 ( C_{L1} ) 为:

同理,( C_L2 ) 也取18 pF以实现对称设计。

四.设计注意事项

- 寄生电容的影响

PCB走线寄生电容通常较小(约0.2 pF~0.5 pF),但高频或长走线时需精确评估。 - 芯片内部补偿

部分芯片(如某些MCU)内部已集成补偿电容,此时无需外加负载电容,但仍建议预留焊盘。 - 非对称设计例外

少数应用(如Cypress RTC晶体)要求 ( C_G \neq C_D ),需严格遵循厂商提供的计算指南。

五.实例分析

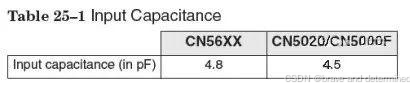

场景:设计一个32.768 kHz晶体振荡电路,标称负载电容 ( C_L = 12.5 , \text{pF} ),晶体寄生电容 ( C_S = 0.85 , \text{pF} ),芯片输入/输出寄生电容 ( C_i = C_o = 4.8 , \text{pF} )。

- 计算总对地电容:

- 计算外加负载电容:

- 实际选用:

选择18 pF的NP0/C0G电容,精度建议±5%以内。

六.常见问题与解决

- 频率偏差过大

检查负载电容是否匹配标称值,或重新测量PCB寄生参数。 - 起振困难

确保 ( C_{L1}/C_{L2} ) 容值对称,并验证晶体驱动功率是否足够。 - 温度稳定性差

选用温度特性稳定的电容(如NP0材质),避免使用Y5V/X7R等容值随温度变化的材质。

七.总结

负载电容的设计需综合晶体参数、芯片特性和PCB布局。通过精确计算与对称布局,可确保振荡频率稳定。实际应用中,预留调试空间并参考厂商指南是关键。