C5.6:双电源发射极偏置、特殊类偏置、PNP型偏置电路

接触过很多运算放大器会有正负电压供电,而负压的应用,让电路性能发挥的更好。

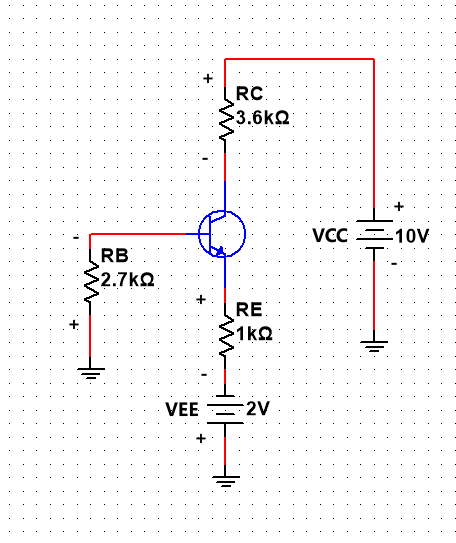

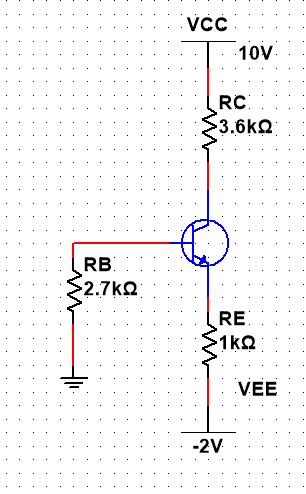

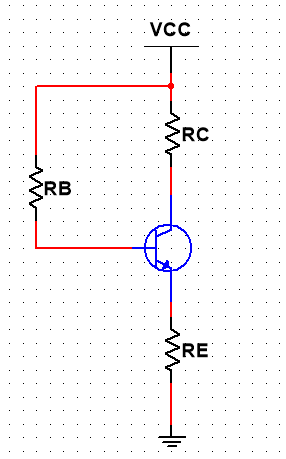

即上图所示,一个+10V和一个-2V的双电源供电,所以负电源让发射结正向偏置,正电源让集电结反向偏置,该电路还是发射极偏置电路,也叫双电源发射极偏置(TSEB),上图也可以简化为下图这样。

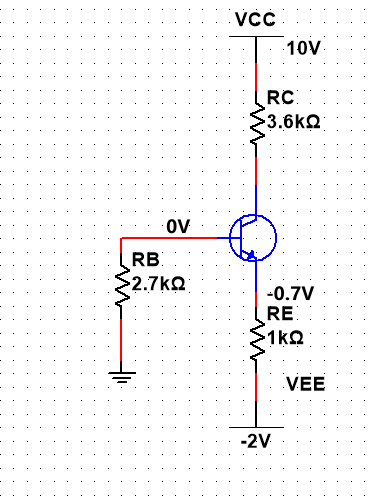

这种电路如果设计没问题的话,基极电流近乎为零,所以基极电源近似为0V,则如下图所示:

因为发射结导通压降为0.7V,所以当基极电压为0V,且发射结导通的时候,发射极电压为-0.7V,则发射极电流求解为:

VRE = -0.7V - (-2V) = 1.3V

IE = 1.3V / 1kΩ = 1.3mA

得到了发射极电流,自然就等效得到了集电极电流,进而通过集电极电阻求得集电极电阻的压降,进而正电源减去压降得到了集电极对地的电压:VC = 10V - 1.3mA*3.6kΩ = 5.32V

VCE是集电极和发射极的电位差,所以VCE = 5.32V - (-0.7V) = 6.02V

跟分压器相似,好的双电源发射极偏置也需要满足100:1准则,所以RB < 0.01βdc * RE,在满足这种情况下,求解公式就是VB ≈ 0V,所以IE = (VEE - 0.7V) / RE,VC = VCC - (IC * RC),所以VCE = VC + 0.7V。

良好设计的VDB电路和TSEB电路,Q点是不受β影响的。

不过TSEB电路误差来源有基极电压,现实情况里基极电压并不等于0V,在基极电阻上会有小电压,因为有很小的基极电流会流过该电阻,基极和地存在负电压,而良好的设计里,基极电压小于-0.1V,如果设计较大的基极电阻进行折中,则基极电压可能低于-0.1V,对电路诊断也是判断基极电压,若基极电压和地之间的电压读数过大,则不正常。

而有些偏置在书上很少提及,但是在老式电路图里却偶尔见到,下面简单聊聊很少使用的偏置电路。

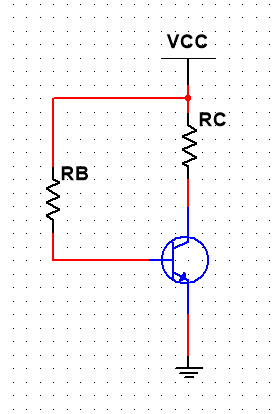

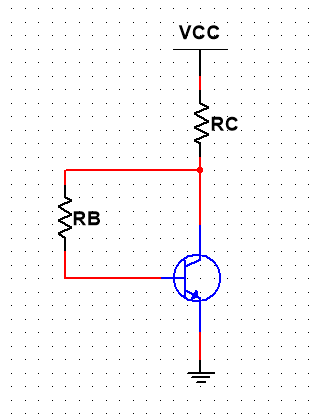

首先是发射极反馈偏置电路,而讨论之前要说前文的基极偏置电路,这种电路在Q点稳定性上是最差的,如下图,因为基极电流是固定的,所以集电极电流随电流增益变化而变化,晶体管更换或温度变化,这种电路的Q点会在负载线上移动。

而发射极反馈偏置则是在这种基础上,添加了发射极电阻,是最早用来稳定Q点的方法,如下图:

他的原理就是假设IC增加的时候,则VE增加(VE = IE * RE),对应VB也就会增加(为了满足导通压降,所以需要提高VB来导通发射结),VB增加意味着RB两端电压减少,意味着IB减少,这样IC就会减少,与IC初始增加相反,这种发射极电压变化反馈到基极电流的情况,叫负反馈。

这种电路没有广泛应用,就是因为大多数需要批量的产品,这种Q点漂移还是太大。

公式如下: IE = (VCC - VBE) / (RE + (RB / βdc))

VE = IE * RE

VB = VE + 0.7V

VC = VCC - IC * RC

使用发射极反馈偏置的目的是遮掩βdc变化的影响,RE需要远远大于RB / βdc,若满足这个条件,则Q点对βdc不敏感,但是在实际情况下,不是晶体管截止的情况下,足够大的RE来消除βdc的影响是很困难的。

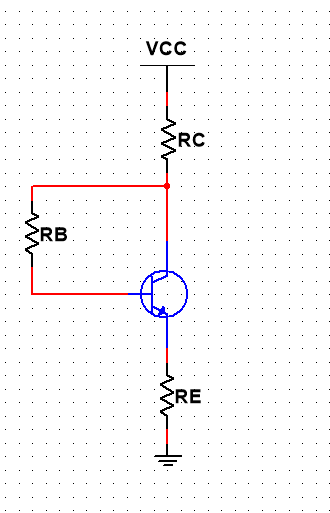

然后就是集电极反馈偏置,也叫自偏置,这是另一种稳定Q点的方法,基本思想就是电压反馈到基极,减少集电极电流变化,如下图:

假设IC增加,则RC压降会增加,所以VCC - IC * RC的值,也就是集电极对地电压就会降低,进而基极电阻两端的电压减小,导致基极电流减小,结果和假设相反。

公式则是:IE = (VCC - VBE) / (RC + (RB/ βdc))

VB = 0.7V

VC = VCC - IC * RC

而一般设置基极电阻让Q点处于负载线中间:RB = βdc * RC

在Q点稳定性方面,集电极反馈偏置要比发射极反馈偏置要更有效(发射极反馈实际情况难以满足电阻比例关系,容易是截止情况下满足比例关系),尽管电路还是对β敏感,但是由于结构简单,所以实际中可以经常应用。

而对于上述两种方式,所以结合出来了集电极-发射极反馈偏置电路,这种反馈足够深,同时发射极反馈和集电极反馈,改善了工作点的稳定性。

但是这种电路采用两个反馈,虽然有一定帮助,但是不适合大规模生产,公式如下:

IE = (VCC - VBE) / (RC+RE + (RB / βdc))

VE = IE * RE

VB = VE + 0.7V

VC = VCC - IC * RC

为什么该电路不适合大规模生产?

答:1.负反馈在交流通路中同样存在,可能在高频下因晶体管极间电容形成正反馈环路,引发振荡或频率响应畸变,晶体管参数(如极间电容)的批次差异会放大振荡风险,需额外补偿电路(如中和电容),增加设计和调试成本;

2.并且反馈电阻RB在交流等效电路中并联于输入/输出端,显著降低输入阻抗( Zi≈RB/β)并抬高输出阻抗( Zo≈RC),导致电压增益下降和带宽缩窄,为满足增益需求需选用高β晶体管,但β值的生产离散性(±50%)会加剧电路性能波动;

3.而且该电路依赖β,过高的β没事,而过低的β会让分母里RB占比增大,Q点对β变化更明显;

4.并且当晶体管接近饱和的时候,反馈作用减弱甚至消失(VC无法进一步降低),则Q点稳定性失效,所以设计的时候,批次可能导致部分电路在高温或者低压的情况脱离稳定;

5.并且集电极电压VC被反馈作用拉低,则输出交流信号幅度受限,在严格的场景下,需要更高的VCC来满足交流信号的要求,但是进一步牺牲了能效;

6.以及反馈仅仅靠IC间接调节,而非直接调节,所以VBE温漂未被补偿,导致有一定的延迟误差;

7.最后则是由于该电路要是稳定实现,需要精确计算,严格要求电阻和β的值,所以成本投入过大。

对于PNP型晶体管,在负电源供电的时候很常用,或者双电源的时候,和NPN晶体管互补使用,由于PNP和NPN相反的掺杂浓度,所以分析的时候要转换思路,要注意PNP的发射极多子是空穴而不是自由电子,但是正常偏置条件是一样的,都是基极-发射极正偏,同时基极-集电极反偏。

负电源供电:

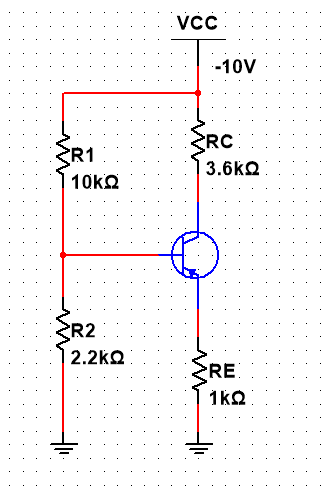

对于-10V负电源的分压器偏置电路,电路参数为负值,计算要格外注意,公式步骤如下:

VB = (R2 / (R1 + R2)) * VCC = -1.8V

PNP晶体管来说,发射极正偏的时候,VE比VB高0.7V,因此VE = VB + 0.7V = -1.1V

然后确认发射极和集电极电流:IE = VE / RE = 1.1mA,IC ≈ IE = 1.1mA

VC = -VCC + IC * RC - 10V + 1.1mA * 3.6k = -6.04V

VCE = VC - VE = -6.04 - (-1.1V) = -4.94V

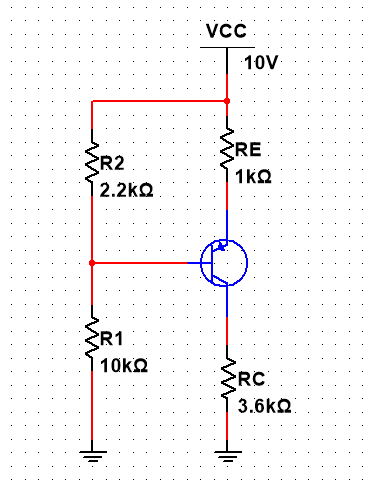

对于正电源供电的情况:

正电源要比负电源应用更广泛,所以经常见到上图这种画法,原理就是R2两端电压加在发射结及串联的发射极电阻上以此确认发射极电流,集电极电流流过RC,产生集电极对地电压,所以可以按照步骤来计算或者排查电路故障:

1.计算R2两端电压

2.上述电压减0.7V得到发射极电阻两端电压

3.求得发射极电流

4.计算集电极对地电压

5.计算基极对地电压

6.计算发射极对地电压

注:以上仅个人观点,如有错误,恳请批评指正