Diamond开发经验(1)

前言: 学习Lattice的芯片开发的过程中,很多实际开发过程中遇到的问题是没办法绕过的,虽然我今天被绕了一天(此句多余,单纯记录美好心情哈哈哈哈)将这些解决方法梳理成文章供大家参考,十个问题组成一篇文章。

文章目录

- 1.两个JTAG如何同时在线调试?

- 2. 添加设备列表中没有的flash型号?

- 3. Reveal的信号不会更新?

- 4. Spreadsheet引脚显示unconnected

- 5.Lattice文档说明

- 6.传送门

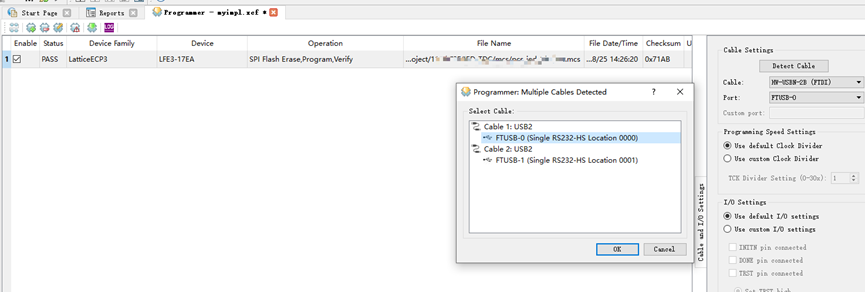

1.两个JTAG如何同时在线调试?

在programmer界面 点击Detect Cable会显示两个板子通过两个USB Port连接到了电脑上。在两个板子调试时,打开两个Diamond,可以先后连接JTAG以便确认FTUSB-0对应的板子是哪一个,后连接的则对应FTUSB-1。在两个Diamond中分别选择不同的Port下载文件即可。

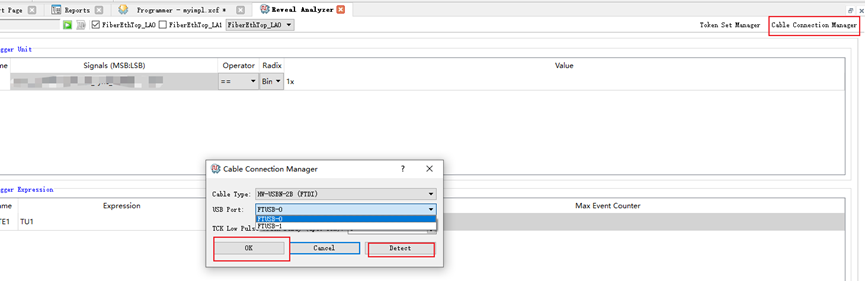

而Reveal文件需要在两个bit文件烧写完成之后依次点击使用。需要说明,如果一个Diamond的reveal正在等待触发信号,而另外一个开始烧写bit文件,通常都会出错。在各自烧写完毕后,打开reveal文件,可以看到右上角有Cable Connection Manager按钮,单机此按钮,在弹出的对话框中单机detect按钮,选择该工程对应的USB Port点击OK即可。

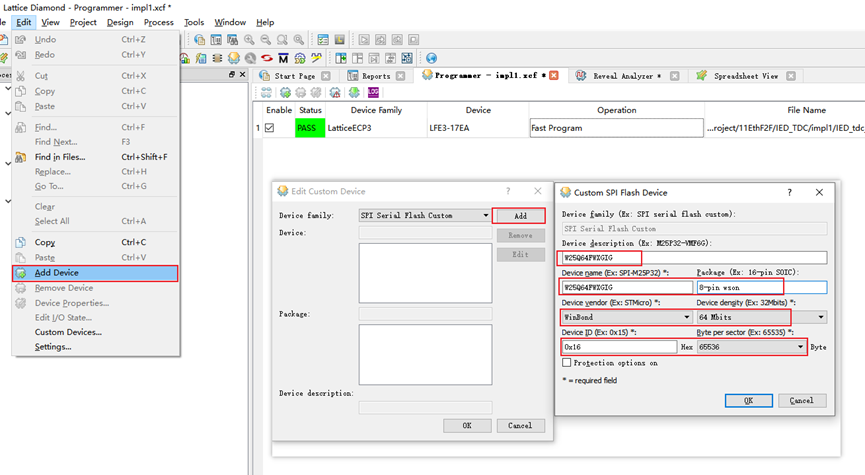

2. 添加设备列表中没有的flash型号?

在Programmer界面,选择Edit–>Add Device在弹出的对话框中选择Add,然后在新弹出的对话框中,添加板贴Flash的参数依次包括设备名称、封装、厂商、容量、设备ID等内容,这些内容在Flash手册中都会标写。这里添加后,在固化操作时flash列表中就有新添加的这一项了。

3. Reveal的信号不会更新?

当修改了源文件之后,有时会发现想把新写的信号添加在Reveal Analyzer中监控,但是会发现在源文件中删除的信号还在,而新加的信号并没有更新。如果没有删除原来的信号,工程可以照常编译,执行综合—place—bitstream file等过程,Reveal Analyzer依然不更新。这时需要打开Reveal Analyzer的界面,然后找一个IP核重新生成一下即可。这可能是软件的bug,anyway,这么做是可以解决问题。

4. Spreadsheet引脚显示unconnected

明明在Top文件中添加了输入或者输出管脚,并且工程也已经生成了bit文件,但在Spreadsheet View中依然显示未链接,这通常是和这几个引脚相关的逻辑有问题。用第一篇文章的led demo举例子如下:当代码写成如下

module LED_demo

(

input clk_i, //输入系统时钟

input rst_n, //输入复位信号

output led1, //输出led1

output led2 //输出led2,与led1取反

);

parameter CLK_DIV_PERIOD=125_000_000;

reg clk_div=0;

assign led1=clk_div;

assign led2=~clk_div;

reg[31:0] led_cnt=0; //分频用的计数器

always@(posedge clk_i or negedge rst_n)beginif(!rst_n)beginled_cnt<=0;end else if(led_cnt==(CLK_DIV_PERIOD-1)) beginled_cnt<=0;end else beginled_cnt<=led_cnt+1'b1;end

endalways@(posedge clk_i or negedge rst_n)beginif(!rst_n)beginclk_div<=0;end else if(led_cnt<(CLK_DIV_PERIOD>>1)) begin clk_div<=0;end else beginclk_div<=1;end

end

endmodule

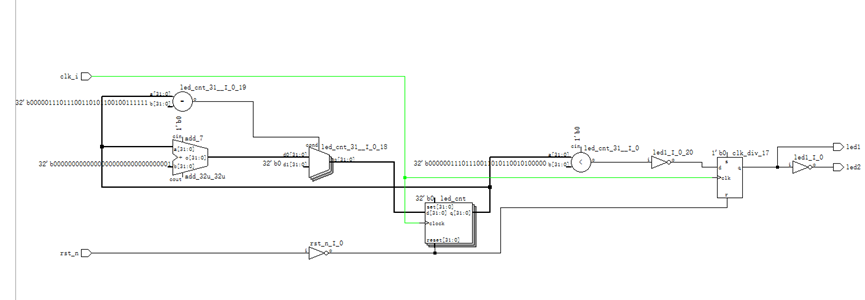

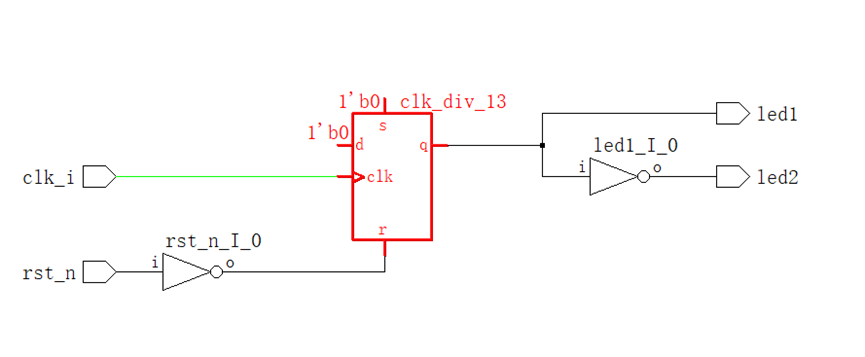

这是一段没有任何问题的代码,综合前的电路结构图如下所示:

如果我把代码中 reg[31:0] led_cnt=0; 修改为 reg[23:0] led_cnt=0; 这时SpreadSheet View中会显示引脚led1、led2为Unconnected,此时综合前的电路结构图如下所示,由于led_cnt的位宽小于常量125_000_000所以clk_div恒为0,综合工具把这里的代码直接优化成如下图所示的电路结构。也就是这个隐蔽的问题造成了显示unconnected的情况。

5.Lattice文档说明

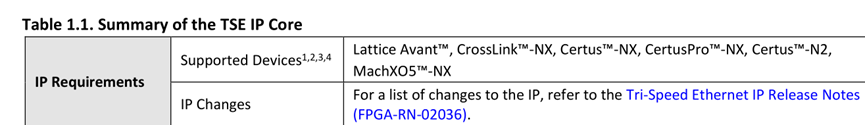

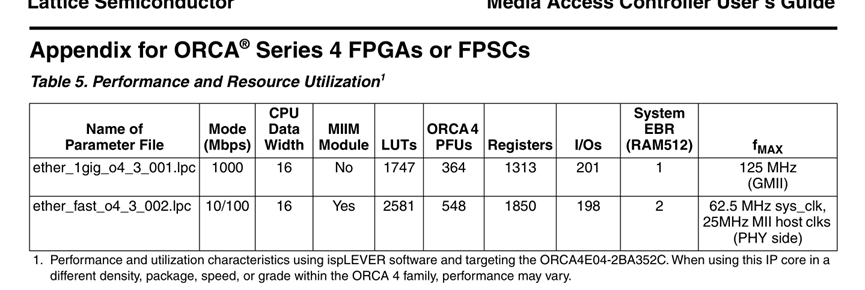

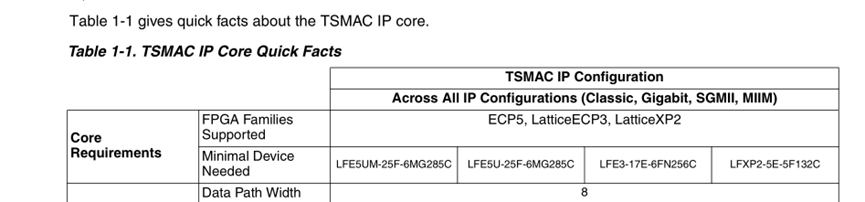

Lattice的发展过程中更新迭代了很多产品,就目前而言,一个IP核可能有三份文档,应用在不同的平台。以tri speed ethernet mac ip为例,他有三个文档,不同的文档适用不同的产品类型,大致是远古时代的ispLever开发的ORCA系列,还有latticeECP系列,以及新一代的其他器件。开发IP的时候需要找对应的文档开发,有些区别不大,但有的甚至信号名称都不一样。

- Tri-Speed Ethernet IP IP Version: v2.0.0

- 10/100 and 1Gig Ethernet Media Access Controller

- Tri-Speed Ethernet MAC IP User Guide

6.传送门

- 我的主页

- Lattice进阶之路汇总导航

| END |

📡文章原创,首发于CSDN论坛。

📡欢迎点赞♥♥收藏⭐⭐打赏💵💵!

📡欢迎评论区或私信指出错误💉,提出宝贵意见或疑问😱。