LPDDR5训练过程

1 整体流程

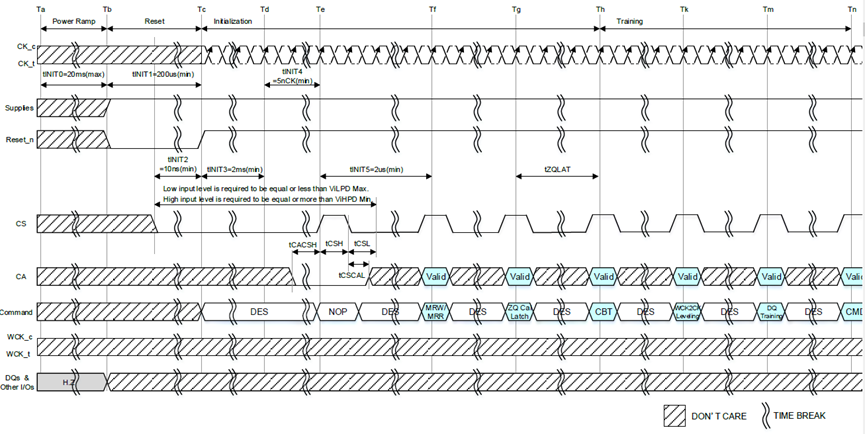

2 上电初始化

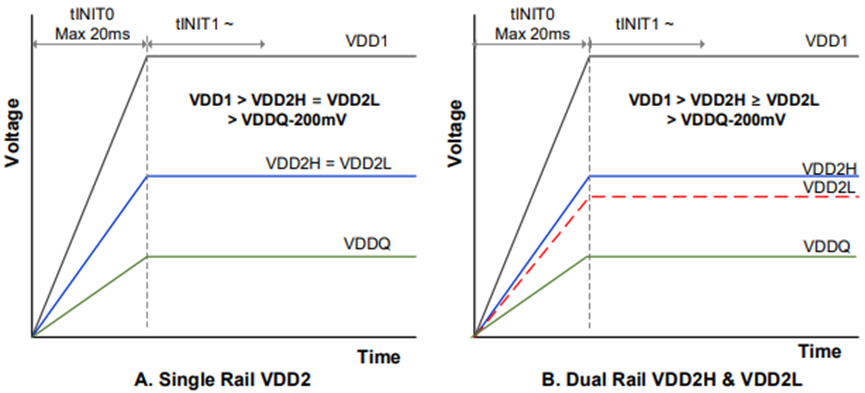

上电时,RESET_N引脚需保持低电平(≤0.2*VDD2H)状态,VDD2H电压参考使用书册,以K3LKCKC0BM-MGCP为例,VDD2H为1.05V。

VDD1、VDD2H/2L、VDDQ严格按照如下时序进行上电。

供电稳定后,RESET_N至少保持tINIT1(200us)才可释放,RESET_N置高后,CK差分对需要保持在互补电平,且在CS的第一个指令前保持稳定(至少5个时钟周期)。

Tinit5(2us)后,第一条MRW指令或者MRR指令开始发起。

3 ZQ校准

LPDDR5的ZQ校准发生在上电完成后,自动运行,ZQ校准分为两种后台自动校准和基于命令校准。

ZQ校准分为两方面:输出驱动器阻抗校准和CA/DQ ODT 阻抗校准。

- 输出驱动器阻抗校准

在 LPDDR5 SDRAM 的工作过程中,输出驱动器需要将内部的电信号转换为合适的驱动能力,以驱动外部的电路。通过 ZQ校准,可以使输出驱动器的阻抗在不同的工艺、温度和电压条件下,都能保持在合适的水平,确保信号传输的准确性和稳定性。例如,在不同的生产工艺下,芯片内部的晶体管特性会有所差异,导致输出驱动器的阻抗不一致,通过 ZQ 校准就能对这种差异进行补偿。

- CA/DQ ODT 阻抗校准

CA(Command/Address)总线和 DQ(Data)总线用于在 SDRAM 和外部控制器之间传输命令、地址和数据等信息。ODT(On-Die Termination,片上终端) 阻抗起到匹配信号传输线路阻抗的作用,减少信号反射,提高信号质量。ZQ 校准可以对 CA/DQ ODT 阻抗进行调整,使其适应不同的工作环境,保证数据传输的可靠性 。比如在不同的温度和电压条件下,线路的阻抗特性会发生变化,ZQ 校准能让 ODT 阻抗与之匹配,优化信号传输。

当 LPDDR5 SDRAM 的电压或温度因系统环境变化而改变时,可能需要重新进行 ZQ 校准。ZQ 校准仅能在 VDDQ 电压设置为标称 0.5V或更高(即 DVFSQ 未激活时)时执行。

在后台校准模式下,若 VDDQ 设置为低于 0.5V 的标称电平,或者 VDDQ 在不同电平间变化(即 DVFSQ 激活时),内存控制器需通过设置 ZQ 停止来暂停校准。

在基于命令的模式下,当 DVFSQ 激活时,除非设置了 ZQ 停止,否则 ZQ 校准启动命令为非法命令。

DVFS(Dynamic Voltage and Frequency Scaling):动态电压频率调节。

ZQ校准