PCIe Base Specification解析(十一)

文章目录

- 4.2.6.4 Recovery

- 4.2.6.4.1 Recovery.RcvrLock

- 4.2.6.4.2 Recovery.Equalization

- 4.2.6.4.2.1 Downstream Lanes

- 4.2.6.4.2.1.1 Phase 1 of Transmitter Equalization

- 4.2.6.4.2.1.2 Phase 2 of Transmitter Equalization

- 4.2.6.4.2.1.3 Phase 3 of Transmitter Equalization

- 4.2.6.4.2.2 Upstream Lanes

- 4.2.6.4.2.2.1 Phase 0 of Transmitter Equalization

- 4.2.6.4.2.2.2 Phase 1 of Transmitter Equalization

- 4.2.6.4.2.2.3 Phase 2 of Transmitter Equalization

- 4.2.6.4.2.2.4 Phase 3 of Transmitter Equalization

- 4.2.6.4.3 Recovery.Speed

- 4.2.6.4.4 Recovery.RcvrCfg

- 4.2.6.4.5 Recovery.Idle

- 4.2.6.5 L0

- 4.2.6.6 L0s

- 4.2.6.6.1 Receiver L0s

- 4.2.6.6.1.1 Rx_L0s.Entry

- 4.2.6.6.1.2 Rx_LOs.ldle

- 4.2.6.6.1.3 Rx_LOs.FTS

- 4.2.6.6.2 Transmitter L0s

- 4.2.6.6.2.1 Tx_L0s.Entry

- 4.2.6.6.2.2 Tx_LOs.ldle

- 4.2.6.6.2.3 Tx_L0s.FTS

- 4.2.6.7 L1

- 4.2.6.7.1 L1.Entry

- 4.2.6.7.2 L1.Idle

- 4.2.6.8 L2

- 4.2.6.8.1 L2.Idle

- 4.2.6.8.2 L2.TransmitWake

- 4.2.6.9 Disabled

- 4.2.6.10 Loopback

- 4.2.6.10.1 Loopback.Entry

- 4.2.6.10.2 Loopback.Active

- 4.2.6.10.3 Loopback.Exit

- 4.2.6.11 Hot Reset

- 4.2.7 Clock Tolerance Compensation

- 4.2.7.1 SKP Ordered Set for 8b/10b Encoding

- 4.2.7.2 SKP Ordered Set for 128b/130b Encoding

- 4.2.7.3 Rules for Transmitters

- 4.2.7.4 Rules for Receivers

- 4.2.8 Compliance Pattern in 8b/10b Encoding

- 4.2.9 Modified Compliance Pattern in 8b/10b Encoding

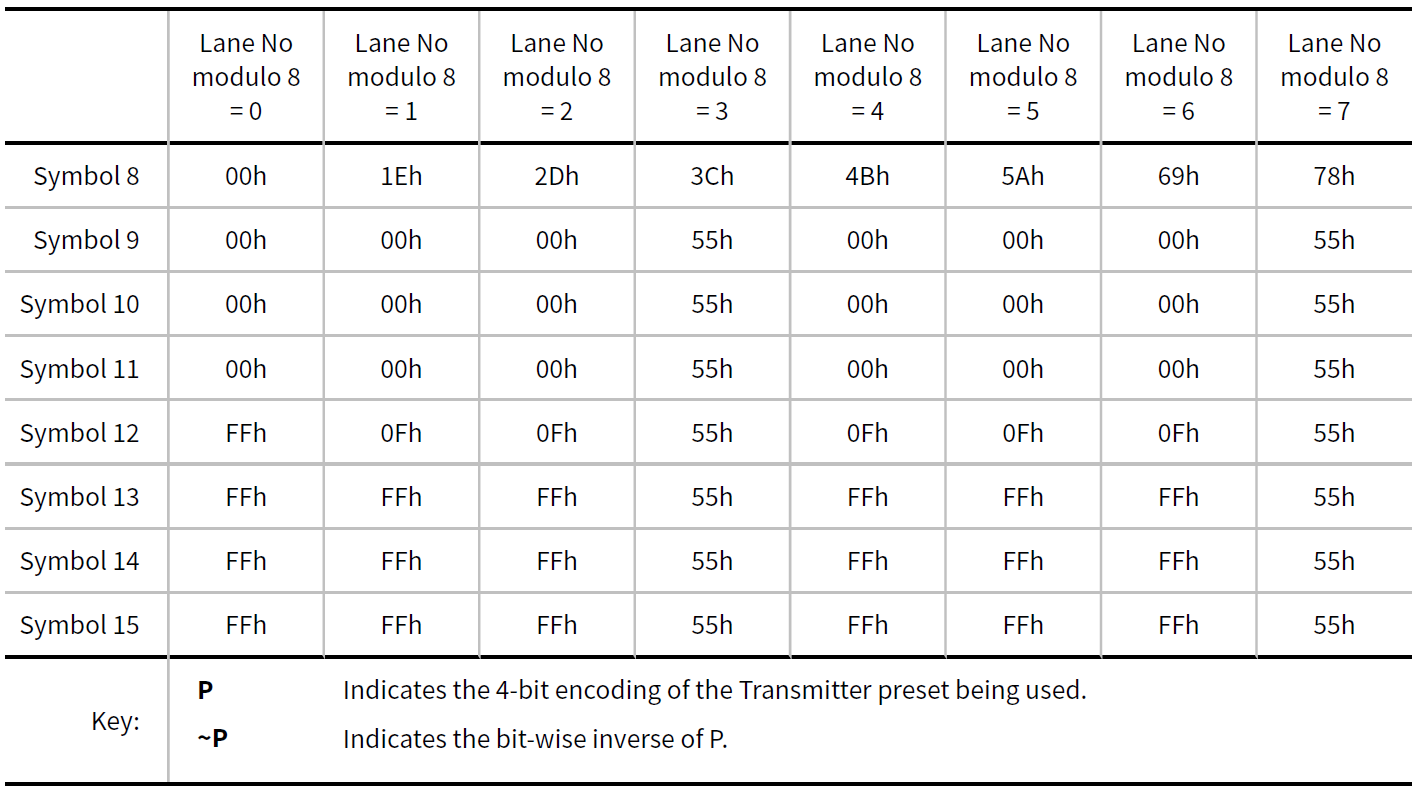

- 4.2.10 Compliance Pattern in 128b/130b Encoding

- 4.2.11 Modified Compliance Pattern in 128b/130b Encoding

- 4.2.12 Jitter Measurement Pattern in 128b/130b

- 4.2.13 Lane Margining at Receiver

- 4.2.13.1 Receiver Number, Margin Type, Usage Model, and Margin Payload Fields

4.2.6.4 Recovery

在Recovery状态,发送器和接收器都使用已配置的链路和通道号以及支持的数据速率发送和接收数据。Recovery允许已配置的链路根据需要调整数据速率,重新建立bit lock、Symbol lock或 Block alignment、Lane-to-Lane de-skew。Recovery 还用于设置新的N_FTS值,并进入Loopback、Disabled、Hot Reset和Configuration 状态。

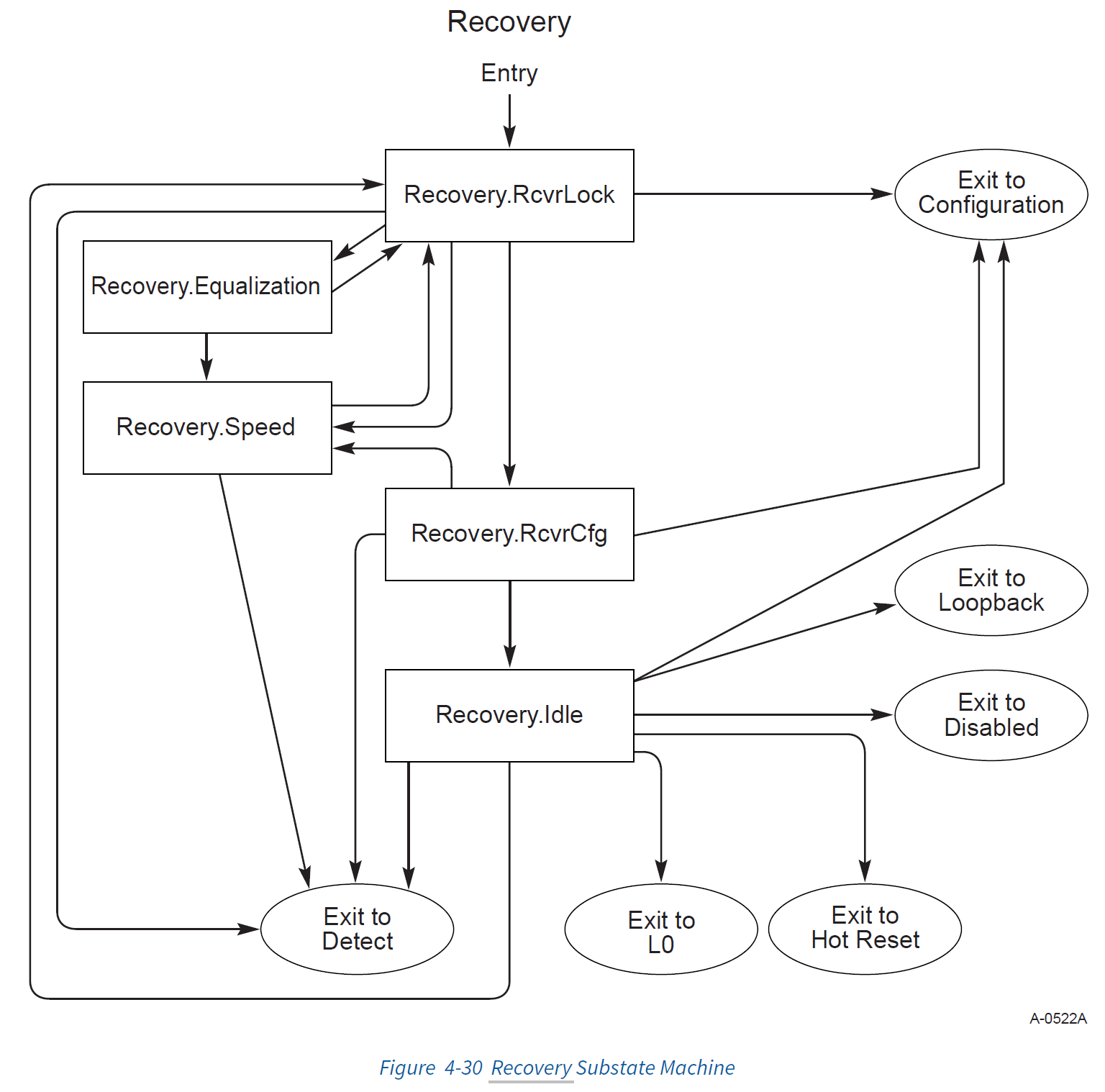

Recovery 状态的子状态机如 Figure4-30所示。

4.2.6.4.1 Recovery.RcvrLock

如果链路以8.0GT/s或更高的数据速率运行,则接收器必须在获得该Lane的Block Alignment 后才考虑接收任何TS1或TS2有序集。如果从L1或Recovery.Speed或LOs进入此子状态,则必须在退出电气空闲状态后获得Block Alignment。如果从LO进入此子状态,则必须在最后一个数据流结束后获得Block Alignment。

如果在data rate为8.0GT/s或更高速率下工作:

如果start_equalization_w_preset =1b:

Upstream Port必须使用在Recovery.RcvrCfg状态从接收到的适当的八个连续TS2有序集中携带的发送器preset值(如果协商为8.0GT/s,则为EQ TS2;如果协商为32.0 GT/s且为 equalization bypass to highest datarate,则为EQ TS2,或者如果协商为16.0GT/s或32.0GT/s,则为128b/130b EQTS2),如Chapter 8所述。接收到保留或不支持的发送器预设值的通道必须使用实现特定的方法来选择支持的发送器预设设置,以便在它开始以需要执行均衡的数据速率开始发送时使用。

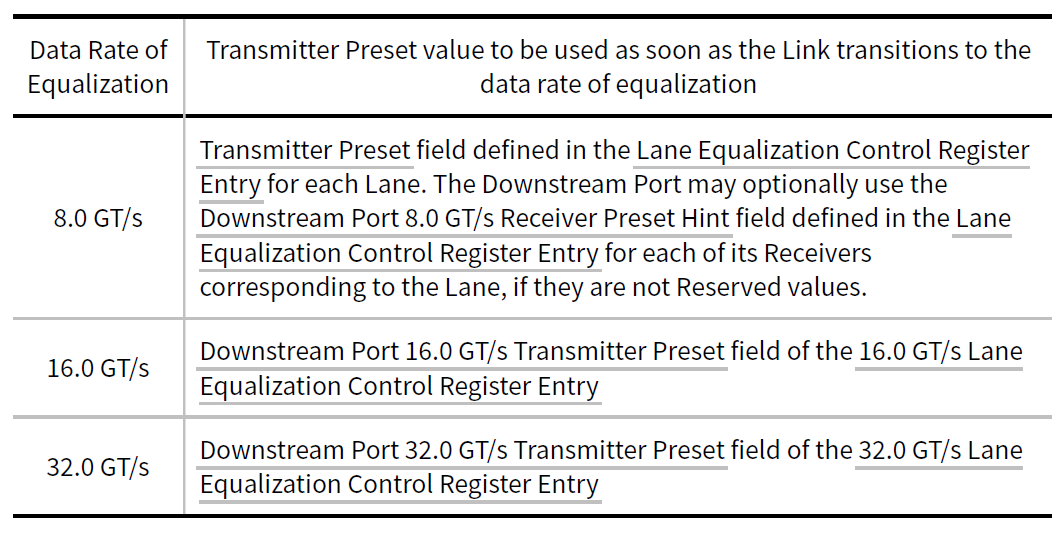

Downstream Port 开始以必须执行均衡的数据速率进行传输时,必须按照以下规则使用发送器预设设置:

1.如果均衡的数据速率为16.0GT/s或32.0GT/s,并且接收到八个连续的EQTS2有序集(对于要进行到32.0GT /s的均衡旁路的情况)或128b/130b EQTS2有序集,且它们携带在Recovery.RcvrCfg进行的最新转换中具有受支持的发送器预设值,则必须使用来自那些EQTS2或128b/130b EQ TS2有序集的发送器预设值。

2.否则,如果支持在适当的Lane Equalization Control Register Entry的Downstream Port Transmitter Preset 字段中定义的Transmitter Preset值(如下所述),则必须使用它:

3.否则,请使用特定于实现的方法来选择支持的发送器预设设置。

下游端口必须确保其符合Chapter 8中的预设定义。

下个状态跳转到Recovery.Equalization状态。

否则:

发送器必须使用最后一次均衡过程结束时商定的系数设置。

如果此子状态是从Recovery.Equalization中进入的,则在传输的TS1有序集中,下游端口必须将Pre-cursor、Cursor 和Post-cursor Coefficient 字段设置为当前的发送器的设置,并且如果在Recovery.Equalization的Phase 2中最后接受的请求是一个preset请求,它必须将Transmitter Preset 设置为该请求的可接受预设。

建议在此子状态下,在传输的TS1有序集中,所有端口都将Pre-cursor、Cursor和Post-cursorCoefficient字段设置为当前的发送器的设置,并将Transmitter Preset位设置为最新的预设值。

Upstream Port 在所有已配置的Lane上收到的8个连续的TS1有序集有以下特征,则状态机跳转到Recovery.Equalization 状态。

接收到的TS1有序集中的Link number和Lane number与每个通道上发送的TS1有序集中的Link number和Lane number 匹配。

speedchange=0b∘

EC字段不能等于00b。

IMPLEMENTATION NOTE

Redoing Equalization

Downstream Port 可以使用此条款通过软件帮助或某些其他特定于实现的方式来重做发送器均衡过程的某些部分以避免超时,同时确保链路上没有正在传输的事务。

Downstream Port 在直接定向且 Recovery.RcvrLock状态不是从Configuration.ldle或Recovery.Idle进入的情况下跳转到Recovery.Equalization状态。在开始传输 Recovery.Equalization要求的TS1有序集之前,端口必须确保由于处于Recovery.RcvrLock 状态而传输的EC=00b的TS1有序集不超过2个。

在此子状态下,发送器在所有已配置的Lane上发送 Configuration 完成时设置好的Link number和Lane number的TS1有序集。如果变量directed_speed_change=1b,则TS1有序集的speed_change字段(Data Rate Identifier 字符的bit7)就必须设置为1b。如果在任意Lane上收到8个连续speed_change字段设置为1b的TS1有序集,则directed_speed_change 变量设置为1b。只能通告那些能够可靠支持的大于2.5GT/s的数据速率。发送的TS1有序集中的N_FTS表示在当前数据速率下快速恢复需要的FTS数量。允许设备更改进入此子状态时通告的支持的数据速率。

当支持 equalization bypass to highest data rate 时,Downstream Port 想通过重做均衡把数据速率从2.5 GT/s或5.0 GT/s切换到8.0 GT/s或32.0 GT/s,则必须:

发送EQ TS1 Ordered Set,并将 speed_change位设置为1b,并通告以下数据速率:

如果重做均衡用于8.0GT/s数据速率,则通告8.0 GT/s Data Rate Identifier。

如果重做均衡用于32.0GT/s数据速率,则通告32.0 GT/s Data Rate Identifier。

如果均衡重做尝试是由硬件(如Section 4.2.3所述)启动的,则硬件必须在启动尝试之前确保数据速率为2.5GT/s或5.0 GT/s。

如果按Section 4.2.3中所述由软件机制启动了均衡重做尝试,则在启动尝试之前,软件必须确保数据速率为2.5 GT/s 或5.0GT/s。

打算以数据速率从8.0GT/s更改为16.0GT/s或从16.0 GT/s更改为32.0GT/s的方式进行重做均衡的下游端口必须:

发送将Equalization Redo 设置为1b,speed_change位设置为1b的TS1 Ordered Set,并通告将执行均衡重做的Data Rate Identifier (16.0 GT/s或32.0 GT/s)。

如果均衡重做尝试是由硬件(如Section 4.2.3中所述)启动的,则硬件必须在启动重做均衡尝试之前确保数据速率为以下值:

如果均衡重做是为16.0GT/s数据速率而做的,则必须保证数据速率为8.0GT/s。

如果均衡重做是为32.0GT/s数据速率而做的,则必须保证数据速率为16.0GT/s。

如果按Section 4.2.3中所述由软件机制启动了均衡重做尝试,则在启动重做均衡尝试之前,软件必须确保数据速率为以下值:

如果均衡重做是为16.0GT/s数据速率而做的,则必须保证数据速率为8.0GT/s。

如果均衡重做是为32.0GT/s数据速率而做的,则必须保证数据速率为16.0GT/s。

上游端口必须在它在Recovery.RcvrCfg中传输的TS2有序集中通告其最高数据速率支持,并且可选地在此子状态下传输在TS1有序集合中通告最高的数据速率支持,除非上游端口确定与最高数据速率无关的问题,如果均衡接收到的八个连续的有序集是以下之一,则均衡将阻止它在要求执行均衡的最高数据速率下可靠运行:

将speed_change位设置为1b的EQTS1或EQTS2有序集。

Equalization Redo 设置为1b的TS1 Order Set或speed_change 设置为1b的128b/130b EQ TS2 Ordered Set。

在其他情况下,设备不得在此子状态下或在Recovery.RcvrCfg或Recovery.Equalization 子状态下更改支持的数据速率值。进入该子状态后,successful_speed_negotiation 变量将重置为0b。

IMPLEMENTATION NOTE

Handling a Request to Advertise 8.0 GT/s Data Rate Identifier

如果没有通告8.0 GT/s Data Rate Identifiers的 Upstream Port 接收到具有8.0 GT/s Data Rate Identifiers 并且在 Recovery.RcvrLock状态设置speed_change字段为1的EQTS,则表明Downstream Port 正在尝试切换链路速率达到8GT/s,以执行8.0 GT/s链路均衡过程。如果由于某种原因Upstream Port 无法或不愿意切换到在TS2有序集中通告8.0 GT/s Data Rate Identifiers,则在状态机转换到Recovery.RcvrCfg时会传输该数据,因此在本轮Recovery 状态将不执行8.0GT/s的链路均衡过程。这可能会导致Downstream Port永久放弃将链路速度更改为8.0GT/s并执行8.0 GT/s链路均衡过程的尝试,导致直到链路转换到Detect 并重新开始一个链路训练之前,链路速率都低于8.0 GT/s。建议如果Upstream Port由于某种暂时原因而无法或不愿意在上述条件下切换为通告8.0 GT/s Data Rate Identifiers,并且不打算禁止链路以8.0GT/s的速度运行,则建议它在合理的情况下执行以下某个操作:

如果Upstream Port 支持用于执行链路均衡过程的停顿保证机制(Quiesce Guarantee mechanism),转换到Recovery并在其发送的TS中将speed_change位设置为1b,并通告8.0GT/s的Data Rate Identifiers。如果在将速度更改为8.0GT/s之后且以8.0 GT/s的速度进入Recovery.RcvrCfg之前未进入过 Recovery.Equalization(Downstream Port 没有把状态机定向到Recovery.Equalization),则应在Recovery.RcvrCfg中以8.0GT/s的速率发送的Request Equalization和Quiesce Guarantee 字段设置为1的TS2有序集,以便请求Downstream Port启动链路均衡过程。

进入Recovery状态并通告8.0 GT/s的 Data Rate Identifiers,并将speed_change位清除为0b。Downstream Port随后可以将速度更改为8.0GT/s,并执行链路均衡过程,尽管不能保证会这样做。

处理通告16.0GT/s(或32.0 GT/s) Data Rate Identifier的请求的过程与8.0 GT/s Data Rate Identifier 以 16.0 GT/s (或32.0 GT/s) Data Rate Identifier 替换8.0 GT/s相似,同理用于128b/130b EQTS2代替EQTS。

Upstream Port 必须将其传输的TS1有序集的 Selectable De-emphasis字段设置为与所需的5.0GT/s数据速率下的去加重级别相匹配。Upstream Port 请求一个去加重级别的机制是特定于实现的。还必须注意,由于TS1有序集在链路传输中可能有bit error,所以Upstream Port的请求可能无法到达Downstream Port,因此,当速度切换时,Upstream Port可能会尝试在随后进入Recovery 后重新请求期望的去加重级别。如果Downstream Port 打算在Recovery.RcvrCfg中使用 Upstream Port的去加重信息,则它必须记录在此状态下接收到的Selectable De-emphasis字段的值。

Link Control 2 寄存器的Transmit Margin字段在进入该子状态时进行采样,并在进入该子状态的192ns之内对发送封装引脚生效,并且一直保持有效,直到之后从LO,LOs或L1进入该子状态后再重新采样。

激活任何无效的通道后,发送器必须等待其TX共模电压建立,然后退出电空闲并发送TS1有序集。

从L1.2L1 PM子状态退出时,允许在L1.0期间被动建立共模,并在Recovery期间主动建立共模。为了确保在Recovery.RcvrLock 中已建立共模,下游端口必须维护一个计时器,并且下游端口必须发送TS2训练序列,直到下游端口已开始传输TS1训练序列为止,直到经过至少TcOMMONMODE为止,在已配置链路的任何通道上检测到电气空闲退出。参见Section 5.5.3.3。

实现时必须注意,在对端进入Recovery.RcvrLock之后,新的Transmit Margin字段在192ns内生效后,早期的bit lock和Symbol or Block alignment之后,电压电平可能会发生变化。在这些情况下,接收器需要重新获取bit lock和Symbol or Block alignment。

a. Note:对于发起速度更改的一侧,在LO或L1状态下,directed_speed_change 变量设置为1b。对于未启动速度更改的一侧,如果接收到的TS有序集的speed_change设置为1b,则在此子状态中将directed_speed_change设置为1b。在Recovery.Speed子状态下,该位复位为0b。

b.从LO进入此子状态后,设备必须接收它收到的所有TLP和DLLP,然后再接收第一个TS有序集。如果使用128b/130b 编码,则任何接收到的TLP和DLLP都必须遵守Section 4.2.2.3中128b/130b编码的成帧规则。

如果在所有已配置的Lane上收到8个连续的与在这些Lane上发送的Link number和Lane number一致的TS1或TS2有序集,并且携带的speed_change字段值与directed_speed_change 变量相等,并且在当前速率为8.0GT/s或更高的情况下EC字段值为00b,则下个状态跳转到Recovery.RcvrCfg状态。

如果Extended Synch字段设置为1b,则发送器在进入Recovery.RcvrCfg之前至少必须发送1024个连续的TS1有序集。

如果从Recovery.Equalization中进入此子状态,则Upstream Port必须评估所有接收到八个TS1有序集的通道所接收到的equalization coefficient或preset,并注意它们是否不同于均衡过程中Phase 2接收的最终的equalization coefficient 或preset。注意:通过设置TS2有序集的Request Equalization字段,在Recovery.RcvrCfg中报告不匹配。

否则,在24ms超时后,执行以下操作:

如果下面两个条件满足,则状态机转换到Recovery.RcvrCfg状态:

在任何已配置的通道上接收到八个连续的TS1或TS2有序集,且这些有序集的Link number与Lanenumber与发送的一致,并且speed_change位等于1b。

当前工作的数据速率大于2.5 GT/s;或者在发送和接收的连续的八个TS1或TS2有序集中都设置了5.0GT/s或更高的data rate identifiers。

否则,如果自LO或L1进入Recovery以来操作速度尚未更改为相互协商的数据速率(即,changed_speed_recovery=0b),并且当前操作速度大于2.5GT/s,则下一个状态是Recovery.Speed。离开Recovery.Speed后将要使用的新数据速率为2.5 GT/s。

Note:这表示链路无法以当前数据速率(大于2.5 GT/s)运行,并且链路将以2.5 GT/s数据速 率运行。

否则,如果自LO或L1进入 Recovery以来操作速度已更改为相互协商的数据速率(changed_speed_recovery=1b;即到此子状态的速率已从Recovery.Speed获取),则下一个状态是Recovery.Speed。离开Recovery.Speed后要使用的新数据速率恢复为从LO或L1进入Recovery时的速度。

Note:这表明链路无法以新的协商数据速率运行,并且将恢复为从LO或L1进入Recovery时的 数据速率。

否则,如果任何已配置通道已接收到至少一个Link number和Lane number与正在发送的相匹配TS1或TS2有序集,且自进入Recovery以来工作速率尚未更改为相互协商的数据速率,并且至少满足以下条件之一,则下一个状态是Configuration 并且directed_speed_change 变量重置为0b:

directed_speed_change 变量等于0b,并且接收到的TS1或TS2有序集上的speed_change位等于0b。

当前的工作数据速率为2.5 GT/s,而2.5 GT/s数据速率是已发送的TS1有序集和已接收的TS1或TS2有序集中最高的通告的数据速率。

否则,下个状态是Detect状态。

IMPLEMENTATION NOTE

Example Showing Speed Change Algorithm Between 2.5 GT/s and 5.0 GT/s

假设链路连接了两个数据速率大于5.0GT/s的组件A和B。链路以2.5GT/s的速率训练到LO。A准备将链路切换到大于5.0GT/s 的速率上,于是把directed_speed_change设置为1b,然后从LO切换到Recovery.RcvrLock。A发送speed_change字段置1的TS1有序集并通告所支持的三种数据速率。B在LO状态下收到第一个TS1有序集然后进入Recovery.RcvrLock状态。最开始的时候B 发送speed_change字段置0的TS1有序集。当B收到八个连续的speed_change字段置1,B就开始发送speed_change字段置1的TS1有序集且通告支持的三种数据速率。然后B将进入Recovery.RcvrCfg,之后进入Recovery.Speed。A等待从B接收八个连续的speed_change字段置1的TS1有序集或TS2有序集,然后A将进入Recovery.RcvrCfg,接着进入Recovery.Speed。A和B都进入Recovery.Speed状态且记录了8.0GT/s数据速率为它们可工作的最大速率。在Recovery.Speed状态directed_speed_change 变量设置为0b。当它们从Recovery.Speed 切换到Recovery.RcvrLock 状态时,它们会工作在8.0GT/s下且发送的TS1有序集的

speed_change字段置为 0b。 如果两端都稳定工作在8.0GT/s,它们将转移到Recovery.RcvrCfg,然后经过Recovery.Idle进入 LOo 但是,如果B Symbol lock失败,它会在Recovery.RcvrLock状态超时,然后进入Recovery.Speed状态。A将会进入Recovery.RcvrCfg,但它会在B进入Recovery.RcvrLock后A收到工作在8.0GT/s的TS1有序集后看到电气空闲。这会导致A进入Recovery.Speed。当第二次进入Recovery.Speed后,两侧就返回到之前进入Recovery状态时的工作速率(即2.5GT/s)。两侧都在2.5GT/s的工作速率下从Recovery进入 LOo∼A将第二次置起directed_speed_change 变量,请求8.0GT/s的数据速率,经过同样的步骤,在建立8.0GT/s 数据速率时失败并且以2.5GT/s的数据速率返回到 LO∘。但是在做第三次尝试的时候,A将只通告2.5GT/s和5GT/s两种速率并且成功建立工作在5GT/s的链路且进入 LO∘ 但是,如果因为热插拔事件导致状态机进入Detect状态,则必须通告支持从2.5GT/s 到8GT/s的能力。

4.2.6.4.2 Recovery.Equalization

4.2.6.4.2.1 Downstream Lanes

在进入Recovery.Equalization 子状态时:

当前的phase就是Phase 1。

Link Status 2寄存器的 Equalization Phase 1 Successful, Equalization Phase 2 Successful, Equalization Phase 3 Successful, Link Equalization Request 和 Equalization Complete 字段,以及Link Control 3 寄存器的 Perform Equalization字段都设置为 Obo

equalization_done_8GT_data_rate 变量设置为1b。

start_equalization_w_preset设置为0b。

4.2.6.4.2.1.1 Phase 1 of Transmitter Equalization

在该Phase,发送器用Downstream Port的Lane Equalization Control 寄存器的 Transmitter Preset 字段的值来发送TS1有序集。在发送的TS1有序集中,EC字段为01b,Transmitter Preset就设置为对应Lane的寄存器中的值,FS、LF和Post-cursor Coefficient 字段的值设置为与Transmitter Preset字段相关的值。

如果 Downstream Port 需要时间来稳定其接收器逻辑,则进入Phase 1后,允许Downstream Port 最多等待500ns,然后评估接收到的TS1有序集的信息。

如果所有已配置的上接收到两个连续的EC=01b的TS1有序集并且Downstream Port想执行 Phase 2和Phase 3,则下个状态跳转到Phase 2。

接收器必须完成其比特锁定过程,然后在其接收器引脚上收到第一个有效有序集合的第一比特后的2ms内识别有序集。

Link Status 2 寄存器的 Equalization Phase 1 Successful 字段设置为 1b。

如果 Downstream Port 想要调整Upstream Port的发送器的参数,则两个连续的TS1有序集中的FS和LF值用于Phase3。

如果所有已配置的上接收到两个连续的EC=01b的TS1有序集并且 Downstream Port 不想执行 Phase 2和Phase 3,则下个状态跳转到Recovery.RcvrLock。

Link Status 2 寄存器的 Equalization Phase 1 Successful, Equalization Phase 2 Successful, Equalization Phase 3 Successful,Link Equalization Request 和 Equalization Complete字段都设置为 1b。

Note:转换到Recovery.RcvrLock 可能用于这种场景:Downstream Port基于平台和信道特性的原因知道自己不用执行Phase 2和Phase 3过程。

否则,在24ms超时后,状态机跳转到Recovery.Speed。

successful_speed_negotiation 设置为 0b

Link Status 2 寄存器的 Equalization Complete 字段设置为 1b。

4.2.6.4.2.1.2 Phase 2 of Transmitter Equalization

发送器根据如下规则,按Lane独立发送EC=10b与相关 coefficient 设置的TS1有序集。

如果从进入Phase 2开始收到了两个连续的EC=10b的TS1有序集,或者收到了两个preset或一组coefficient(比如由Use Preset 指定)的值与最后收到的两个EC=10b的TS1有序集中携带的值不同的EC=10b的TS1有序集:

如果最近两个连续的TS1有序集合中要求的preset或coefficient是合法且受支持的(请参阅Section 4.2.3),则执行以下操作:

将发送器设置更改为所需的preset或coefficient,以使新的设置在接收器引脚上收到第二个请求新设置的TS1有序设置的最后位置后的500ns内对发送器引脚有效。更改发送器设置不得使发送器引脚上的任何非法电压电平或参数超过1ns。

在传输的TS1有序集中体现新的设置,并将Reject Coefficient Values 字段设置为0b。

否则:不用改变发送的设置值,但是需要在TS1有序集中体现preset或coefficient值的请求,并且把Reject Coefficient Values 设置为1b。

否则,当前的preset和 coefficient值会被用于发送器。

如果所有已配置的上接收到两个连续的 EC=11b 的TS1有序集,则下个状态跳转到Phase 3。

Link Status 2 寄存器的Equalization Phase 2 Successful字段设置为 1b。

否则,在32ms超时后状态机跳转到Recovery.Speed状态。这个超时容差为 0∼ms∼+4∼ms。

successful_speed_negotiation 设置为0b。

Link Status 2 寄存器的 Equalization Complete 字段设置为 1b。

4.2.6.4.2.1.3 Phase 3 of Transmitter Equalization

-

发送器发送 EC=11b的TS1有序集。

-

Port必须在每个通道上独立评估并获得最佳设置。根据Section 4.2.3和Section4.3中的规则评估合法的新preset或coefficient 的设置:

通过将Transmitter Preset 字段设置为所需的值并将Use Preset字段设置为1b来请求一个新的preset。或者,通过将Pre-cursor、Cursor和Post-Cursor Coefficient字段设置为所需的值,并将Use Preset字段设置为0b,以请求一组新的coefficient。发出请求后,必须连续请求至少1μs或直到请求评估完成为止(以较晚者为准)。

等待所需的时间(500ns加上往返延迟,包括通过Downstream Port的逻辑延迟),以确保(如果接受)Upstream Port 正在使用请求的设置进行传输。获取Block Alignment,然后评估传入的有序集。Note:由于在切换到请求的设置期间传入的比特流可能是非法的,因此Downstream Port 可能忽略在此等待期间收到的任何内容。因此,在此等待周期完成之后需要验证 Block Alignment。

如果接收到两个连续的TS1有序集,且TransmitterPreset字段(用于preset请求)或Pre-cursor、Cursor和Post-Cursor 字段(用于coefficient请求)与请求的字段相同,并且Reject CoefficientValues 字段设置为0b,则请求的设置被接受并且需要进行评估。如果接收到两个连续的TS1有序集,且Transmitter Preset字段或Pre-cursor、Cursor和 Post-Cursor 字段与请求的字段相同,并且Reject Coefficient Values 字段设置为1b,则请求的设置被拒绝,建议 Downstream Port 请求其他preset或coefficient的组合。但是,允许Downstream Port在不发出任何其他请求的情况下退出此Phase。Downstream Port 负责根据其评估标准和要求将其发送的TS1有序集中的Reset EIEOS Interval Count字段设置为1b。

IMPLEMENTATION NOTE

Reset EIEOS and Coefficient/ Preset Requests

当端口想要更长的PRBS码型时,可以将Reset EIEOS Interval Count字段设置为1b,然后在需要获取块对齐时将其清除。

在此Phase发送的所有TS1有序集都是请求。第一个请求可以是新的preset或coefficient请求,也可以是通过反映两个连续的TS1有序集(EC=11b)中接收到的设置来保持当前链路伙伴发射机设置的请求,这些设置导致切换到Phase 3。

从发送请求到评估完成,每个preset或coefficient请求所花费的总时间必须少于2ms。在优化的最后阶段需要更长评估时间的实现可能会继续请求相同的preset或coefficient设置(超过2ms的限制),但在此阶段必须遵守24ms的超时时间,并且此例外不得超过两次。如果请求者无法在超时时间内接收到有序集,则可以假定所请求的设置在该通道中不起作用。

所有新的preset或coefficient设置必须同时显示在所有已配置的通道上。如果任何给定的通道不想在那时更改设置,则可以继续发送当前的preset或coefficient作为其新值。

如果所有已配置的Lane都工作在最佳设置下则下个状态为Recovery.RcvrLock。

Link Status 2 寄存器的 Equalization Phase 3 Successful和Equalization Complete 字段设置为1b。

否则,在24ms超时后状态机跳转到Recovery.Speed状态。这个超时容差为-0ms~+2ms。

successful_speed_negotiation 设置为0b。

Link Status 2 寄存器的Equalization Complete 字段设置为1b。

4.2.6.4.2.2 Upstream Lanes

在进入Recovery.Equalization 子状态时:

-

当前的phase就是Phase 0。

-

Link Status 2 寄存器的 Equalization Phase 1 Successful, Equalization Phase 2 Successful, Equalization Phase 3 Successful, Link Equalization Request 和 Equalization Complete 字段都设置为0b。

-

equalization_done_8GT_data_rate 变量设置为1b。

-

start_equalization_w_preset 设置为0b。

4.2.6.4.2.2.1 Phase 0 of Transmitter Equalization

在最近一次从2.5 GT/s或5.0 GT/s数据速率转换到8.0GT/s数据速率期间,发送器使用EQTS2有序集中接收的发送器preset 指定的发送器设置发送的TS1有序集。在TS1有序集中,EC字段设置为00b,每个通道的Transmitter Preset字段设置为在EQ TS2有序集中接收的值,以及Pre-cursor Coefficient、Cursor Coefficient和 Post-cursor Coefficient字段设置为与Transmitter Preset字段相对应的值。

·如果接收到的EQTS2有序集合的通道的Transmitter Preset 为保留值或不支持的值:意味着在发送的TS1有序集合中,Transmitter Preset 字段设置为接收到的Transmitter Preset,但Coefficient字段设置为与由特定选择的与特定实现有关的Transmitter Preset值。

如果通道没有接收到EQTS2有序集:意味着在发送的TS1有序集中,Transmitter Preset字段没有定义,且Coefficient 字段设置为与由特定选择的与特定实现有关的Transmitter Preset值。

如果Upstream Port需要时间来稳定其接收器逻辑,则允许其在进入Phase0之后等待长达500ns的时间,然后才能评估TS1有序集的接收器信息。

如果在所有已配置的Lane上收到两个连续的 EC=01b 的TS1有序集,则下个phase是Phase 1。

接收器必须完成其比特锁定过程,然后在其接收器引脚上收到第一个有效有序集的第一比特后的2ms内识别有序集。

如果Upstream Port想要调整 Downstream Port的发送器的参数,则两个连续的TS1有序集中的FS和LF值用于Phase 2。

否则,在12ms超时后进入Recovery.Speed状态。

successful_speed_negotiation 变量设置为 0b

Link Status 2 寄存器的Equalization Complete 字段设置为 1b。

4.2.6.4.2.2.2 Phase 1 of Transmitter Equalization

发送器使用在Phase0中确定的发送器设置发送TS1有序集。在TS1有序集中,EC字段设置为01b,每个通道的FS,LF和Post-cursor Coefficient 字段设置为该 Lane的当前发送器的设置值。

如果在所有已配置的Lane上收到两个连续的EC=10b的TS1有序集,则下个Phase为Phase 2。

Link Status 2 寄存器的 Equalization Phase 1 Successful字段设置为 1b。

如果在所有已配置的Lane上收到两个连续的EC=00b的TS1有序集,则下个状态为RecoveryRcvrLock

Link Status 2 寄存器的 Equalization Phase 1 Successful 字段和 Equalization Complete字段设置为 1b。

否则,在12ms超时后进入Recovery.Speed状态。

successful_speed_negotiation 变量设置为0b。

Link Status 2寄存器的Equalization Complete字段设置为 1b。

4.2.6.4.2.2.3 Phase 2 of Transmitter Equalization

发送器发送 EC=10b的TS1有序集。

Port必须在每个通道上独立评估并获得最佳设置。根据Section 4.2.3和Section 4.3中的规则评估合法的新preset或coefficient 的设置:

通过将Transmitter Preset字段设置为所需的值并将 Use Preset字段设置为1b来请求一个新的 preset0 或者,通过将Pre-cursor、Cursor和 Post-Cursor Coefficient字段设置为所需的值,并将Use Preset字段设置为0b,以请求一组新的coefficient。发出请求后,必须连续请求至少 1μs 或直到请求评估完成为止(以较晚者为准)。

等待所需的时间(500ns加上往返延迟,包括通过DownstreamPort的逻辑延迟),以确保(如果接受)UpstreamPort 正在使用请求的设置进行传输。获取Block Alignment,然后评估传入的有序集。Note:由于在切换到请求的设置期间传入的比特流可能是非法的,因此Downstream Port 可能忽略在此等待期间收到的任何内容。因此,在此等待周期完成之后需要验证 Block Alignment。

如果接收到两个连续的TS1有序集,且Transmitter Preset字段(用于preset请求)或Pre-cursor、Cursor和Post-Cursor 字段(用于coefficient请求)与请求的字段相同,并且Reject Coefficient Values字段设置为0b,则请求的设置被接受并且需要进行评估。如果接收到两个连续的TS1有序集,且Transmitter Preset字段或Pre-cursor、Cursor和 Post-Cursor 字段与请求的字段相同,并且Reject Coefficient Values字段设置为1b,则请求的设置被拒绝,建议Downstream Port 请求其他preset或coefficient的组合。但是,允许Downstream Port在不发出任何其他请求的情况下退出此Phase。Downstream Port 负责根据其评估标准和要求将其发送的TS1有序集中的Reset EIEOS Interval Count字段设置为1b。

IMMIPLEMENTATION NOTE

Reset EIEOS and Coefficient/ Preset Requests

当端口想要更长的PRBS码型时,可以将Reset EIEOS Interval Count字段设置为1b,然后在需要获取块对齐时将其清除。

在此Phase发送的所有TS1有序集都是请求。第一个请求可以是新的preset或coefficient请求,也可以是通过反映两个连续的TS1有序集(EC=10∼b)中接收到的设置来保持当前链路伙伴发射机设置的请求,这些设置导致切换到Phase 3。

·从发送请求到评估完成,每个preset或coefficient请求所花费的总时间必须少于2ms。在优化的最后阶段需要更长评估时间的实现可能会继续请求相同的preset或coefficient设置(超过2ms的限制),但在此阶段必须遵守24ms的超时时间,并且此例外不得超过两次。如果请求者无法在超时时间内接收到有序集,则可以假定所请求的设置在该通道中不起作用。

所有新的preset或coefficient设置必须同时显示在所有已配置的通道上。如果任何给定的通道不想在那时更改设置,则可以继续发送当前的preset或coefficient作为其新值。

如果所有已配置的Lane都工作在最佳设置下则下个phase为Phase 3。

Link Status 2 寄存器的 Equalization Phase 2 Successful字段设置为1b。

否则,在24ms超时后状态机跳转到Recovery.Speed状态。这个超时容差为 0∼ms∼+2∼ms。

successful_speed_negotiation设置为0b。

Link Status 2寄存器的Equalization Complete 字段设置为 1b。

4.2.6.4.2.2.4 Phase 3 of Transmitter Equalization

发送器发送 EC=11b且有如下规则设置的coefficient的TS1有序集:

如果从进入Phase 3开始收到了两个连续的EC=11∼b的TS1有序集,或者收到了两个preset或coefficient(比如由 Use Preset 指定)的值与最后收到的两个EC=11∼b的TS1有序集中携带的值不同的EC=11b的TS1有序集:

如果最近两个连续的TS1有序集合中要求的preset或coefficient是合法且受支持的(请参阅Section 4.2.3),则执行以下操作:

将发送器设置更改为所需的preset或coefficient,以使新的设置在接收器引脚上收到第二个请求新设置的TS1有序设置的最后位置后的500ns内对发送器引脚有效。更改发送器设置不得使发送器引脚上的任何非法电压电平或参数超过 1ns

在传输的TS1有序集中体现新的设置,并将Reject Coefficient Values 字段设置为0b。

否则:不用改变发送的设置值,但是需要在TS1有序集中体现preset或coefficient值的请求,并且把Reject Coefficient Values 设置为1b。

否则,当前的preset和coefficient值会被用于发送器。

如果所有已配置的Lane都收到两个连续的EC=00b的TS1有序集,则下个状态为Recovery.RcvrLock。

Link Status 2 寄存器的Equalization Phase 3 Successful和Equalization Complete 字段设置为1b。

否则,在32ms超时后状态机跳转到Recovery.Speed状态。这个超时容差为-0ms~+4ms。

successful_speed_negotiation 设置为0b。

Link Status 2 寄存器的 Equalization Complete 字段设置为1b。

4.2.6.4.3 Recovery.Speed

发送器进入电空闲状态,并一直保持此状态,直到接收器的Lane进入电空闲状态为止,然后在成功的速度协商的情况下(例如,success_speed_negotiation=1b)停留至少800ns,或者在不成功的速度协商中至少停留 6μs (即,successspeednegotiation=0b),但在那里停留的时间不得超过1ms。 仅在接收器的Lane进入电气空闲状态后,才允许将操作频率更改为新的数据速率。如果协商的数据速率为5.0GT/s,并且在full swing 模式下运行,则在select_deemphasis =0b的情况下选择-6dB的去加重等级,在select_deemphasis=1b的情况下选择-3.5dB的去加重等级。请注意,如果链路已经以两个端口支持的最高数据速率运行,则依然会执行Recovery.Speed,但不会更改数据速率。

如果当前数据速率为2.5GT/s或8.0GT/s,则必须在进入电空闲之前发送EIOS。 如果当前数据速率为 5.0GT/s,则在进入电空闲之前必须发送两个连续的EIOS。

在此状态下,DC共模电压不需要符合规范定义。

如果在任何已配置的通道上接收到EIOS,或者如Section 4.2.4.3中所述检测到/推断出电气空闲,则通道上存在电气空闲条件。

在成功进行速度协商(即,success_speed_negotiatioon=1∼b))后进入此子状态时,如果在指定的时间间隔(Table 4-11中定义)内未在任何已配置的通道中接收到TS1或TS2有序集,则可能会在接收器通道上推断出电气空闲状态。(这涵盖了链路正常运行并且双方都已成功接收TS有序集的情况。因此,在指定间隔内缺少TS1或TS2有序集可以解释为进入了电气空闲状态。)

如果在Table 4-11中指定的时间间隔内未在任何已配置的通道中至少检测到一次电气空闲退出,则在速度协商失败(即,successspeednegotiation=0b)之后进入此子状态。(这涵盖了以下情况:至少一方在接收由另一代理发送的TS有序集时遇到问题,因此在较长的时间间隔内没有退出电气空闲可以被视为等同于进入电气空闲。)

若满足上述在发送器的Lane不再需要处于电气空闲状态的条件,下个状态就跳转到Recovery.RcvrLock。

如果在成功进行速度协商后从Recovery.RcvrCfg中进入此子状态(即,success_speed_negotiatioon=1b),则新的数据速率将在所有已配置的通道上更改为链路两侧通告的最高公共数据速率。changed_speed_recovery变量设置为 1b。

否则,如果是第二次从LO或L1进入Recovery之后进入此子状态(即, changedspeedrecovery=1∼b) ,则新数据速率将是LTSSM从LO或L1进入Recovery时的数据速率。changed_speed_recovery 变量将重置为0b。

否则,新数据速率将为 2.5GT/so。changed_speed_recovery变量保持为 Ob∘。

Note:这代表以下情况:LO中的操作频率大于2.5GT/s,并且一侧无法以该频率操作,然后在Recovery.RcvrLock超时的情况下,它第一次从LO或L1进入该子状态。

48ms超时后进入Detect状态。

Note:正常情况下不会执行这个操作。

directed_speed_change=0b。Link Status 寄存器的Current Link Speed字段要反映当前的工作速率。

在发生链路带宽变化时,如果将recovery_speed_negotiation 设置为1b,并且在Recovery.RcvrCfg中接收到八个连续的Autonomous Change 设置为1b的TS2有序集,或出于自主原因由Downstream Port发起速度更改(非可靠因素且不是因为Link Retrain导致),则Link Status寄存器的 Link Autonomous Bandwidth Status 字段要设置为1b。

否则,在在发生链路带宽变化时,Link Status 寄存器的Link Bandwidth Management Status 字段要设置为1b。

4.2.6.4.4 Recovery.RcvrCfg

在这个子状态,发送器在所有已配置的Lane上发送在退出Configuration状态时使用的Link number与Lane number 值的TS2有序集。如果directed_speed_change已经为1b,则TS2有序集的speed_change字段也要设置为1b。TS2中携带的N_FTS值要反映在当前速率下快速恢复需要的FTS数。

如果下述条件全满足,Downstream Port就必须发送这样的EQTS2有序集:其Transmitter Preset和 Receiver Preset Hint字段的值由Upstream Port的 Transmitter Preset 和 Receiver Preset Hint 字段的值确定,而这些值又来自于各个Lane的Equalization Control 寄存器。

a. Downstream Port 会在Recovery.RcvrLock状态通告对8.0GT/s数据速率的支持,而Upstream Port则在退出 Detect状态后、在Configuration.Complete或者 Recovery.RcvrCfg状态中通告对8.0GT/s数据速率的支持,并且会在进入此子状态之前在任意已配置的Lane上收到八个连续的speed_change字段设置为1的TS1或TS2有序集。

b.如果要执行此操作,equalization_done_8GT_data_rate 变量设置为0b。

如果当前速率是8.0GT/s,并且在最近执行的均衡过程中检测到一个问题,则Upstream Port会把有序集中的Request Equalization 字段设置为1b。否则,Request Equalization 设置为0b。如果希望重新执行均衡过程,则Downstream Port或Upstream Port还需要把Request Equalization和Quiesce Guarantee 字段设置为1b,参阅Section 4.2.3。

在进入此子状态时,start_equalization_w_preset设置为0b。

在进入此子状态时,Downstream Port必须把select_deemphasis变量设置为Link Control 2 寄存器 Selectable De-emphasis 字段的值,或采用某种特定机制设置select_deemphasis的值,比如可以使用Upstream Port在八个连续的TS1有序集中携带的值。一个通告支持5GT/s数据速率的Downstream Port 必须在TS2有序集中传输与select_deemphasis值相同的Selectable De-emphasis字段。一个Upstream Port 如果因自主原因要改变链路带宽,就必须传输 Autonomous Change 字段设置为1b 的TS2有序集。

·对于支持Link width upconfigure的设备,如果directed_speed_change为0b,则建议在此子状态、Recovery.Idle子状态、Configuration.Linkwidth.Start 子状态开启当前inactive Lane集合上的电气空闲检测电路。这样做是为了在Link upconfigure 期间,不启动 upconfiguration的那一侧不会在Configuration.Linkwidth.Start子状态期间丢失发送的第一个EIEOS。

如果下述条件全满足,则状态机跳转到Recovery.Speed状态:

满足下述其中一个条件:

1)如果使用8b/10b编码,则需要在任意已配置的通道上收到八个连续的Data Rate Identifier相同的TS2有序集,并

且其speed_change字段设置为1b,且八个连续的TS2有序集是标准TS2有序集。

2)在所有已配置的通道上收到八个连续的Data Rate Identifier 相同的TS2有序集,且其speed_change字段设置为1b。

3)在任意已配置的通道上收到八个连续的Data Rate Identifier 相同的TS2有序集,并且其speed_change字段设置为1b,并且收到这8个连续的TS2有序集之后超过1ms。

当前数据速率大于2.5GT/s或者在发送和接收(连续八个)的TS2有序集中设置了大于2.5 GT/s的Data Rate Identifiers 字段。

对于8b/10b编码,在同一个已配置的通道中接收到一个speed_change设置为1b的TS2有序集后,至少发送了32个不被EIEOS中断的speed_change设置为1b的TS2有序集。对于128b/130b编码,在同一个已配置的通道中接收到一个将speed_change设置为1b的TS2有序集后,至少发送128个speed_change位设置为1b的TS2有序集。

在接收到的speed_change字段设置为1b的八个连续TS2有序集上通告的数据速率表明了另一个端口可以支持的数据速率。这些接收到的八个连续的TS2有序集中的Autonomous Change字段由Downstream Port给出,以便在Recovery.Speed子状态下由Link Status寄存器记录。Upstream Ports必须用select_deemphasis变量记录在这八个连续的TS2有序集中通告的Selectable De-emphasis 字段的值。在Recovery.Speed 状态切换的新速率是两个Port支持的最高的data rate。对于Upstream Ports,如果这八个连续的TS2有序集是EQTS2有序集,它必须把start_equalization_w_preset变量设置为1b并且把Lane Equalization Control寄存器的 Upstream Port Transmitter Preset 和Upstream Port Receiver Preset Hint字段的值更新为这些EQTS2有序集中携带的值。在执行链路均衡之前,首次以8.0GT/s的速度运行时,任何未接收到满足此条件的EQTS2有序集的已配置通道将使用与实现相关的preset值。如果equalization_done_8GT_data_rate 变量为0b,或因直接定向的原因,则Downstream Port必须将start_equalization_w_preset变量设置为1b。successful_speed_negotiation 变量要设置为1b。请注意,如果链路已经以两个端口支持的最高数据速率运行,则将执行 Recovery.Speed,但不会更改数据速率。如果使用128b/130b编码,并且在八个连续的TS2有序集中将 Request Equalization 位设置为1b,则设备必须将其与Quiesce Guarantee字段的值一起记录下来,并遵循Section 4.2.3中的规则。

如果下述两个条件全为真,则状态机跳转到Recovery.Idle状态:

在所有已配置的Lane上收到8个连续的与在该Lane上发送的Link number与Lane number 值相匹配、Data Rate Identifiers 相同的TS2有序集,并且满足以下两个条件中的一个:

收到的八个连续的TS2有序集的speed_change字段为0b。

当前数据速率为2.5GT/s,并且没有在接收到的八个连续TS2有序集中设置5.0 GT/s或更高的Data Rate Identifier,或者没有在发送的TS2有序集中设置5.0 GT/s或更高的Data Rate Identifier。

在收到一个TS2有序集后发送完16个连续的不被EIEOS中断的TS2有序集。在进入Recovery.ldle时changed_speed_recovery和directed_speed_change 变量设置为0b。

如果N_FTS发生变化,则新的N_FTS用于之后的LOs状态。

当使用8b/10b编码,Lane-to-Lane de-skew必须在退出Recovery.RcvrCfg时完成。

设备必须记录在发生此状态转换时在任意Lane上发送的八个连续的TS2有序集中通告的Data Rate Identifiers值。这个值可能会覆盖之前记录的值。

当使用128b/130b编码且八个连续的TS2有序集中的Request Equalization 字段为1b,则设备必须要记录此值并按Section 4.2.3的规则来处理。

如果在任意Lane上收到了八个连续的TS1有序集中的Link number与Lane number与在该Lane上发送的不一致,并且在收到一个TS1有序集之后发送完16个TS2有序集,并且下述任一条件满足,则状态机跳转到Configuration状态:

收到的八个连续的TS1有序集的speed_change字段为0b。

当前数据速率为2.5GT/s,并且没有在接收到的八个连续TS1有序集中设置5.0 GT/s或更高的Data Rate Identifier,或者没有在发送的TS2有序集中设置5.0 GT/s或更高的Data Rate Identifier。

如果N_FTS发生变化,则新的N_FTS用于之后的LOs状态。

在状态机切换到Configuration时changed_speed_recovery和directed_speed_change变量设置为0b。

如果从LO或L1进入Recovery以来,工作速率没有变化到相互协商的速率上(changed_speed_recovery=0b),并且现在的工作速率大于2.5GT/s,并且检测到一个EIOS或者在任意已配置的Lane上推导/检测到电气空闲条件,并且在进入此子状态后在未配置的Lane上收到一个TS2有序集,则下个状态转换到Recovery.Speed。退出Recovery.Speed后的工作速率将会是2.5GT/s。

如Section 4.2.4.3所述,如果在Table 4-11中指定的时间间隔内未收到TS1或TS2有序集,则可以推断出电气空闲状态。

如果从LO或L1进入Recovery以来,工作速率已经变化到相互协商的速率上(changed_speed_recovery=1b),并且检测到一个EIOS或者在任意已配置的Lane上推导/检测到电气空闲条件,并且在进入此子状态后在未配置的Lane上收到一个TS2有序集,则下个状态转换到Recovery.Speed。退出 Recovery.Speed后的工作速率将会恢复到从LO或L1进入Recovery时的速率。

如Section 4.2.4.3所述,如果在Table 4-11中指定的时间间隔内未收到TS1或TS2有序集,则可以推断出电气空闲状态。

这种切换意味着另一端无法以其运行的速度实现符号锁定或块对齐。因此,双方将恢复到2.5GT/s的运行速度,并且两个设备都不会在不退出Recovery状态的情况下再次尝试更改速度(意思是如果还需要尝试更改速度,则必须退出Recovery状态)。还应注意,即使此处涉及速度更改,但changed_speed_recovery 依然为0b。

在48ms超时后会执行以下操作:

如果当前速率为2.5GT/s或者5GT/s,则下个状态跳转到Detect状态。

如果idle_to_rlock_transitioned<FFh且当前工作速率为8GT/s,则下个状态跳转到Recovery.ldle。

在在进入Recovery.Idle时,changed_speed_recovery和directed_speed_change变量都重置为0b。

否则下个状态跳转到Detect状态。

4.2.6.4.5 Recovery.Idle

在直接定向作用下下个状态跳转到Disabled状态。

Note:“直接定向”的意思是Downstream Port或crosslink Port 在上层逻辑中把发送的TS1或TS2有序集中的Disable Link 字段置为1b。

在直接定向作用下下个状态跳转到Hot Reset状态。

Note:“直接定向”的意思是Downstream Port 或 crosslink Port 在上层逻辑中把发送的TS1或TS2有序集中的Hot Reset 字段置为1b。

在直接定向作用下下个状态跳转到Configuration状态。

Note:“直接定向”的意思是Port在上层逻辑中进行重新配置链路。

在直接定向作用下下个状态跳转到Loopback状态,此时发送器作为一个loopback master,这个根特定实现有关。

Note:“直接定向”的意思是Port在上层逻辑中把发送的TS1或TS2有序集中的Loopback字段置为1b。

如果在任意已配置的Lane上收到两个连续的Disable Link字段为1b的TS1有序集,则下个状态跳转到Disabled状态。

Note:这个行为仅应用于Upstream Port和crosslink Port。

如果在任意已配置的Lane上收到两个连续的Hot Reset字段为1b的TS1有序集,则下个状态跳转到Hot Reset状态。

Note:这个行为仅应用于Upstream Port和 crosslink Port。

如果在任意已配置的Lane上收到两个连续的Lane number字段为PAD的TS1有序集,则下个状态跳转到Configuration 状态。

Note:确保实现转换到Configuration以更改链路配置功能的端口在所有通道上发送Lane number设置为PAD的TS1有序集。

Note:建议LTSSM使用此转换来增大/缩小链接宽度,以减少更改链接宽度所需的时间。

如果在任意已配置的Lane上收到两个连续的Loopback字段为1b的TS1有序集,则下个状态跳转到Loopback状态。

Note:收到Loopback字段为1b的TS1有序集的设备作为loopback slave。

当使用8b/10b编码,则发送器在所有已配置的Lane上发送Idle data。当使用128b/130b编码,则发送器在所有已配置的Lane上发送SDS有序集以开始一个数据流,然后发送Idle data Symbols。Note:在Lane 0上发送的第一个 Idle data Symbol 为数据流的第一个Symbol。

如果定向到其他状态,则在转换到其他状态之前不用发送Idle Symbol,也不用发送128b/130b编码(Disabled,Hot Reset,Configuration, or Loopback)。

IMPLEMENTATION NOTE

EDS Usage

当使用128b/130b编码,在Configuration或Loopback或Hot Reset或Disabled状态时,如果数据流处于有效状态(即已发送SDS 有序集),则必须发送EDS。未启动Link Upconfigure的一方在收到TS1有序集时可能已经发送了SDS和数据流(Logical IDL)。在这种情况下,它将在发送配置中的TS1有序集之前在有效的通道集中发送EDS。

当使用8b/10b编码,如果在所有已配置的Lane上收到8个连续的Symbol Times的Idle data并且在收到一个 Idle data Symbol 后发完16个Idle data Symbol,则状态机跳转到LO。

如果在最后一次从Recovery或Configuration 状态转换到LO之前软件把Link Control 寄存器的 Retrain Link 字段写1b,Downstream Port 就必须把Link Status 寄存器的Link Bandwidth Management Status字段置为1b。

当使用128b/130b编码,如果在所有已配置的Lane上收到8个连续的Symbol Times的Idle data并且在收到一个Idle data Symbol后发完16个Idle data Symbol,并且此子状态不是从Recovery.RcvrCfg切换过来的,则状态机跳转到LO。

Idle data Symbol 必须在Data Block中接收。

Lane-to-Lane de-skew 必须在数据流处理开始之前完成。

如果在最后一次从Recovery或Configuration 状态转换到LO之前软件把Link Control 寄存器的 Retrain Link字段写1b,Downstream Port 就必须把 Link Status 寄存器的 Link Bandwidth Management Status 字段置为1b。

在转换到LO状态时idle_to_rlock_transitioned 变量要置为00h。

否则,在2ms超时后执行下述操作:

如果idle_to_rlock_transitioned<FFh,则下个状态为Recovery.RcvrLock。

如果 data rate是8.0GT/s,则每次转换到Recovery.RcvrLock,idle_to_rlock_transitioned变量递增1。

如果 data rate是5.0GT/s(或,如果支持2.5GT/s),则在转换到Recovery.RcvrLock 时 idle_to_rlock_transitioned 变量设置为 FFh0

否则,下个状态为 Detect0。

4.2.6.5 L0

LO状态是正常的数据传输状态。

LinkUp=1b0

在接收STP和SDP时,idle_to_rlock_transitioned要复位为00h。

如果下述两个条件其中一个满足,状态机就跳转到Recovery状态:1)当两侧设备都支持比2.5GT/s更高的 data rate 且链路处于DL_Active时,上层逻辑会直接发起链路速率切换(directedpeedhange=1b) ;2)当两侧设备都支持8GT/s且链路要执行一个8GT/s的均衡过程时,上层逻辑会直接发起链路速率切换(directedpeedhange=1b)。然后还要把changed_speed_recovery 复位成0b。

对于Upstream Port,如果Downstream Port 从来没有在Configuration.Complete或Recovery.RcvrCfg 状态通告比2.5GT/s 更高的数据速率,directed_speed_change就不能设置为1b。

对于Downstream Port,如果 Upstream Port从来没有在Configuration.Complete或Recovery.RcvrCfg状态通告比2.5GT/s 更高的数据速率,directed_speed_change就不能设置为1b。如果支持比2.5GT/s更高的数据速率,则如果Link Control 寄存器的Retrain Link字段设置为1b,并且Link Control 2 寄存器中的Target Link Speed字段不等于当前的链路速度,则Downstream Port 必须将directed_speed_change变量设置为1b。

即使链路不处于DL_Active状态,如果对端通过TS1发出请求,支持比2.5GT/s更高的数据速率的Port 也必须参与链路速率切换过程。

如果要发生链路宽度变化,则状态机会跳转到Recovery状态。

如果对端端口在Configuration状态没有通告链路宽度的upconfigure能力,或者链路在进入L0时已经是最大宽度的链路,上层逻辑就不能发出增加链路宽度的操作。

正常情况下,出于可靠性原因,如果将upconfigure_capable 重置为0b,则上层逻辑不会减小链路宽度,因为如果upconfigure_capable 为0b,则链路将无法返回到最初的宽度。如果将Link Control寄存器中的 Hardware Autonomous Width Disable 字段设置为1b,则端口不得出于可靠性以外的其他原因启动减小链路宽度的操作。

减少或增加链路宽度是跟具体实现有关的问题。

如果在此状态下收到了一个TS1或TS2有序集,或在128b/130b编码时收到了一个EIEOS,则状态机会跳转到Recovery状态。

状态机可以在此状态下直接定向到Recovery状态。如果在没有接收到EIOS的Lane上检测到了电气空闲,则端口有可能转换到Recovery状态,也有可能停留在LO状态。这种没有接收到EIOS的Lane上检测到了电气空闲的情况可能会导致error,所以Port可能会直接切换到Recovery状态。

如Section 4.2.4.3所述,可以在以下任一条件下推断所有通道的电气空闲条件:(i)在任何128μs窗口中均不存在Flow Control Update DLLP,(ii)在任何 128μs窗口中的任何已配置通道中不存在SKP有序集,或者(iii)在任何 128μs 窗口中的任何已配置通道中不存在Flow Control Update DLLP或SKP有序集。

这里的“直接定向”的意思是上层逻辑直接导致状态机进入Recovery状态,包括把Link Control 寄存器的 Retrain Link 字段设置为1b这种方式。

发送器可以在此状态下发送TLP和DLLP。

如果发送器实现了LOs功能,则发送器可以直接转移到LOs状态,(注意只是发送器进入LOs)。参阅Section 4.2.6.2.2。

Note:这里的“直接”指的是上层逻辑直接导致状态机进入LOs状态,参阅Section 4.2.6.6.2。

Note:有一个点需要注意:就是在此情况下TX和RX可能处于不同的LTSSM状态(如Tx处于LOs,而Rx处于L0)。

如果接收器实现了LOs功能,那么在任意Lane上收到了EIOS,则接收器直接转移到LOs状态,(注意只是接收器进入LOs)。参阅 Section 4.2.6.2.1。

Note:有一个点需要注意:就是在此情况下TX和RX可能处于不同的LTSSM状态(如Tx处于LOs,而Rx处于L0)。

如果接收器没有实现LOs,则当在任意Lane上接收到EIOS时状态机就转换到Recovery状态,且Port不能直接定向到L1和L2状态,参阅Section 4.2.6.6.1。

下列条件满足,状态机就转换到L1状态。

上层逻辑发出直接定向,且在任意Lane收到一个EIOS,并且在2.5GT/s和8GT/s速率下在所有Lane上发送一个EIOS 或在5GT/s速率下在所有Lane上发送两个连续的EIOS,状态机就跳入L1。

Note:上述的“直接”指的是在两端都接收和发送了EIOS之后都同意立即进入L1状态。PCI-PM(see Section 5.3.2.1)或ASPM(see Section 5.4.1.2.1)方式可以导致链路进入L1。

Note:当由上层逻辑指示时,链路的一侧会一致在所有通道上发送EIOS来启动进入L1的过程,然后进入电气空闲注1。然后该端口会等待在任意Lane上收到一个EIOS,之后状态机立即转换到L1。相反的,在任意Lane上首先收到EIOS 的一侧必须在所有Lane上发送EIOS并且立即转化到L1。

下列条件之一满足,状态机就转换到L2状态。

上层逻辑发出直接定向,且在任意Lane收到一个EIOS,并且在2.5GT/s和8GT/s速率下在所有Lane上发送一个EIOS 或在5GT/s速率下在所有Lane上发送两个连续的EIOS,状态机就跳入L2。

Note:上述的“直接”指的是在两端都接收和发送了EIOS之后都同意立即进入L2状态。Section 5.3.2.3给出了更多解释。

Note:当由上层逻辑指示时,链路的一侧会一致在所有通道上发送EIOS来启动进入L2的过程,然后进入电气空闲注2。然后该端口会等待在任意Lane上收到一个EIOS,之后状态机立即转换到L2。相反的,在任意Lane上首先收到EIOS 的一侧必须在所有Lane上发送EIOS并且立即转化到L2。

注1:被驱动的共模电压必须满足LO期间直流共模电压的绝对增量(VTx-CM-DC-ACTIVE-IDLE-DELTA)和电气空闲状态的规范(请参见 Table 4-18)。

注2:被驱动的共模电压不用满足LO期间直流共模电压的绝对增量(VTx-CM-DC-ACTIVE-IDLE-DELTA)和电气空闲状态的规范(请参见 Table 4-18)。

4.2.6.6 L0s

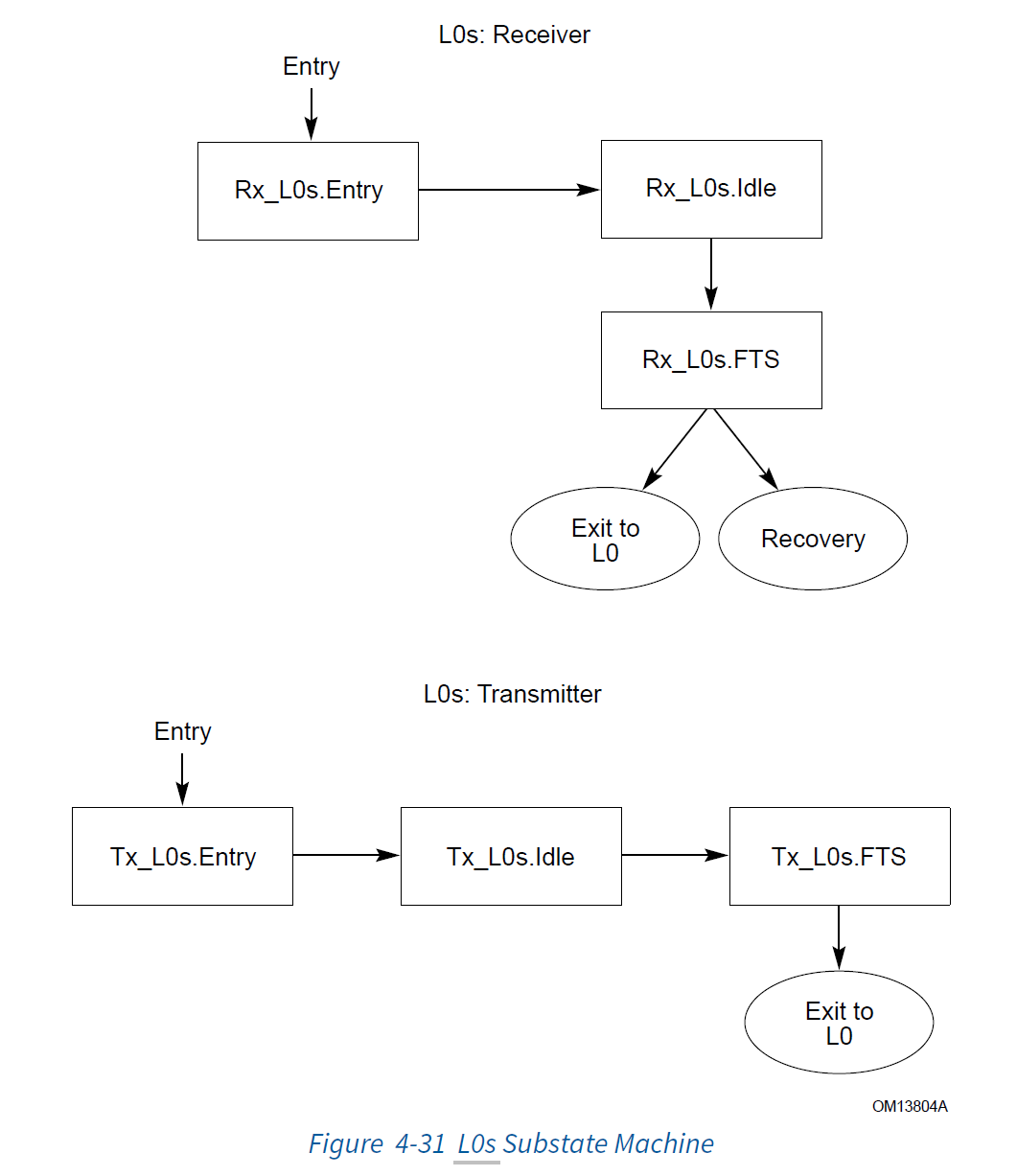

L0s子状态如 Figure 4-27所示。

4.2.6.6.1 Receiver L0s

如果接收器的Port通告对L0s的支持,则接收器必须实现L0s,Link Capability 寄存器中的ASPM Support字段用于指示对该功能的支持。即使接收器的Port不通告对LOs的支持,也允许该接收器实现 L0s

4.2.6.6.1.1 Rx_L0s.Entry

TTX-IDLE-MIN (这个值在Table4-18中定义)超时后进入Rx_L0s.Idle状态。

Note:这是发送器进入电气空闲的最小时间。

4.2.6.6.1.2 Rx_LOs.ldle

如果接收器在任意已配置的Lane上检测到电气空闲退出,则状态机转换到Rx_LOs.FTS状态。

4.2.6.6.1.3 Rx_LOs.FTS

如果在链路的所有已配置的Lane上收到8b/10b编码的SKP有序集或者128b/130b编码的SDS有序集,则状态机会跳转到L0s

接收器必须在接收到8b/10b编码的SKP有序集后能立即接收有效数据。

接收器必须在接收到128b/130b编码的SSDS有序集后能立即接收有效数据。

在离开Rx_L0s.FTS状态时必须完成Lane-to-Lane de-skew。

否则,在N_FTS超时后进入Recovery状态。

当使用8b/10b 编码:N_FTS 超时不得小于40 * [N_FTS + 3] * UI(3 * 40 UI 是从六个符号推导而来,以覆盖最大的SKP有序集+四个符号(可能有额外的FTS)+ 2 个符号的设计余量),且不得超过此数字的两倍。设置Extended Synch 字段后,接收器N_FTS 超时必须调整为不小于40 * [2048] * UI(2048 个FTS),并且不大于40 * [4096] * UI(4096 个FTS)。在规范定义的范围内选择合适的超时值时,实现时必须考虑最坏情况的Lane to Lane skew,设计裕度以及四到八个连续的EIE 符号(速度不超过2.5 GT/s)。

当使用128b/130b 编码:N_FTS 超时不得小于130 * [N_FTS + 5 + 12 + Floor(N_FTS/32)] * UI,并且不得大于此数量的两倍。5 + Floor(N_FTS/32)表示了第一个EIEOS,最后一个EIEOS,SDS,周期性的EIEOS 和一个附加EIEOS 的情况,以防实现方式选择发送两个EIEOS,然后在N_FTS 被32 整除时发送一个SDS。如果设置了Extended Synch 字段,则此处将考虑发送12 个SKP 有序集的数量。当Extended Synch 字段被置位时,超时应与N_FTS 等于4096 的正常情况相同。

发送器也必须转移到Recovery状态,但是允许它完成TLP和DLLP的整个过程。

建议在过渡到Recovery时增加N_FTS字段的值,以保证将来从Rx_L0s.FTS过渡到Recovery。

4.2.6.6.2 Transmitter L0s

如果发送器的Port通告对L0s的支持,则接收器必须实现L0s,Link Capability 寄存器中的ASPM Support字段用于指示对该功能的支持。即使接收器的Port不通告对LOs的支持,也允许该接收器实现 L0s

4.2.6.6.2.1 Tx_L0s.Entry

如果当前数据速率为2.5 GT/s或8.0 GT/s,则发送器发送一个EIOS;如果当前数据速率为5.0GT/s,则发送两个连续的EIOS;然后进入电空闲状态。

DC共模电压的值要符合规范定义的TTX-IDLE-SET-TO-IDLE的值。

Note:被驱动的共模电压必须满足LO期间DC共模电压和电气空闲之间的绝对增量(VTx-CM-DC-ACTIVE-IDLE-DELTA)的规范(请参见Table 4-18)。

TTX-IDLE-MIN (这个值在Table4-18中定义)超时后进入 TxOs.Idle 状态。

4.2.6.6.2.2 Tx_LOs.ldle

在直接定向作用下,下个状态为TxLOs.FTS

IMPLEMENTATION NOTE

Increase of N_FTS Due to Timeout in Rx_L0s.FTS

发送器通过在Tx_L0s.FTS子状态发送N_FTS个快速训练序列,使接收器能够重新获取比特锁定、符号锁定或块对齐。在没有NT 快速训练序列的情况下,接收器将在Rx_L0s.FTS子状态中超时,并且可能会增加在Recovery状态下通告的N_FTS的值。

4.2.6.6.2.3 Tx_L0s.FTS

发送器在所有已配置的通道上发送N_FTS个快速训练序列(Fast Training Sequences,FTS)。

在5.0GT/s的数据速率下,在发送NTS个(4096 if Extended SSync=1) FTS之前必须发送四到八个EIE Symbol。在128b/130b编码下,在发送N_FTS个(4096 if Extended:Sync=1)FTS之前必须发送一个EIEOS。在2.5GT/s的数据速率下,在发送NTS个(4096 if Extended Sync=1)FTS之前需要发送最多一个完整的FTS。

在发送协商好的N_FTS个FTS之前,不能插入SKP有序集。

如果Extended Sync字段设置为1b,则需要发送4096个FTS。

当使用8b/10b编码,发送器在所有已配置的通道上发送一个SKP有序集。

当使用128b/130b编码,发送器在所有已配置的通道上发送一个EIEOS,然后再跟一个SDS有序集。Note:SDS有序集发送后在Lane 0上发送的第一个Symbol是数据流的第一个Symbol。

下个状态是L0。

4.2.6.7 L1

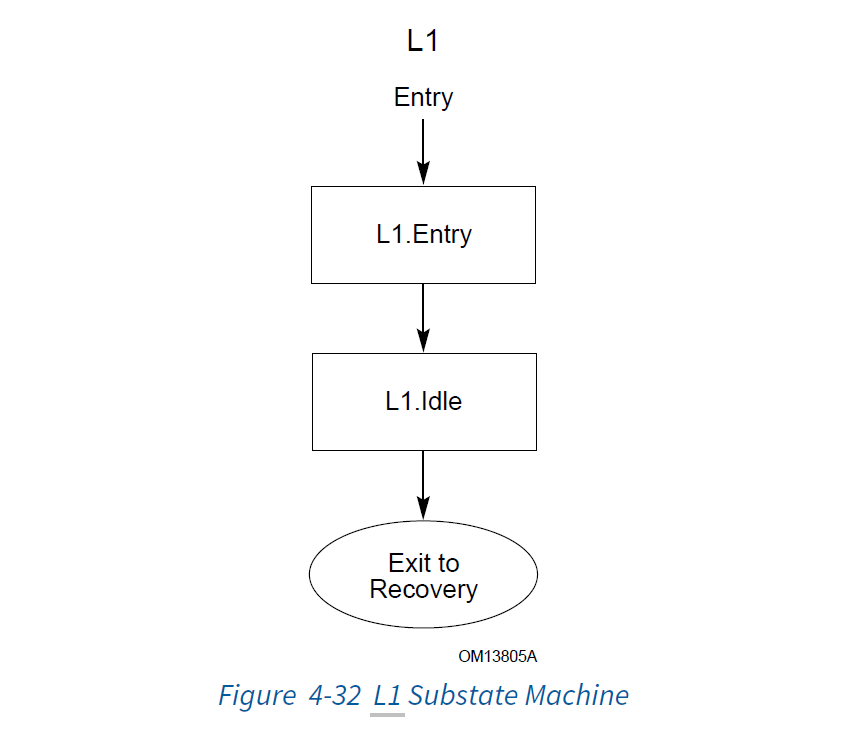

L1子状态如 Figure 4-28所示。

Figure 4-28: L1 Substate Machine

4.2.6.7.1 L1.Entry

所有已配置的发送器处于电气空闲状态。

DC共模电压比现在规范定义的TTX-IDLE-SET-TO-IDLE值的范围之内。

TTx-IDLE-MIN超时后状态进入L1.Idle子状态。TTx-IDLE-MIN在Table 4-18定义。

Note:这个时间用于保证发送器建立好电气空闲条件。

4.2.6.7.2 L1.Idle

发送器保持电气空闲状态。

DC共模电压必须在规范定义之内。

Note:被驱动的共模电压必须满足LO期间DC共模电压和电气空闲之间的绝对增量(VTx-CM-DC-ACTIVE-IDLE-DELTA)的规范(请参见Table 4-18)。

如果任何接收器检测到从电气空闲状态退出,或者除2.5GT/s速率之外在保持此子状态至少40ns之后被直接定向,则下一个状态是Recovery。

Note:在该子状态下,除了2.5GT/s以外的速度,至少需要40ns的停留时间,以解决逻辑电平上的延迟,以便在链路进入L1并立即退出L1状态时为电气空闲检测电路提供准备。

允许Port遵循LO中描述的相同规则将directed_speed_change 变量设置为1b。进行此类转换时,必须将changed_speed_recovery 变量重置为0b。Port也可以从Recovery转换回LO,然后在从LO到Recovery的转换上将directed_speed_change 变量设置为1b。

如果使用直接定向的方式更改链路宽度,则也允许Port从L1进入Recovery。Port必须遵循LO状态所述相同的规则来更改链路宽度。

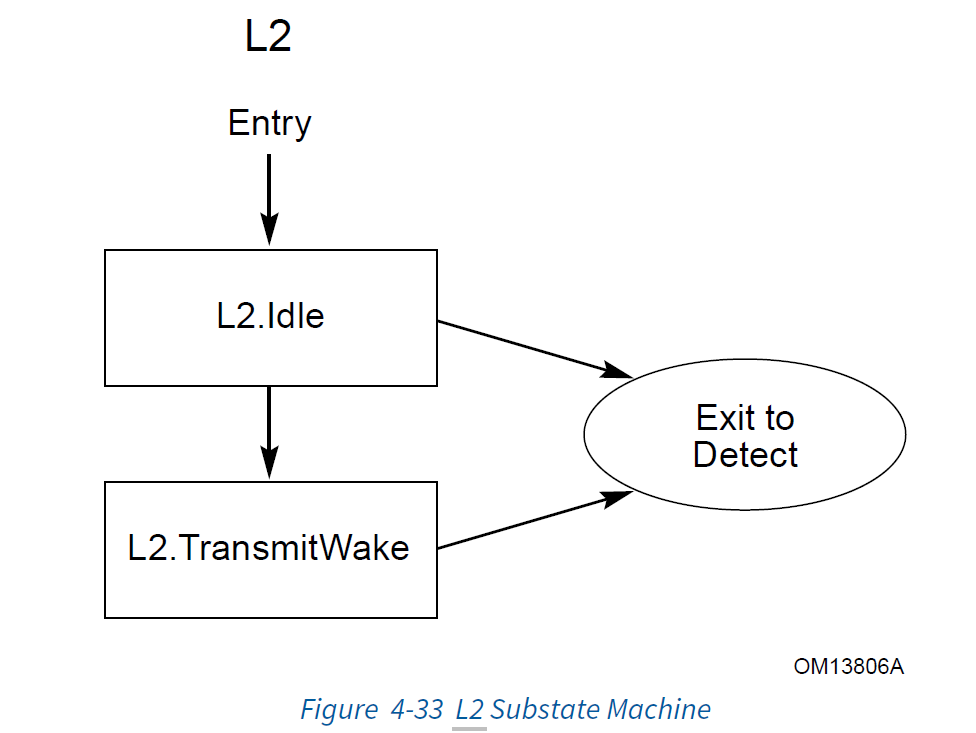

4.2.6.8 L2

L2子状态如Figure 4-29所示。

Figure 4-29: L2 Substate Machine

4.2.6.8.1 L2.Idle

所有RX的终端必须保持使能为低阻抗状态。

所有已配置的发送器必须处于电气空闲状态至少TTx-IDLE-MIN时间(Table 4-18)。

DC共模电压必须在规范定义的范围内。

接收器必须至少等待TTx-IDLE-MIN再开始查找电气空闲退出。

对于Downstream Lanes:

对于Root Port,如果至少在Lane0上检测到一个Beacon或者因直接定向作用,状态机跳转到Detect状态。

在进入Detect前主电源必须恢复。

Note:“直接定向”指的是上层逻辑决定进入Detect状态。

对于一个Switch,如果至少在Lane0上检测到一个Beacon,则Upstream Port 必须转换到L2.TransmitWake状态。

对于 Upstream Lanes:

如果在任意之前预确定过的通道组上检测到电气空闲退出,则状态机进入Detect状态。

预确定的通道组必须包括但不限于可能与链路的Lane 0进行协商的任何通道。对于多通道链路,预确定的通道数必须大于或等于2。

一个Switch可能把某些 Downstream Lanes转换到Detect状态。

对于Upstream Port,如果在直接定向作用下发送一个Beacon,则状态机转换到L2.TransmitWake状态。

Note:Beacons只能由 Upstream Port往RC方向发送。

4.2.6.8.2 L2.TransmitWake

只有Upstream Port有这个状态。

在此子状态下,至少需要在Lane0上发送Beacon。

如果任意接收器沿RC方向检测到电气空闲退出,则下个状态跳转到Detect。

Note:当上游接收器看到电气空闲已退出时,需要保证电源被恢复,但是也可以在电气空闲退出之前恢复电源。

4.2.6.9 Disabled

在此状态下,在所有Lane上发送16到32个Disable Link字段设置为1b的TS1有序集,然后进入电气空闲。

在进入电气空闲状态之前必须发送EIOS(2.5GT/s或8.0GT/s会发送一个,5.0GT/s会发送两个)。

DC共模电压不是必须要在规范定义之内。

Note:被驱动的共模电压必须满足LO期间DC共模电压和电气空闲之间的绝对增量(VTx-CM-DC-ACTIVE-IDLE-DELTA)的规范(请参见Table 4-18)。

如果在任意Lane上发送一个EIOS(2.5GT/s或8.0GT/s会发送一个,5.0GT/s会发送两个)并且接收了一个EIOS(即使正传输TS1的Disable Link置为1b),就会执行以下操作:

LinkUp = 0b

在此视角下,链路处于Disabled状态。

对于Upstream Port:如果接收器检测到电气空闲退出则下个状态切换到Detect。

对于Downstream Port:在直接定向作用下,下个状态为Detect状态(比如,软件把Link Disable 设置为0b)。

对于Upstream Port:如果2ms超时后没收到EIOS,则下个状态为Detect。

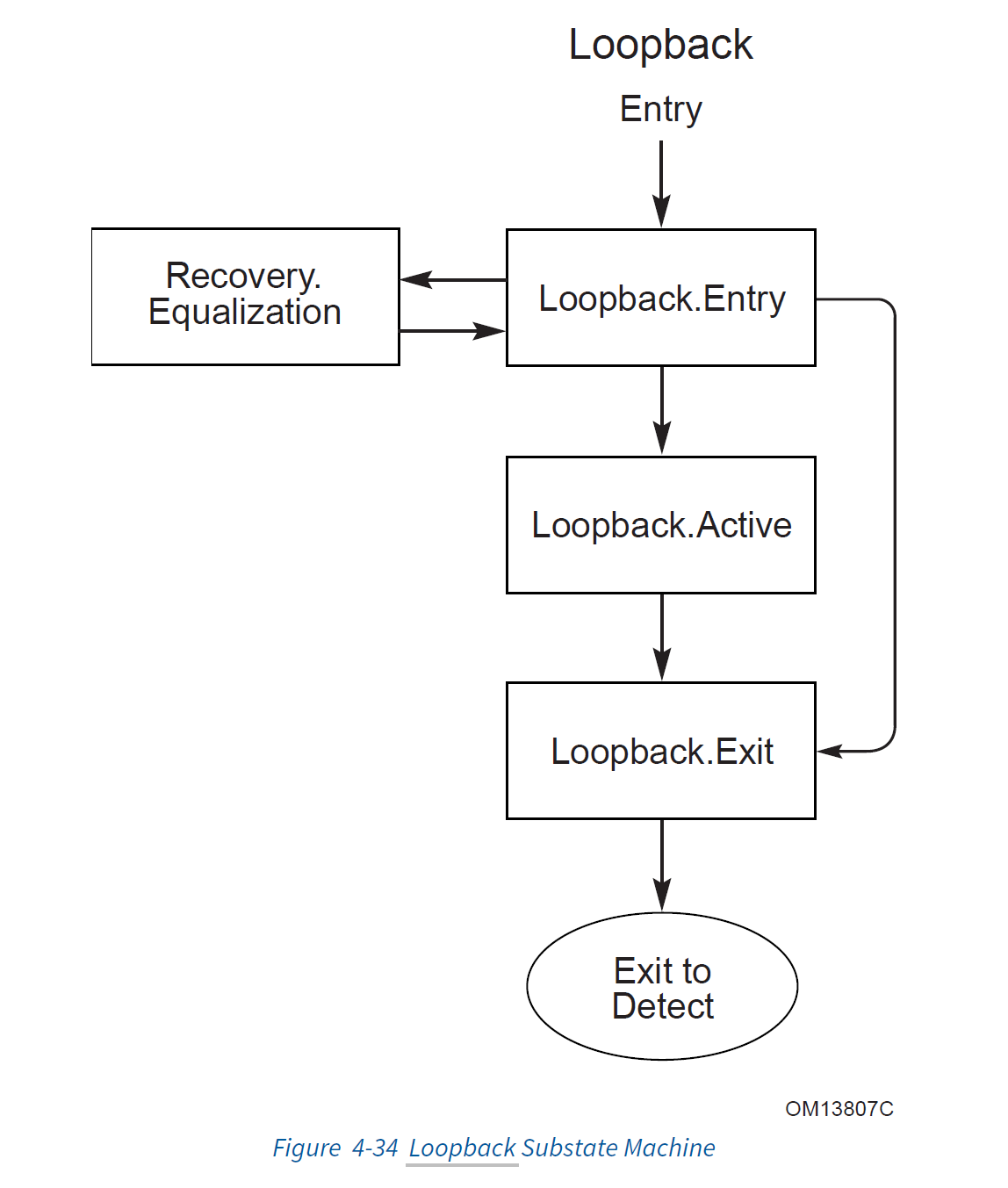

4.2.6.10 Loopback

Loopback 子状态机如 Figure 4-30。

Figure 4-30: Loopback Substate Machine

4.2.6.10.1 Loopback.Entry

LinkUp=0b

在此子状态下,接收器将忽略接收的的TS1或TS2有序集中的Link number和Lane number字段的值。

Loopback master要求:

如果从Configuration.Linkwidth.Start进入Loopback.Entry,需要确定 master与在切换到Loopback.Entry时在任意有效的Lane 上收到的两个连续TS1或TS2有序集中的数据速率的最高公共数据速率。如果当前数据速率不是最高的公共数据速率:

发送16个Loopback字段置为1b的TS1有序集,然后在2.5GT/s或8GT/s速率下再发送一个EIOS,在5.0GT/s下再发送两个EIOS,然后转换到电气空闲并停留1ms。在这段电气空闲期间内将速率切换到最高的公共速率上。

如果最高公共速率是5.0GT/s,则slave的发送器的de-emphasis 由发送的TS1有序集中的 Selectable De-emphasis 字段控制(1b=-3.5dB,0b=-6dB)。

对于5.0GT/s和以上速率,允许发送器实现自己的发送器参数设置,而忽略它发送给slave的发送器参数设置。

Note:如果在LinkUp设置为1b之后进入Loopback状态,则一个Port可以从Recovery进入Loopback状态,另一个Port可以从Configuration 进入Loopback状态。从Configuration 进入Loopback状态的Port可以尝试改变数据速率而另一个不能。如果此场景发生,则结果是未定义的。测试最好避免这种场景。

发送Loopback字段置为1b的TS1有序集。

还允许 master在Loopback.Entry中发送 Compliance Receive 字段置为1b的TS1有序集,包括在数据速率变化之前发送的那些内容。如果它把Compliance Receive字段置为1b,则在处于Loopback.Entry状态时不得再次将其置为 Obo 当一个或两侧端口在数据速率更改后难以获得比特锁定、符号锁定或块对齐时,此使用模型在测试和验证场景非常有用。设置Compliance Receive 字段的能力是特定于实现的。

如果发送的TS1有序集中的Compliance Receive 字段被置为1b,则在2ms超时后状态切换到Loopback.Active。

如果发送的TS1有序集中的Compliance Receive 字段被置为1b,并且与实现相关的一组Lane上收到了两个连续的Loopback字段置为1b的TS1有序集,则下个状态切换到Loopback.Active。

如果更改了数据速率,则master必须考虑slave 可能处于电空闲状态的时间,并发送足够数量的TS1有序集,以便slave 在进行Loopback.Active之前获取符号锁定或块对齐。

IMPLEMENTATION NOTE

Lane Numbering with 128b/130b Encoding in Loopback

如果当前数据速率使用128b/130b编码并且尚未协商好通道编号,则master和slave 可能无法解码接收到的信息,因为它们的通道使用不同的加扰LFSR种子值(因为LFSR种子值由Lane number确定)。这种场景可以通过以下方式避免:允许master和slave 在将master定向至Loopback之前完成通道编号协商,然后指示master在Loopback.Entry期间把Compliance Receive字段被置为1b,或使用其他方法来确保LFSR种子值匹配。

如果一个小于100ms的与实现相关的超时发生,则下个状态跳转到Loopback Exit0 Loopback slave要求:

如果从Configuration.Linkwidth.Start进入Loopback.Entry,需要确定slave与在切换到Loopback.Entry时在任意有效的Lane 上收到的两个连续TS1或TS2有序集中的数据速率的最高公共数据速率。如果当前数据速率不是最高的公共数据速率:

则如果当前速率是2.5GT/s或8GT/s则需要发送一个EIOS,如果当前速率为5.0GT/s则需要发送两个EIOS,然后转换到电气空闲并停留2ms。在电气空闲期间,速率切换到最高公共数据速率上。

如果最高公共速率是5.0GT/s,则将发送器的de-emphasis设置为由TS1有序集中的Selectable De-emphasis字段指定的值(1b=-3.5dB,0b=-6dB)。

如果最高公共速率是8.0GT/s而且因EQ TS1把slave定向到此子状态,则把发送器的参数设置设置为TS1有序集中携带的Preset字段指定的值。如果最高公共速率是8.0GT/s而且因标准TS1把slave定向到此子状态,slave就使用其默认的发送器参数设置值。

如果因TS1有序集中的Compliance Receive字段置为1b导致进入此子状态,则下个状态为Loopback.Active。

slave的发送器无需切换为在任何边界上发送环回数据,并且可以截断任何正在进行的有序集。

否则,slave的发送器发送Link number和 Lane number 设置为PAD的TS1有序集。

如果数据速率为2.5GT/s或5.0GT/s且完成符号锁定,则下个状态是Loopback.Active。

如果数据速率为8.0GT/s且在所有有效Lane上收到两个连续的TS1有序集,则下个状态是Loopback.Active。如果EC字段值适用于slave的Port(10b或11b)且请求的设置是一个preset或一组有效的coefficient,则由接收到的TS1有序集指定的均衡参数设置就必须做评估并应用于发送器(Note:这个过程等同于Recovery.Equalization 状态的行为)。slave 可选择实现两者(指EC为10b和11b)的值都接收。如果应用了该设置,则它们必须在接收到的500ns内生效,并且不得使发送器违反任何电气规范超过1ns。与Recovery.Equalization不同,新设置不会反映在slave发送的TS1有序集中。

当使用8b/10b编码,slave的发送器必须切换为在一个符号边界上发送环回数据,但是它允许截断任何正在传输的有序集。当使用128b/130b编码,slave的发送器没必要在任何边界上发送环回数据,并且它允许截断任何正在传输的有序集。

4.2.6.10.2 Loopback.Active

在此子状态下,发送器必须发送有效的编码数据。Loopback master在退出Loopback之前应该避免将EIOS当做数据发送。

在继续执行时钟容限补偿的同时,需要回送slave重新发送接收到的已编码信息,并需要应用Polling阶段确定的极性反转:

必须按照Section 4.2.7中的概述,在每个通道上添加或删除SKP,不同之处在于不必跨已配置链路的通道同时添加或删除SKP。

对于8b/10b编码,如果重发的SKP有序集需要添加一个SKP Symbol 以适应时序容限矫正,需要在COM Symbol 后的SKP有序集中与SKP Symbol 相邻的重传符号流的任意位置插入该SKP Symbol。插入的SKP符号必须与SKP 有序集中收到的SKP符号具有相同的差异。

对于8b/10b编码,如果重发的SKP有序集需要减少一个SKP Symbol以适应时序容限矫正,该SKP Symbol只需要简单的不进行重传就行。

对于128b/130b编码,如果重发的SKP有序集需要添加SKP Symbol以适应时序容限矫正,需要在有序集的SKP_END Symbol前的重传符号流中插入四个SKP Symbol。

对于128b/130b编码,如果重发的SKP有序集需要减少SKP Symbol以适应时序容限矫正,则SKP有序集中SKP_END Symbol前的四个 SKP Symbol只需简单的不进行重传就行。

即使它被确定为无效编码(即,对于8b/10b编码无法转换为合法的K或D字符;对于128b/130b编码无法转换为合法的Sync Header或有效的有序集),Loopback slave也不允许修改接收到的编码数据(Polling中确定的极性反转情况除外)。

如果下述之一条件满足则状态机跳转到Loopback.Exit:

如果直接定向或在任何通道上收到四个连续的EIOS。必须注意的是,在8b/10b编码中,接收到四个连续的EIOS表示该通道接收到四组连续的COM、IDL、IDL、IDL,或者四个EIOS中IDL符号占IDL总数的三分之二。在128b/130b编码中,接收四个连续的EIOS表示在最后一个EIOS中的01b同步头之后的前三个和前四个符号中接收完整的130位EIOS。

可选地,如果当前链路速度为2.5GT/s,并且在任何通道上都接收到EIOS或检测/推断出电气空闲。

Loopback slave 必须能够在Loopback slave接收到EIOS的1ms内检测到任何通道上的电气空闲状况。

Note:在接收到EIOS之后且在Loopback slave 实际检测到电气空闲之前的时间内,Loopback slave 可能会接收到编码方案未定义的比特流,该比特流可能会被发送器送回。

TTX-IDLE-SET-TO-IDLE参数在这种情况下不适用,因为Loopback slave 可能在EIOS之后的1ms之内无法检测到电气空闲。

在直接定向作用下下个状态跳转到Loopback.Exit。

4.2.6.10.3 Loopback.Exit

Loopback master 在仅支持2.5 GT/s数据速率的端口发送一个EIOS,并在支持大于2.5GT/s数据速率的端口发送八个连续的EIOS(可选择实现对于仅支持2.5GT/s数据速率的端口也发送八个连续EIOS),不论当前的链路速度如何,都要在所有通道上进入电气空闲状态保持2ms。

发送最后的EIOS后,Loopback master 必须在TTx-IDLE-SET-TO-IDLE内所有通道都转换为电气空闲状态。

Note:EIOS 可用于表示Loopback master 发生的传输和比较操作结束。接收到任何EIOS后,Loopback master 收到的任何数据都应忽略,因为它是未定义的。

Loopback slave 必须所有Lane进入电气空闲并保持2ms。

进入电气空闲之前,Loopback slave 必须对检测到电气空闲之前收到的所有符号进行环回。这样可以确保Loopback master 可以看到EIOS,以表示任何环回发送和比较操作的逻辑结束。

Loopback master和Loopback slave的下个状态都是Detect状态。

4.2.6.11 Hot Reset

DSP通过发送两个连续的hot reset字段为1的TS1序列来让USP进入热复位状态。

由上层逻辑引导进入Hot Reset的Lane会执行以下操作(这个多应用于Downstream Port):

在所有已配置的Lane 上发送Hot Reset字段置为1b且Link number与Lane number 为已配置好的值的TS1有序集。

如果在任意已配置的Lane上收到两个连续的Hot Reset字段置为1b的TS1有序集,则:

LinkUp=0b

如果没有上层逻辑要求保持Hot Reset,则下个状态为Detect状态。

否则,继续在所有已配置的Lane上发送Hot Reset字段置为1b且Link number与Lane number为已配置好的值的TS1有序集

否则,在2ms超时后进入Detect状态。

并非由上层逻辑引导进入Hot Reset的Lane会执行以下操作(比如在任意已配置的Lane上收到两个连续的Hot Reset字段置为1b的TS1有序集)(这个多应用于Upstream Port):

LinkUp=0b

如果一个Switch的Upstream Port的任意 Lane 收到两个连续的Hot Reset字段置为1b的TS1有序集,所有已配置的Downstream Port 必须立即切换到Hot Reset。

Switch上的crosslink是个此规则的例外,它的行为与具体实现有关。

所有已配置的Lane上要发送Hot Reset字段置为1b且 Link number与Lane number 为已配置好的值的TS1有序集。

如果收到了两个连续的Hot Reset字段置为1b且Link number与Lane number为已配置好的值的TS1有序集,将继续保持Hot Reset状态并重置2ms计时器。

否则,在2ms超时后进入Detect状态。

Note:通常,Downstream Port或 crosslink Port的通道将被直接定向到Hot Reset,而Upstream Port或crosslink Port的通道将通过接收两个连续的Hot Reset字段置为1b的TS1有序集从Recovery.ldle 状犬态进入Hot Reset。

4.2.7 Clock Tolerance Compensation

SKP Ordered Set(如 Section 4.2.7.1和 Section 4.2.7.2定义)用于补偿链路两端比特率之间的频率差异。接收器物理层逻辑子层必须实现一个执行此补偿的弹性缓存(Elastic Buffer)。SKP有序集传输之间的间隔是根据Table 8-6, Table 8-10和 Table 8-17中指定的Transmit、Receiver和Refclk规范得出的。

该规范支持共享参考时钟体系结构(common Refclk),这样Tx和Rx Refclk速率之间没有差异;规范还支持两种参考时钟体系结构,其中Tx和Rx Refclk速率不同,即Separate Reference Clocks With No SSC - SRNS 和 Separate Reference Clocks with Independent SSC - SRIS。SRNS的最大频率差异为600ppm,这可能导致每1666个Cycle偏移一次时钟。SRIS的最大差异为5600ppm,这可能导致每178个Cycle偏移一次时钟。

特定的外形规格规范要么实现SRIS时钟结构,要么实现SRNS时钟结构,或者实现可以在这两种时钟结构之间切换的机制。Upstream Port 允许实现对SRIS和SRNS的任何组合的支持(不包括对两者的任何支持),但必须符合相关的外形规格规范的要求。支持SRIS的Downstream Port 也必须支持SRNS,除非该Port仅与修改这些要求的特定外形规格相关联。满足特定外形规格要求的端口配置是特定于实现的。Section 8.6.8节提供了外形规格的具体指南。

即使Port运行于SRIS,如果接收器能够以SRNS中使用的速率生成SKP Order Set,则允许该Port把Link Capabilities 2 Register 中的Lower SKP OS Reception Supported Speeds Vector 字段设置为合适的数据速率。即使Port运行于SRIS,如果发送器能够以SRNS 中使用的速率生成SKP Order Set,则允许该Port把Link Capabilities 2 Register 中的 Lower SKP OS Reception Supported Speeds Vector 字段设置为合适的数据速率。系统软件必须先把Link Partner 的 Link Control 3 Register的 Enable Lower SKP OS Generation Vector 字段设置为适当的数据速率,然后检查Lower SKP OS Reception Supported Speeds Vector 域中的位是否已设置。链路上存在的任何软件透明的扩展设备(例如中继器)也必须支持lower SKP OS Generation,系统软件才能设置Enable Lower SKP OS Generation Vector 字段。软件如何确定此类扩展设备是否支持lower SKP OS Generation是特定于实现的。当在Enable Lower SKP OS Generation Vector 字段中设置了链路正在运行的数据速率的比特位时,无论链路正运行于哪种时钟架构,发送器都会以SRNS中使用的速率在LO 状态中调度SKP有序集的生成。在其他LTSSM状态中,SKP有序集调度工作于时钟结构的合适速率下。

与仅支持SRNS的设计相比,支持SRIS的组件的弹性缓冲区中可能需要更多的条目。如果SKP有序集在最大有效负载的数据包之后立即掉落(latter fall),则此要求考虑了调度SKP有序集可能需要的额外时间。

4.2.7.1 SKP Ordered Set for 8b/10b Encoding

当使用8b/10b编码时,传输的SKP有序集是一个COM符号,后跟三个SKP符号,但Loopback.Active 状态下的Loopback从设备除外。收到的SKP有序集是一个COM符号,后跟一到五个SKP符号。

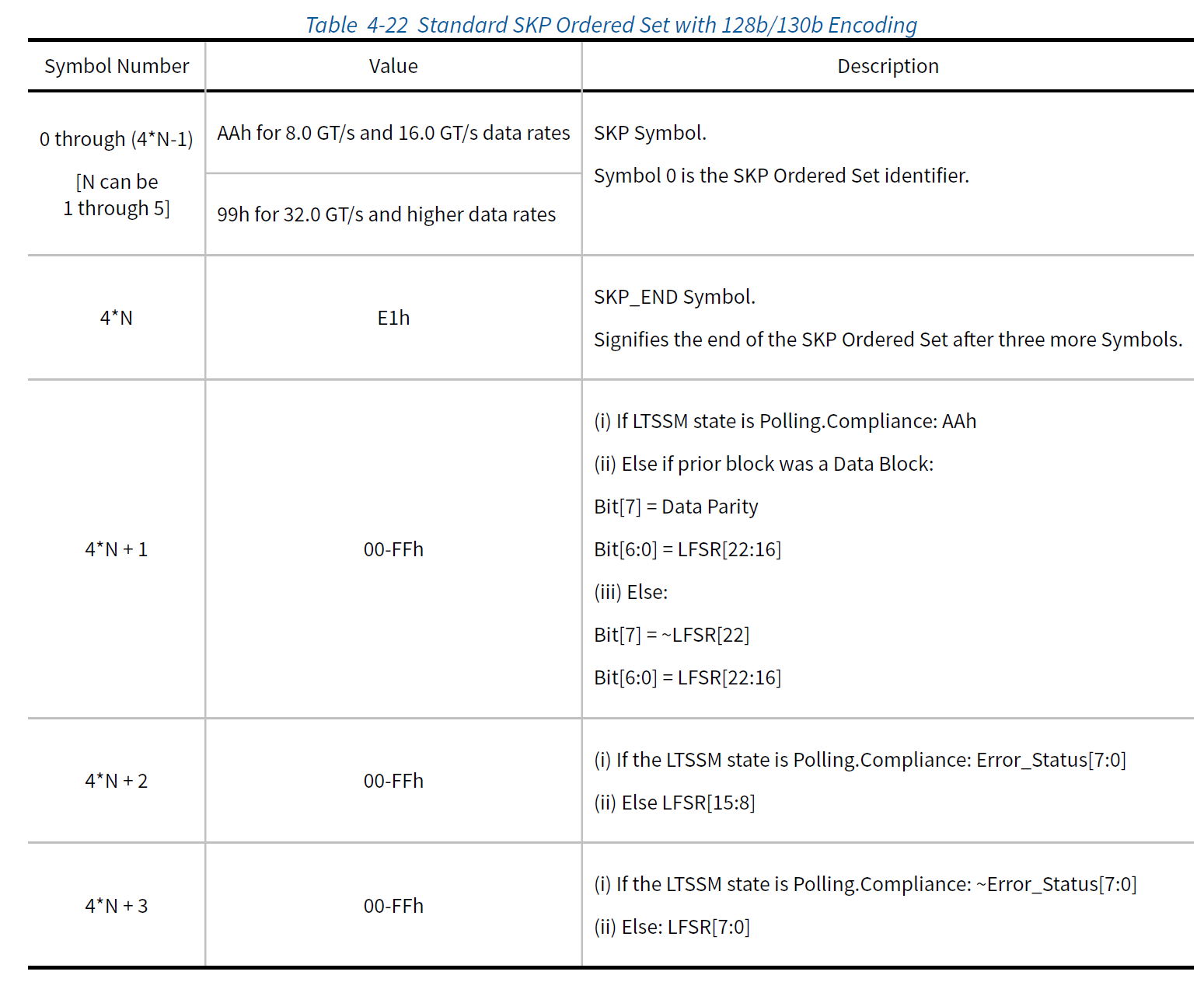

4.2.7.2 SKP Ordered Set for 128b/130b Encoding

Table 4-15给出了使用128b/130b编码时SKP有序集的布局。传输的SKP有序集为16个符号。一个端口可以添加和删除四个SKP 符号。因此,接收到的SKP有序集可以是8、12、16、20或24个符号。SKP_END符号表示SKP有序集的最后四个符号,以便接收器可以识别比特流中下一个块同步头的位置。根据LTSSM状态,SKP_END符号后面的三个符号包含不同的信息。

Table 4-15中的Data Parity字段是自最后一个SDS有序集或SKP有序集(以最近传输的那个有序集)开始加扰后传输的所有数据块的有效负载的偶校验。每个通道的Data Parity 字段是独立计算的。要求接收端使用与发送器相同的方法来计算奇偶校验,并将计算结果与接收到的Data Parity字段进行比较。如果计算出的值和接收到的值不匹配,则必须设置Lane Error Status寄存器中的对应字段,该位与检测到不匹配的默认通道号相对应。但是,这样的不匹配不是一个Receiver Error,也不能引起链路重新训练。

为Modified Compliance Pattern 定义的 Error_Status字段包含两部分信息:Pattern Lock(Error_Status [7])和 Receiver Error Count (Error_Status [6:0])。有关更多信息,请参见Section 4.2.6.2.2。

IMPLEMENTATION NOTE

关于SKP有序集中的LFSR

传输LFSR值使得跟踪工具即使在比特流中间需要重新获取块对齐时也能够运行。由于跟踪工具无法强制链路进入Recovery状态,因此如果需要的话它们可以重新获取比特锁定,并监视SKP有序集以获取Block alignment 并执行 Lane-to-Lane de-skew。可以将“SKP有序集中的LFSR值加载到其LFSR中,以开始解释比特流。必须注意的是,使用比特流时,可能会将其别名为非块边界上的SKP有序集。跟踪工具可以通过使用特定于实现的方式(例如,接收固定数量的有效数据包或同步头或后续的SKP有序集)来验证其块对齐。

4.2.7.3 Rules for Transmitters

所有通道均应以相同的频率发送符号(所有多通道链路中的比特率之差为0ppm)。

传输时,相同长度的SKP有序集应在多通道链路的所有通道上同时传输,但处于Loopback.Active 状态的Loopback Slave 允许的除外(请参见Section 4.2.4.10和Table 4-18的上下文获取同时的意义)。

按Section 4.2.7.1描述的方式传送8b/10b编码的SKP有序集。

按Section 4.2.7.2描述的方式传送128b/130b编码的SKP有序集。

当使用8b/10b编码时:一个SKP有序集的发送间隔在1180和1538个Symbol Times之间。

当使用128b/130b编码时:当LTSSM不处于Loopback 状态或处于Loopback 状态但 Loopback Slave 尚未开始环回数据,则一个SKP有序集的发送间隔在370到375个block之间。当LTSSM处于Loopback状态时,Loopback Master 必须安排两个SKP 有序集进行传输,彼此之间最多相隔两个块,间隔为370到375个块。

如果分组或有序集尚未进行,则应发送预定的SKP有序集,否则,将其累积,然后在下一个分组或有序集边界处连续插入。

注意:使用128b/130b编码时,不能在数据流中的连续块中传输SKP有序集。有关更多信息,请参见第4.2.2.3.2节。

如果packet(指有效数据包)或有序集尚未开始传输,则已经调度好的SKP有序集就可以发送,否则就将其累积,然后在下一个packet或有序集边界处连续插入。注意:使用128b/130b编码时,不能在数据流中的连续块中传输SKP有序集。有关更多信息,请参见Section 4.2.2.3.2。

检测连续的符号或有序集(例如Polling.Active中的八个连续的TS1有序集)时,插入的SKP有序集不算是中断了这种“连续”的行为。

当使用8b/10b编码时:如果 Link Control 2寄存器的Compliance SOS字段为0,则在Polling.Compliance 过程中正在发送Compliance Pattern 或 Modified Compliance Pattern(Section 4.2.8)时,不得传输SKP有序集。如果Link Control 2寄存器的Compliance SOS字段为1b,则使用8b/10b编码正在发送 Compliance Pattern 或 Modified Compliance Pattern时,必须在合适的时间间隔内发送已调度好的SKP有序集。

当使用128b/130b编码时,Compliance SOS字段不起作用。

在发送器处于电气空闲状态时所花费的所有时间都不会计入用于计划发送SKP有序集的计划时间间隔中。

建议在发送器电气空闲时随时重置用于计划SKP有序集的任何计数器或其他机制。

4.2.7.4 Rules for Receivers

接收器应在使用8b/10b编码时识别出 Section 4.2.7.1中定义的received SKP Ordered Sets,在使用128b/130b编码时识别出Section 4.2.7.2中定义的received SKP Ordered Sets。

·在多通道链路中,各通道接收到的SKP有序集的长度必须相同。这在Loopback.Active时可能例外,因为Loopback.Active 可以针对各通道单独进行。

当使用8b/10b编码时,接收器应容忍在1180到1538个Symbol Time的平均间隔内接收和处理SKP有序集,而当使用128b/130b编码时,接收器应容忍在370至375个块之间接收和处理SKP有序集。

注意:因为处于空闲状态的发送器不需要复位它的基于时间调度SKP有序集的机制,因此,接收器应有能力在小于空闲时间的SKP有序集之间的平均时间间隔内接收第一个有时间安排的SKP有序集。

对于8.0GT/s及以上的数据速率,在LO状态下,接收端必须检查每个SKP有序集前面是否有带有EDS数据包的数据块。

接收方应能以2.5 GT/s和5.0 GT/s的数据速率接收和处理连续的SKP有序集。

接收器应能容忍接收和处理最大间隔取决于组件支持的Max_Payload_Size的SKP有序集。对于2.5GT/s和5.0 GT/s的数据速率,SKP有序集之间的最大符号数(N)的公式为: N=1538+(Maxayloadizeyte+28)。例如,如果Max_Payload_Size为4096字节,则N=1538+4096+28=5662。

4.2.8 Compliance Pattern in 8b/10b Encoding

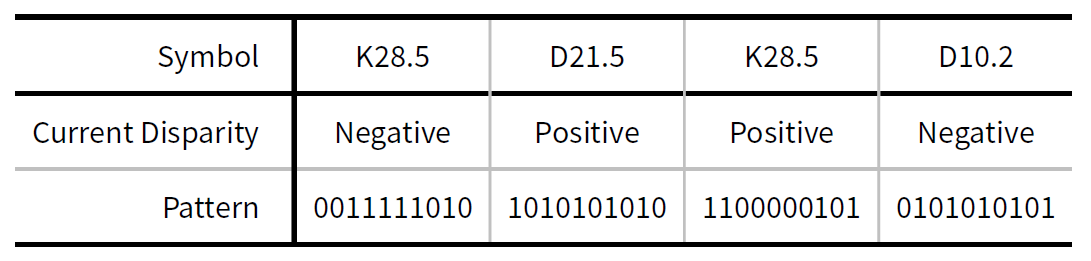

在Polling状态期间,必须根据 Section 4.2.6.2.1中所述的条件从Polling.Active转移到Polling.Compliance子状态。在8b/10b下,Compliance Pattern 由重复的K28.5,D21.5,K28.5和D10.2的符号序列组成。Compliance Pattern 序列如下:

第一个一致性序列符号必须具有负差异(negative disparity)。允许创建差异错误(disparity error),以使执行差异(running disparity)与第一个一致性序列符号的负差异对齐。

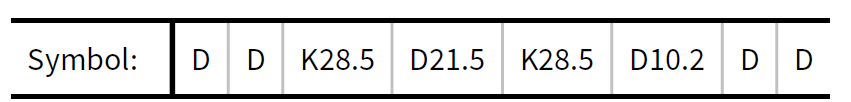

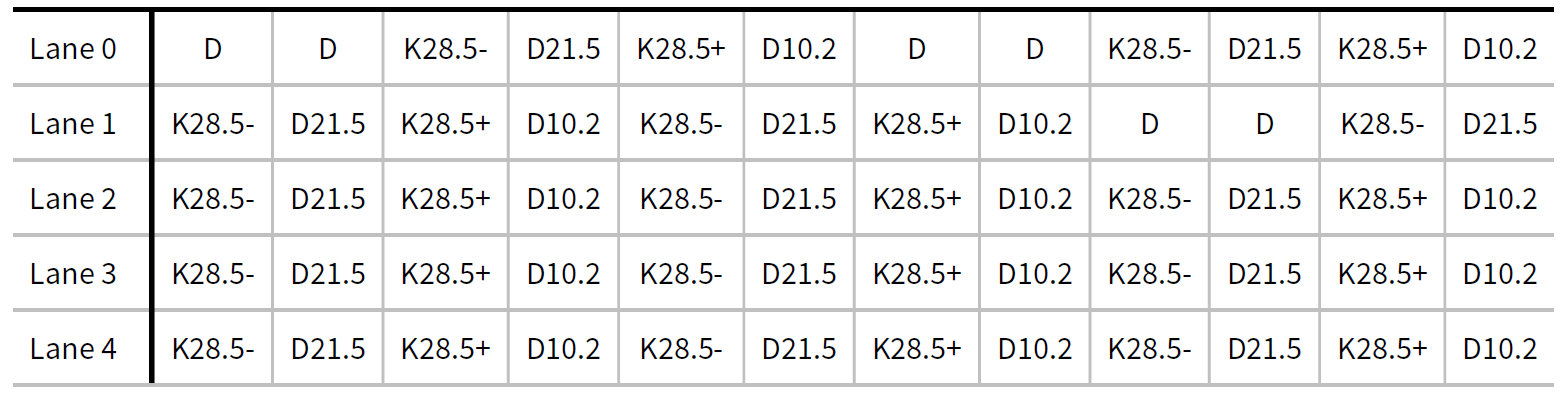

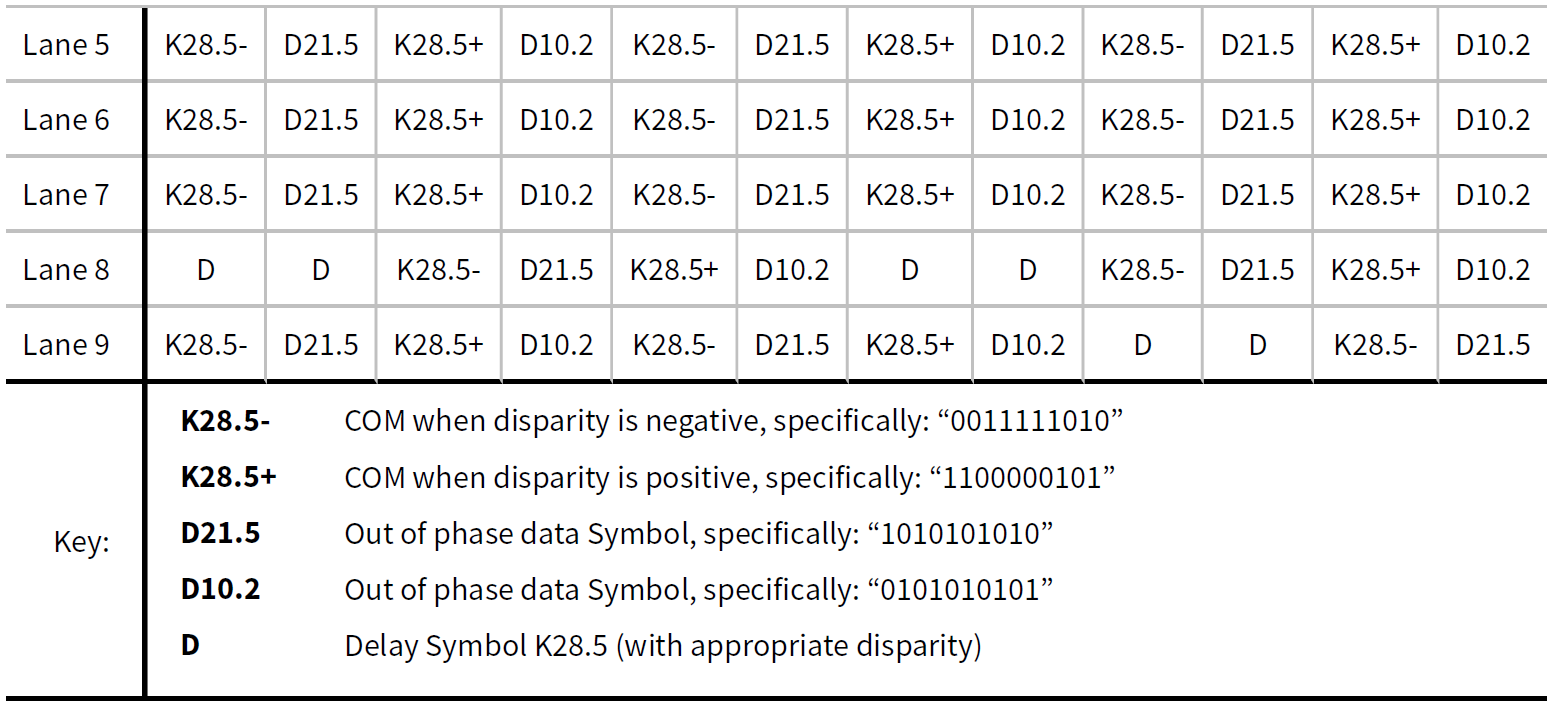

对于具有多个通道的任何给定设备,每八个通道总共延迟四个符号。在四个Symbol Compliance Pattern 序列的开始和结尾均出现两个符号延迟。x1设备或在x1模式下运行的xN设备允许在Compliance Pattern 中包含Delay Symbols。

那么,每八个通道的延迟序列为:

其中D是K28.5符号。第一个D符号具有负差异,以使延迟差异(delay disparity)与Compliance序列的差异对齐。

发送八个符号后,延迟符号将前进到下一个通道,直到在所有八个通道上都发送了延迟符号。然后,延迟符号循环回到通道0,并重复该过程。无论检测到或支持的通道数量如何,都可以在所有八个通道上提前延迟序列。下表给出了此过程的说明:

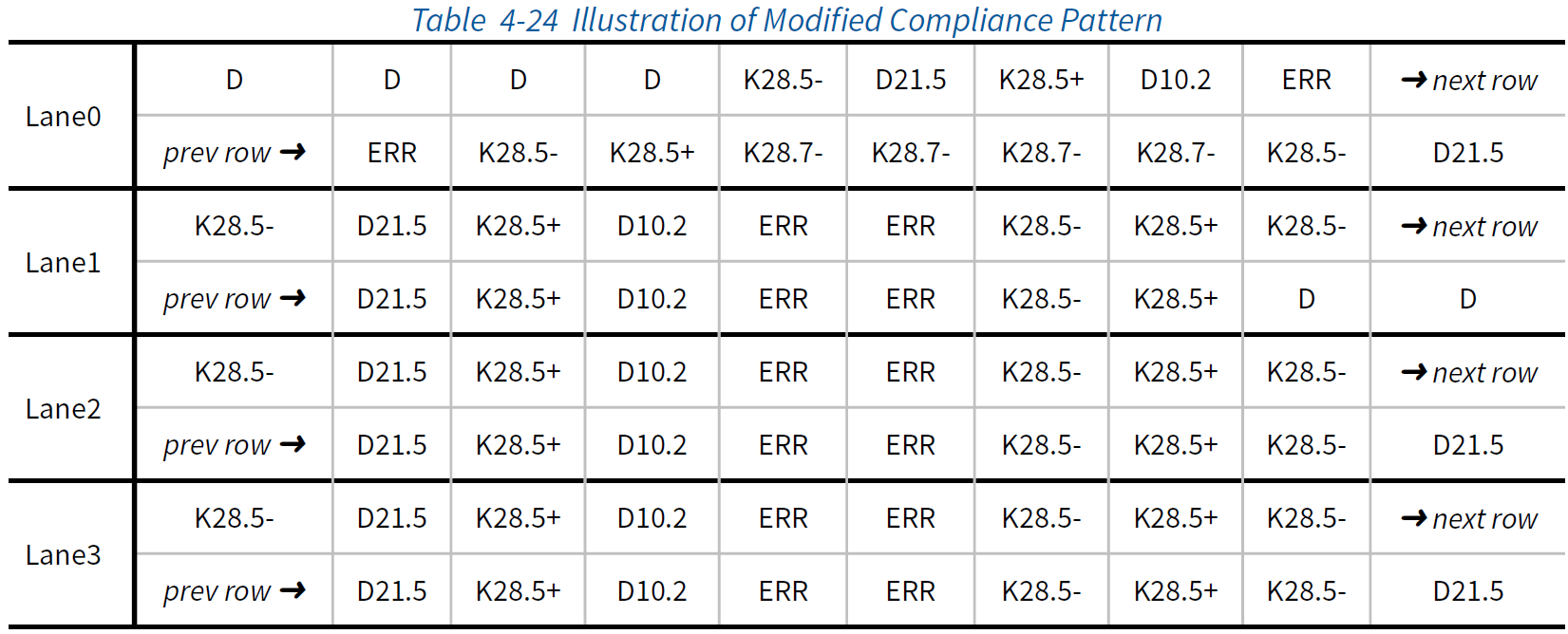

4.2.9 Modified Compliance Pattern in 8b/10b Encoding

Modified Compliance Pattern 由 basic Compliance Pattern sequence(请参阅Section 4.2.8)组成,只做了一处更改。两个相同的error status Symbol,后跟两个K28.5,被附加到8b/10b符号的basic Compliance Pattern sequence (K28.5, D21.5, K28.5和D10.2)上,以形成(K28)的Modified Compliance Pattern,即 K28.5, D21.5, K28.5, D10.2, error status Symbol, error status Symbol, K28.5,K28.5。Modified Compliance Pattern的第一个符号必须具有负差异。允许创建差异错误(disparity error),以使执行差异(running disparity)与第一个Modified Compliance Sequence 符号的负差异对齐。对于具有多个通道的任何给定设备,每八个通道总共移动八个符号。在八个Symbol Modified Compliance Pattern sequence的开头,出现了K28.5的四个符号,在结尾出现了另一个K28.7的四个符号。第一个D符号具有负差异,以使延迟差异与Modified Compliance Sequence的差异对齐。发送16个符号后,延迟符号将前进到下一个通道,直到在所有八个通道上都发送了延迟符号。然后,延迟符号循环回到通道0,并重复该过程。无论检测到或支持的通道数量如何,都可以在所有八个通道上提前延迟序列。x1设备或在x1模式下运行的xN设备允许在Modified Compliance Pattern 中包含 Delay Symbols。

Modified Compliance Pattern 如下:

插入两个相同的错误符号而不是一个错误符号的原因是为了确保8b/10b序列的差异不会受到添加错误状态符号的影响。

所有其他Compliance pattern规则都是相同的(即,用于添加延迟符号的规则),以便保留Compliance pattern的所携带的串扰特性。

error status Symbol是一个8b/10b的D Symbol,在每个通道上都有,其各字段定义如下:

Receiver Error Count (Bits 6:0):当某Pattern Lock 有效,这个字段就递增。

Pattern Lock (Bit 7):当某 Lane 锁定了输入的Modified Compliance Pattern 该字段就有效。

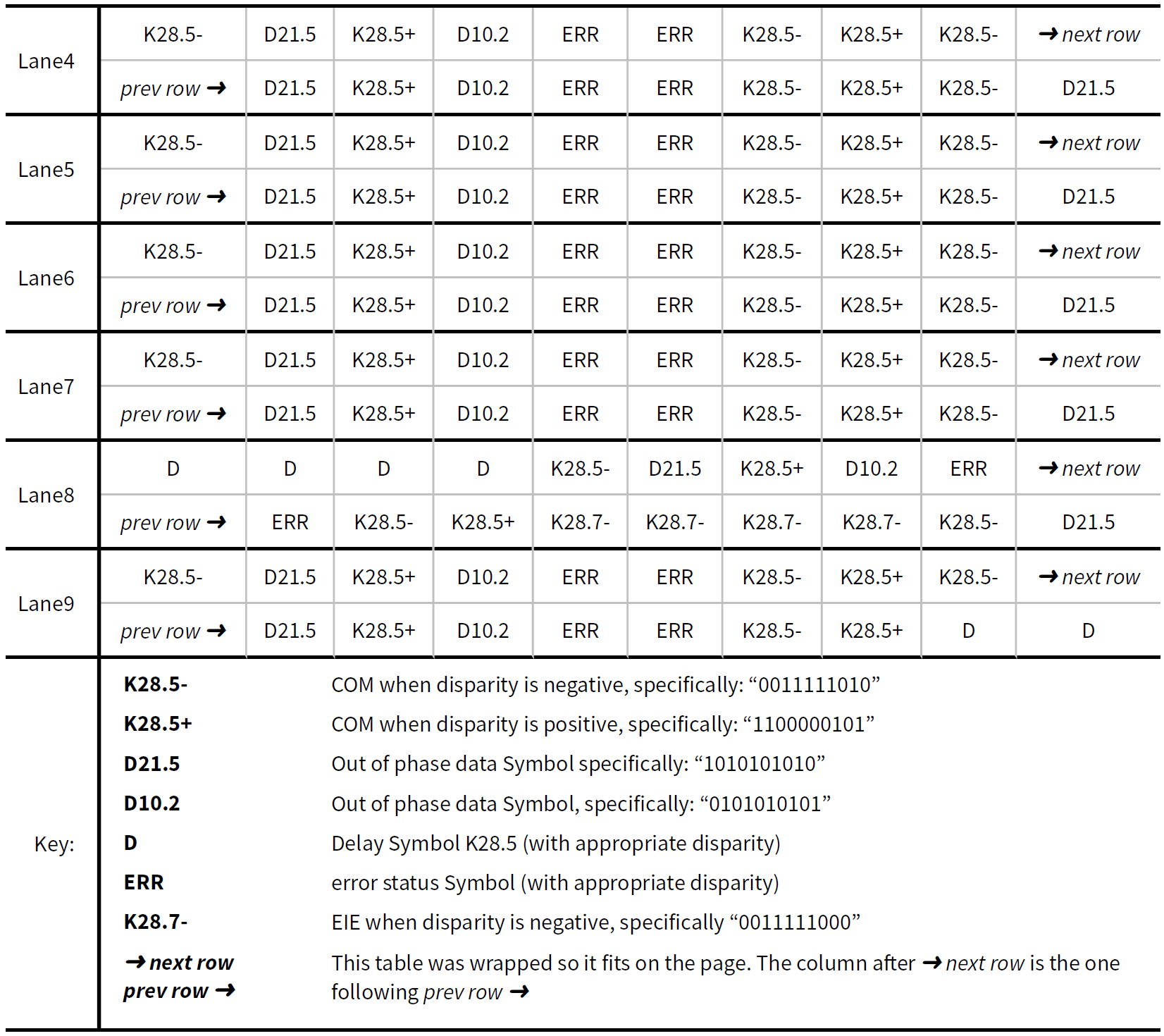

4.2.10 Compliance Pattern in 128b/130b Encoding

128b/130b编码下的Compliance Pattern由以下36个block的重复序列组成。

-

Sync Header 为'01b的block,其128bit未加扰的负载由64个1b后跟64个0b组成。

-

Sync Header为'01b的block,其128bit未加扰的负载构成如下:

-

Sync Header 为'01b的block,其128bit未加扰的负载构成如下:

-

一个EIEOS block。

-

32个Data Block,每个Data Block的负载为16个IDL符号(00h)的加扰。

IMPLEMENTATION NOTE

First Two Blocks of the Compliance Pattern

关于Compliance Pattern的头两个Block:第一个Block是一个非常低频的码型,用于测量preset设置。第二个Block 用于说明 Lane number和preset编码,以确保Compliance Pattern是DC平衡的。

每个Data Block中的有效载荷是该通道中加扰器的输出(即输入数据为0b)。Sync Header是不加扰的。当发送EIEOS时,加扰器被初始化。用于LFSR种子值的Lane number是取决于如何进入Polling.Compliance状态的。如果通过配置Link Control 2寄存器中的Enter Compliance而进入,则Lane number就是是分配给通道的编号,并且要在每个通道上使用的接收器通道极性就是在最近一次LinkUp为1b时使用的。如果Lane不是之前已配置的链路的一部分,并且对于所有其他进入Polling.Compliance的方法,则Lane number是端口分配的默认号。这些默认数字必须唯一。例如,必须为x16链路的每个通道分配一个唯一的Lane number (介于0到15之间)。Compliance Pattern的Data Block不构成数据流,因此在有序集块到数据块的过渡期间无需传输SDS有序集或EDS Token,反之亦然。

IMPLEMENTATION NOTE

Ordered Sets in Compliance and Modified Compliance Patterns in 128b/130b Encoding

各种有序集(例如 EIEOS 和 SKP OS)遵循与当前操作数据速率相对应的有序集定义。例如,在32.0GT/s数据速率下,EIEOS为32.0 GT/s EIEOS;在16.0GT/s 数据速率下,EIEOS为16.0 GT/s EIEOS;而在8.0GT/s 数据速率下,EIEOS 为 8.0 GT/s EIEOS。如Section 4.2.7 定义,SKP有序集是标准 SKP 有序集。

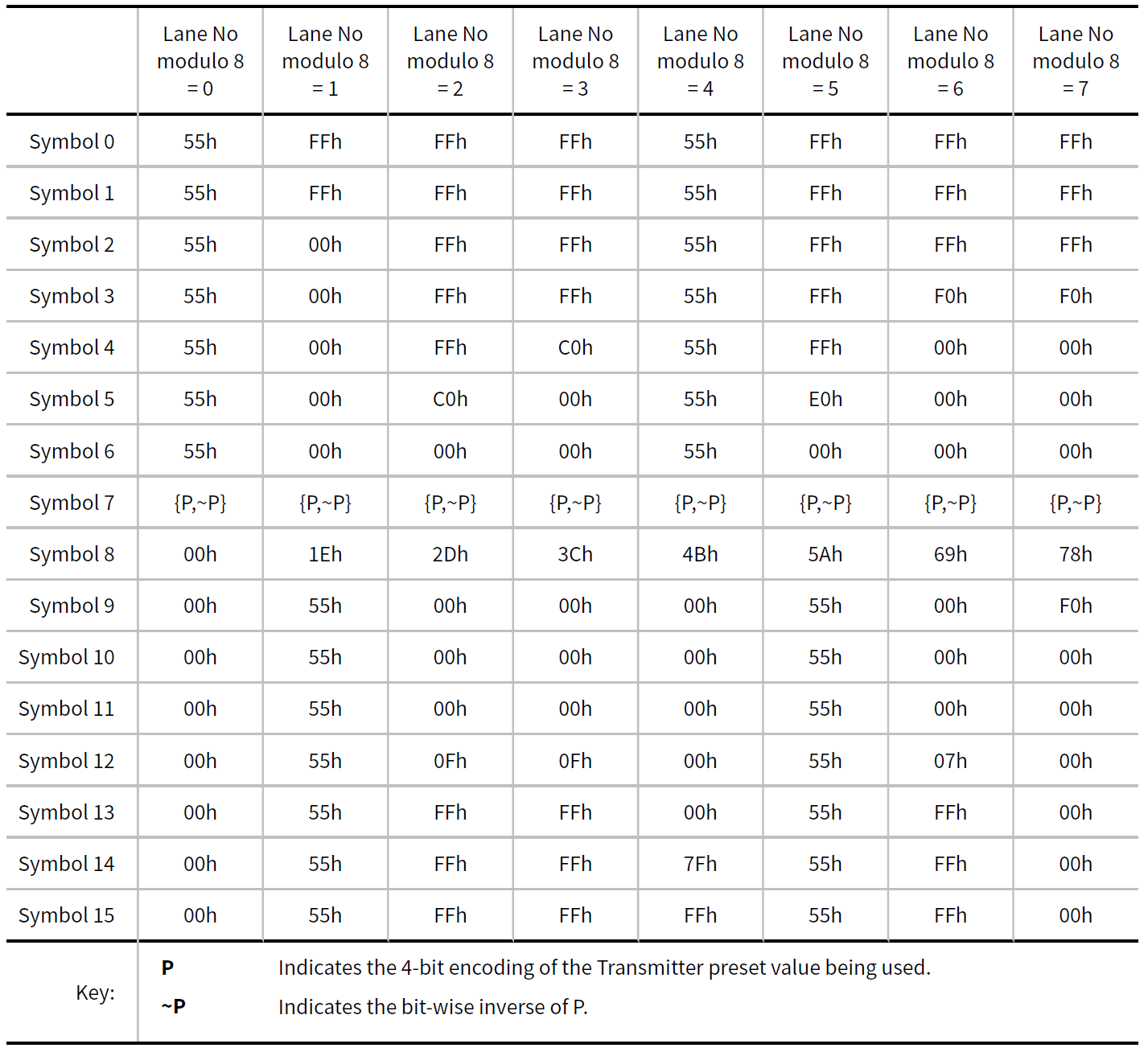

4.2.11 Modified Compliance Pattern in 128b/130b Encoding

128b/130b编码下的 Modified Compliance Pattern 由以下的65792个Block组成:

-

一个EIEOS Block。

-

256个Data Block,其中每个对其中的16个IDL Symbol加扰。

-

255组下列序列组成:

一个SKP Order Set。

256个Data Block,其中每个对其中的16个IDL Symbol加扰。

每个Data Block中的有效载荷是该通道中加扰器的输出(即输入数据为0b)。Sync Header是不加扰的。当发送EIEOS时,加扰器被初始化。用于LFSR种子值的Lane number是取决于如何进入Polling.Compliance状态的。如果通过配置Link Control 2寄存器中的Enter Compliance 而进入,则Lane number就是是分配给通道的编号,并且要在每个通道上使用的接收器通道极性就是在最近一次LinkUp为1b时使用的。如果Lane不是之前已配置的链路的一部分,并且对于所有其他进入Polling.Compliance的方法,则Lane number是端口分配的默认号。这些默认数字必须唯一。例如,必须为x16链路的每个通道分配一个唯一的Lane number (介于0到15之间)。Modified Compliance Pattern的Data Block 不构成数据流,因此在有序集块到数据块的过渡期间无需传输SDS有序集或EDS Token,反之亦然。

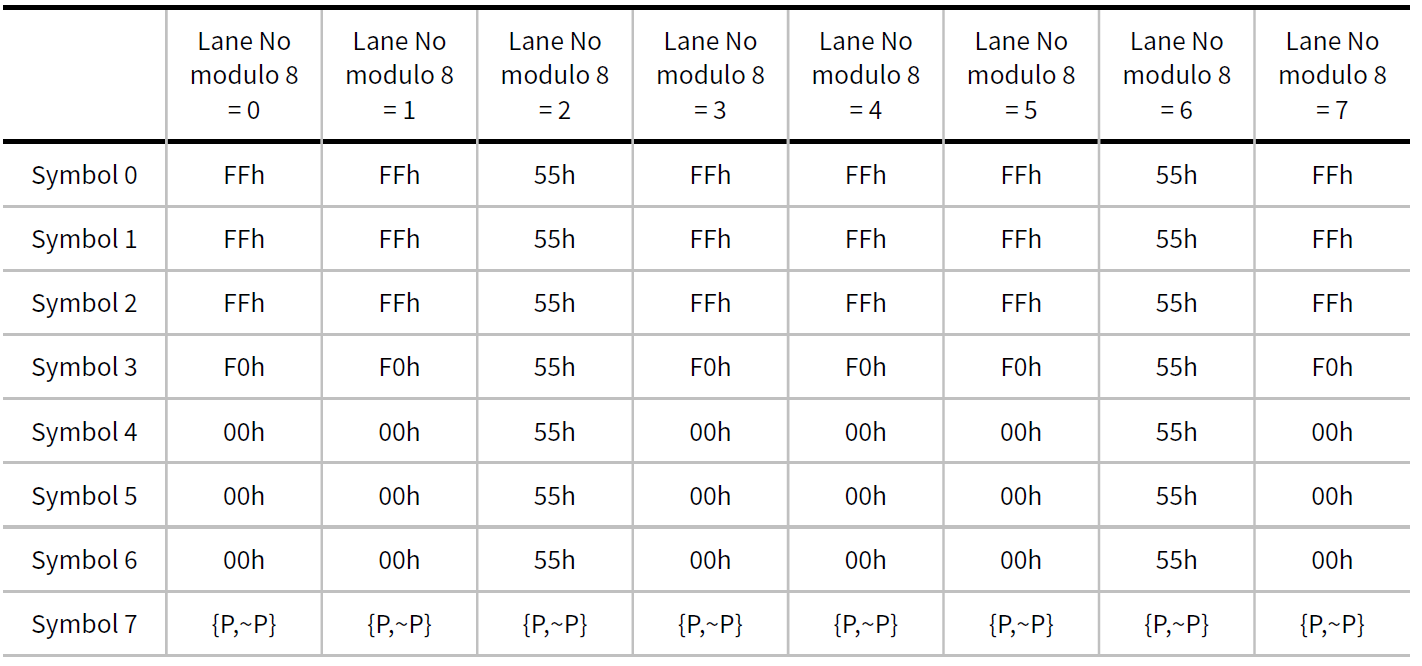

4.2.12 Jitter Measurement Pattern in 128b/130b

抖动测量码型由以下重复块构成:

01b的Sync Header后跟16个55h的Symbol的128 bit未加扰有效载荷。

这会生成交替的1和0码型,用于测量发送器的抖动。

4.2.13 Lane Margining at Receiver

本节中定义的接收器上的Lane Margining对于支持 16.0 GT/s 或更高数据速率的所有端口都是强制性实现的,这包括Pseudo Ports (Retimer)。当链路处于LO状态时,接收器上的Lane Margining使系统软件能够获取给定接收器的裕量信息。裕量信息包括从当前接收器位置的任一方向的电压和时间。对于在接收器上实现Lane Margining的所有端口,接收器处关于时序的Lane Margining 是必须的,而在16.0GT/s和32.0 GT/s 和更高的数据速率时需要在接收器处对电压进行Lane Margining支持。

当接收到一个Margin Command、链路以16.0 GT/s或更高的数据速率运行且链路处于LO状态时,接收器的Lane Margining 开始。当接收到Go to Normal Settings command,链路改变速率或链路退出LO或Recovery状态时,接收器上的Lane Margining结束。当超过某些错误阈值时,接收器的Lane Margining 可选择实现为结束。对于独立采样器,当链路处于Recovery状态时,允许暂停接收器的Lane Margining。

以2.5 GT/s、5.0 GT/s或8.0 GT/s 运行的 PCle 链路不支持接收器上的Lane Margining。

软件使用每个端口(下游或上游)中的每个通道Margining Lane Control Register 和 Margining Lane Status Register 来发送 Margin Command 并获取与端口相关联的相应接收器的裕量状态信息。对于Retimer,获取有关接收器的能力和状态的信息的命令以及为接收器设置裕度的命令在下游方向的Control SKP Ordered Set中传送。目标Retimer接收器的状态和错误报告在上行方向的Control SKP Ordered Set 中传送。软件通过写入 Downstream Port 中 Margining Lane Control Register中的对应字段来控制 Retimer 接收器中的裕量。Downstream Port还更新由链路中的Retimer通过Control SKP Ordered Set传送到其 Margining Lane Status Register 中的状态信息。

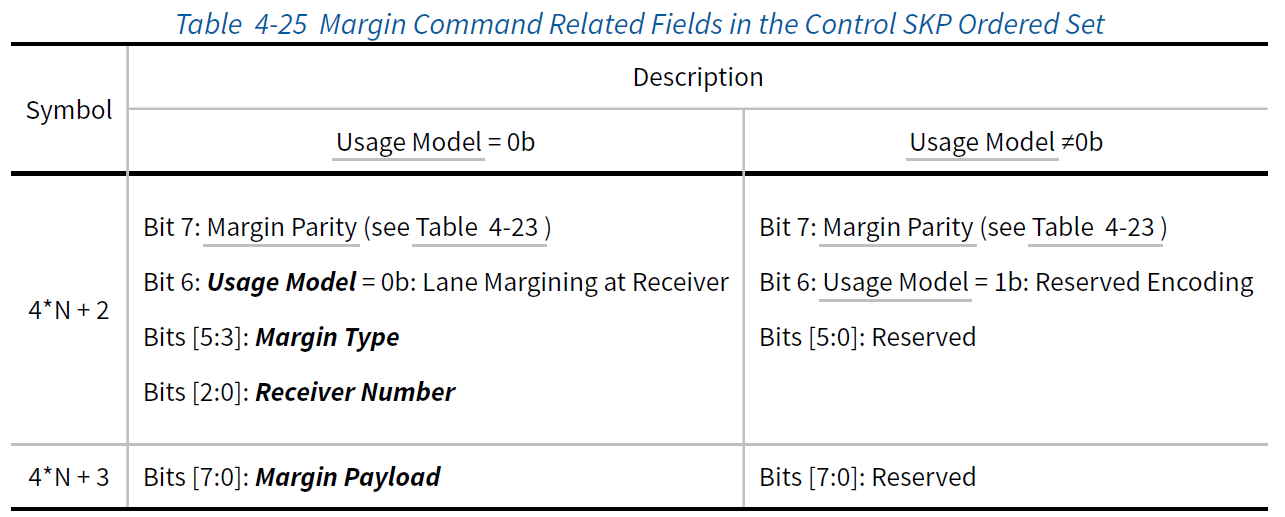

4.2.13.1 Receiver Number, Margin Type, Usage Model, and Margin Payload Fields

Downstream Port 中 Margining Lane Control Register 的四个命令字段的内容总是反映在 Downstream Control SKP Ordered Sets 中的相同字段中。在Downstream Port 接收到的Upstream Control SKP Ordered Set的内容总是反映在Downstream Port的 Margining Lane Status Register的相应状态字段中。下表给出了这些字段在Control SKP Ordered Set中的比特位信息。