ARM芯片架构之CoreSight SoC-400 组件介绍

CoreSight SoC-400 组件介绍

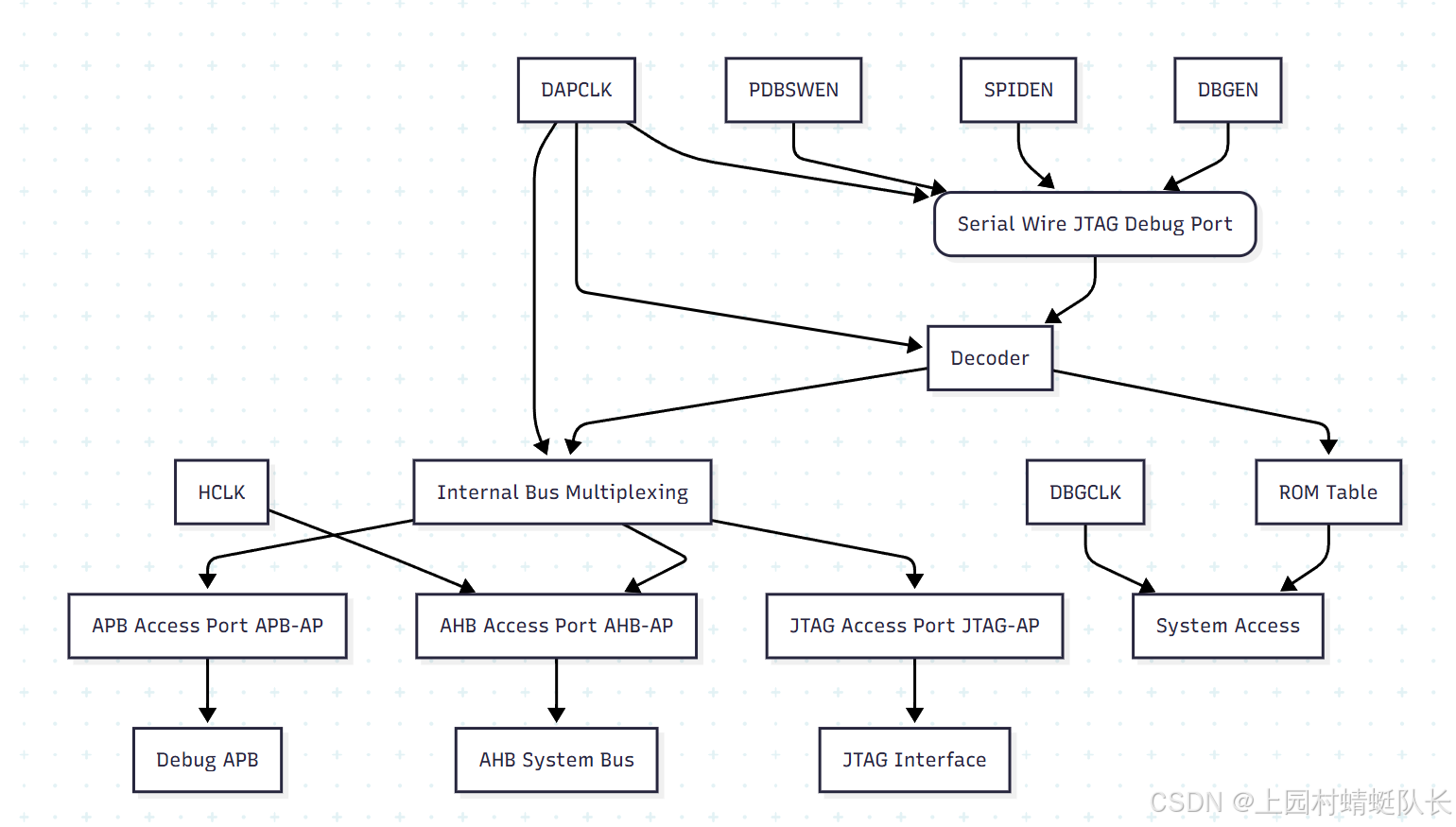

1. Debug Access Port (DAP)

- 功能:DAP 是外部调试器与 SoC 内部调试基础设施的接口核心。它将调试端口(JTAG-DP 或 SW-DP)与多个访问端口(AP)连接起来,使调试器能够访问内存、外设寄存器以及 CoreSight 组件。

- 关键点:

- 支持多种 AP 类型(AHB-AP、APB-AP、AXI-AP)。

- 可通过选择机制访问不同的调试目标。

- 负责调试访问的仲裁与路由。

- 技术实现:

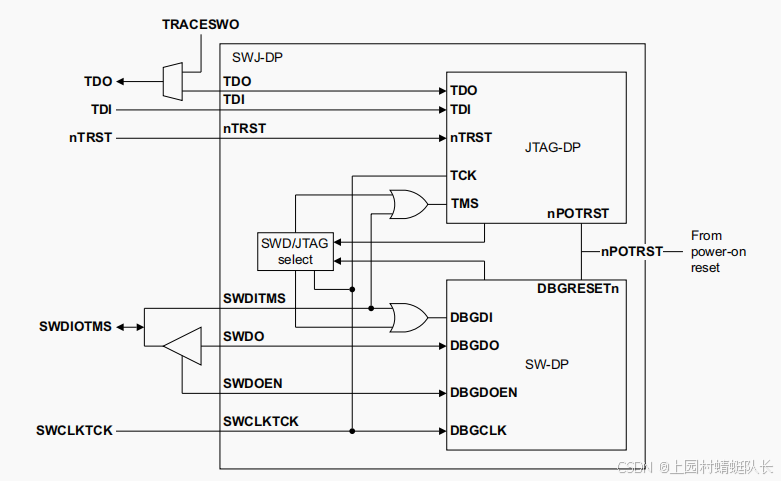

- SWJ-DP(Serial Wire/JTAG Debug Port)

- 双协议支持:同时处理SW-DP(串行线协议)和JTAG-DP(传统JTAG协议)

- 电源管理机制:

- 通过

cdbgpwrupreq信号请求调试域上电 - 通过

csyspwrupreq信号请求系统域上电 - 接收电源控制器的

cdbgpwrack和csyspwrack确认信号

- 通过

- AP(Access Port)子系统:

- AXI-AP:将调试请求转换为AXI总线事务(支持AXI3/AXI4)

- APB-AP:生成APB总线访问(32位地址空间)

- JTAG-AP:直接访问JTAG接口的处理器调试资源

- DAPBUS互联架构:

- 通过DP的

SELECT寄存器路由请求(dapcaddrs[15:8]选择AP) - 支持多AP并行访问(最大256个AP)

- 时钟域隔离:独立调试时钟与系统时钟域

- 通过DP的

2. Debug Port (DP)

- 功能:提供物理层调试链路接口,支持 JTAG 或 Serial Wire Debug 协议。

- 关键点:

- JTAG-DP 提供多信号调试接口,带宽较高。

- SW-DP 提供双线接口,减少引脚占用。

- 管理调试连接的建立、保持与终止。

- 功能:作为外部调试工具访问SoC内部资源的核心枢纽

3. Access Ports (AP)

- 功能:AP 是 DAP 后端的访问节点,负责通过指定总线协议与系统内部资源交互。

- 类型:

- AHB-AP:通过 AHB 总线访问系统内存与外设。

- APB-AP:通过 APB 总线访问低速外设及 CoreSight 配置寄存器。

- AXI-AP:提供高带宽 AXI 总线访问能力。

- 作用:为调试器提供对系统总线的直接读写访问。

4. Embedded Trace Macrocell (ETM)

- 功能:ETM 是高精度指令跟踪单元,可实时记录处理器执行路径。

- 关键点:

- 提供精确的分支与跳转跟踪。

- 支持基于事件的触发与停止。

- 可插入上下文 ID、时间戳信息,帮助性能分析。

5. Program Trace Macrocell (PTM)

- 功能:提供程序流的压缩跟踪数据,用于较低带宽的 trace 输出。

- 特点:

- 对于分支、跳转等事件提供编码信息。

- 资源占用与功耗较低,适用于资源受限系统。

6. System Trace Macrocell (STM)

- 功能:产生系统级事件 trace,可由软件或硬件触发。

- 关键点:

- 支持多通道数据输入。

- 软件可直接写 Stimulus 寄存器生成 trace 数据包。

- 常用于操作系统事件跟踪与性能分析。

7. Instrumentation Trace Macrocell (ITM)

- 功能:面向 Cortex-M 系列,支持事件记录与时间戳插入。

- 特点:

- 与 DWT(Data Watchpoint and Trace)结合使用。

- 用于嵌入式系统的轻量级调试。

8. Trace Funnel

- 功能:将多个 trace 数据源合并为一条 ATB 数据流。

- 关键点:

- 支持通道使能与屏蔽。

- 可配置输入优先级,确保关键 trace 数据优先传输。

9. Trace Replicator

- 功能:将一条 ATB trace 数据流复制到多个目的地。

- 应用:

- 同时将 trace 数据发送到片上缓冲(ETB)和外部接口(TPIU)。

- 在调试和性能分析中并行使用多个 trace sink。

10. Embedded Trace Buffer (ETB)

- 功能:片上环形缓冲区,用于存储 trace 数据。

- 关键点:

- 支持停止模式(Stop-on-full)和循环模式(Circular Buffer)。

- 适合无外部 trace 接口时的事后分析。

11. Trace Memory Controller / ETR

- 功能:管理 trace 数据向片上 RAM 或系统内存的传输。

- 特点:

- ETR 支持通过 AXI 接口直接写入 DDR 内存。

- 提供更大容量的 trace 存储能力。

12. Trace Port Interface Unit (TPIU)

- 功能:将 trace 数据格式化并输出到外部调试器或分析工具。

- 特点:

- 支持并行和串行 trace 输出模式。

- 可选输出速率和协议类型。

13. High-Speed Serial Trace Port (HSSTP)

- 功能:将 trace 数据通过高速串行链路输出,减少引脚数。

- 特点:

- 高速率传输,适合带宽需求大的 trace。

- 常配合外部专用采集设备使用。

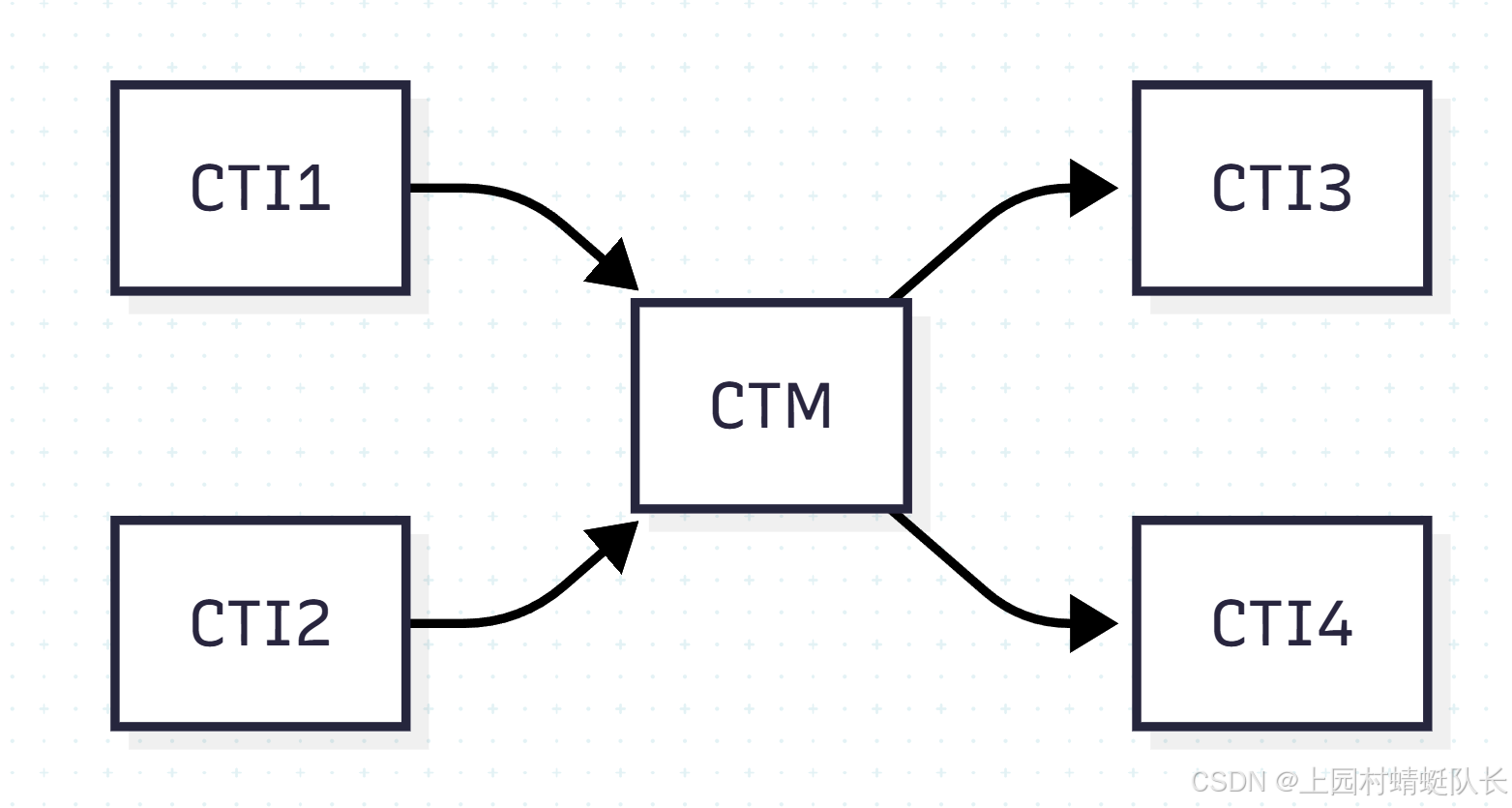

14. Cross Trigger Interface (CTI) & Cross Trigger Matrix (CTM)

- 功能:在不同调试组件或处理器之间传播触发事件。

- 关键点:

- CTI 负责事件输入/输出的管理。

- CTM 作为交换矩阵连接多个 CTI,实现复杂的触发网络。

- 可用于同步多核 trace 的开始和停止。

15. Timestamp Generator

- 功能:为 trace 数据流添加统一的时间戳。

- 作用:

- 允许多个 trace 源数据对齐到同一时间基准。

- 支持高分辨率计时,便于性能分析。

16. ROM Table

- 功能:提供所有 CoreSight 组件的基地址映射。

- 应用:

- 调试工具可自动扫描 ROM Table,识别系统中存在的调试组件。

- 简化调试基础设施的自动发现过程。