BKP 与 RTC 时钟

1. 为什么需要 BKP 与 RTC

RTC 提供低功耗、掉电保持的日历与秒计数能力,是日志时间戳、定时任务、离线设备“走时”的基础。

BKP 备份域在主电源 VDD 断电时,由 VBAT 维持,里面的 RTC、备份寄存器、部分控制/状态逻辑仍可保持工作/记忆。

组合优势:掉电不丢时间、系统复位不清零、可记录“上次校时标志/序列号/参数”。

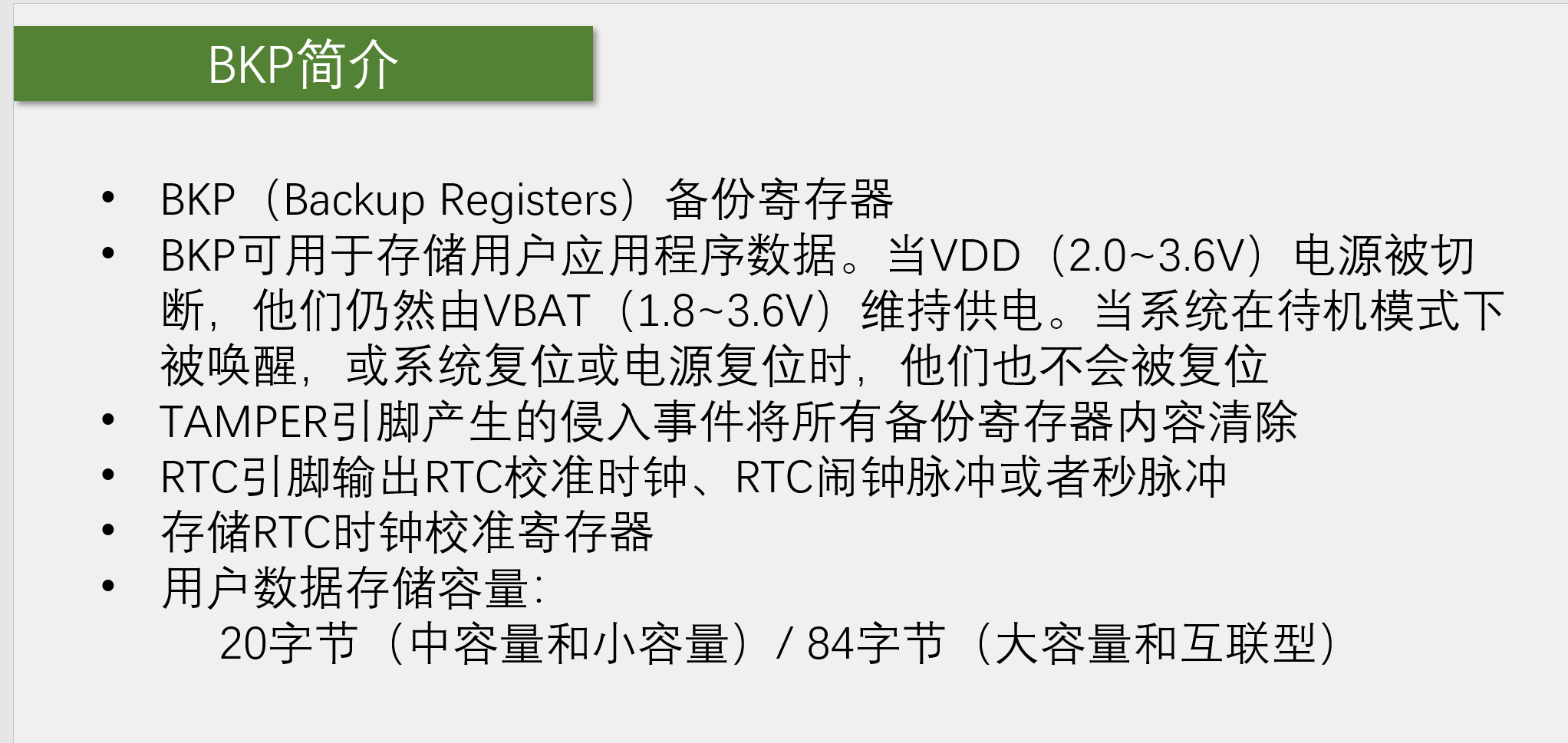

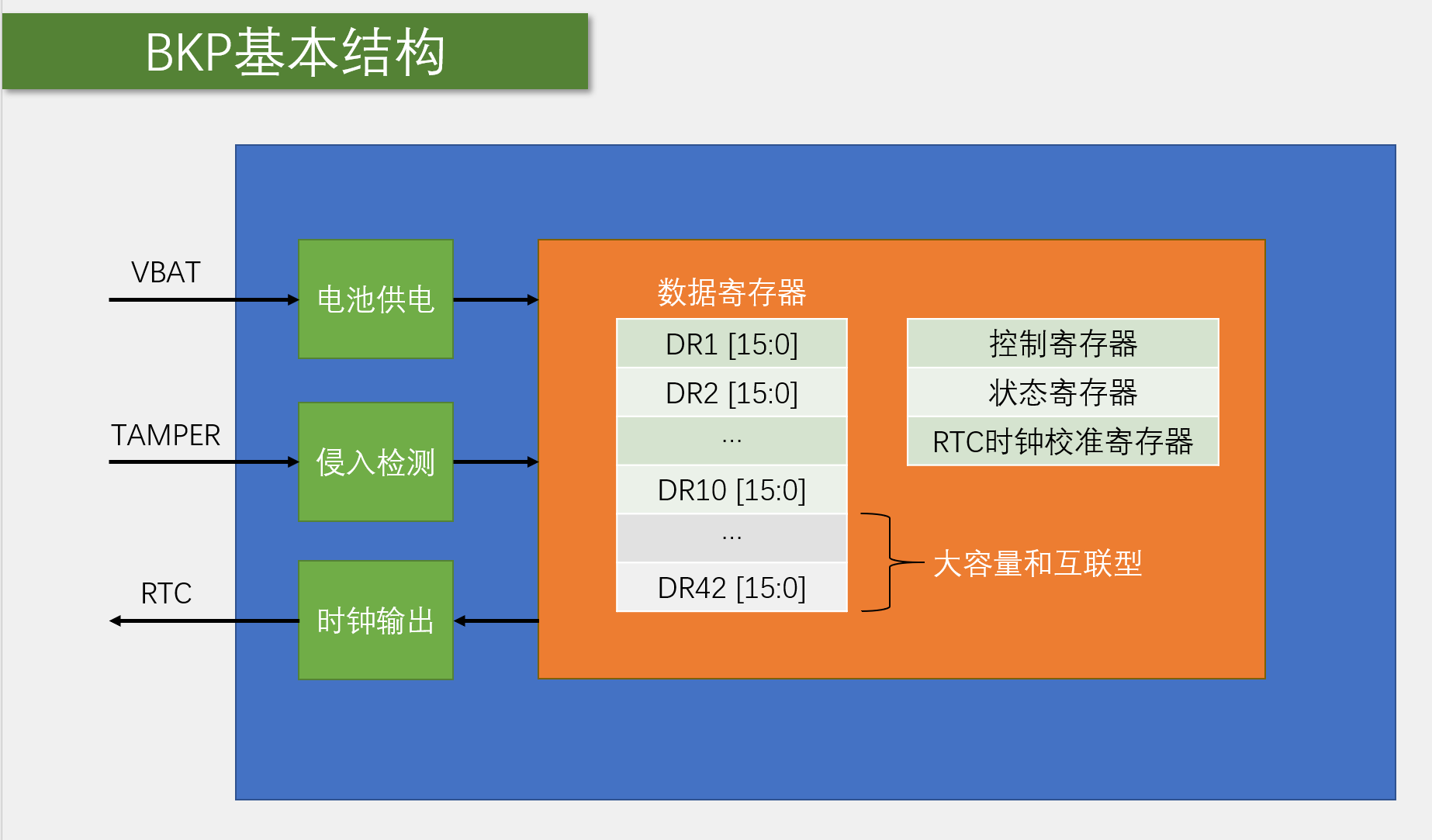

2. 备份域(BKP)到底包含什么

以 STM32F1 为例(不同子系列容量不同)

供电路径:VDD 正常供电;掉电后由 VBAT(1.8–3.6V) 维持。

数据寄存器 DRx:16 位若干个(如 DR1…DR42),可存应用数据、标志、CRC、序列号等。

控制/状态:BKP/RTC 访问使能、校准相关位、时钟源选择、复位/同步标志。

Tamper:防拆/入侵检测引脚,触发时可选自动清空 DRx。

RTC 校准/输出相关寄存器:用于粗调 RTC 走时,或输出 1 Hz 等信号到外脚。

典型用途

“是否已校时”标志位

设备首次运行时间、累计工作时长

最近一次 Unix 时间戳、时区/偏移

小量配置参数(掉电保持)

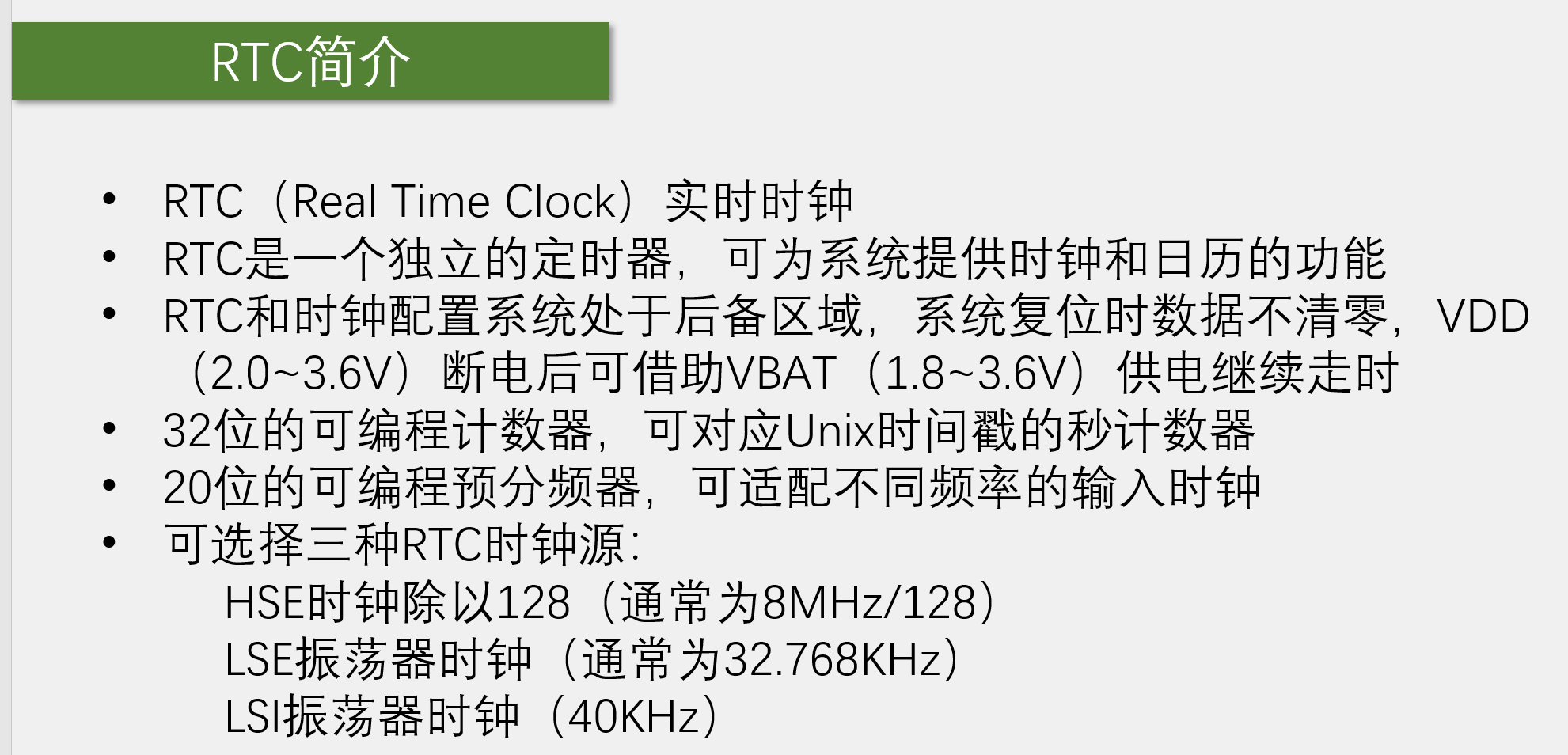

3. RTC 简介与时钟源

3.1 RTC 的职责

以指定时基(LSE/LSI/HSE/128)计数,经预分频得到 1 Hz 秒脉冲。

32 位可编程计数器 CNT 以 1 Hz 递增(常见模型),可直接作为**“秒计时器”**使用。

提供 Alarm(ALR)、Second(SEC)、Overflow(OW) 等事件/中断。

3.2 三类常见 RTC 时钟源

| 时钟源 | 典型频率 | 优点 | 缺点 | 典型用途 |

|---|---|---|---|---|

| LSE 外部低速晶振 | 32.768 kHz | 精度好、温漂小、功耗低 | 启振慢,对电路要求高 | 推荐为 RTC 主时基 |

| LSI 内部 RC | 约 40 kHz | 无需外部器件、启动快 | 精度差,温漂大 | 无法上晶振或精度要求不高 |

| HSE/128 分频 | 8 MHz/128=62.5 kHz(示例) | 复用已有晶振 | 功耗较高、受系统时钟影响 | 少用,适合无 LSE 场景 |

工程建议:如无特殊限制,优先 LSE。需要“即插即用”且不追求长期精度可考虑 LSI。

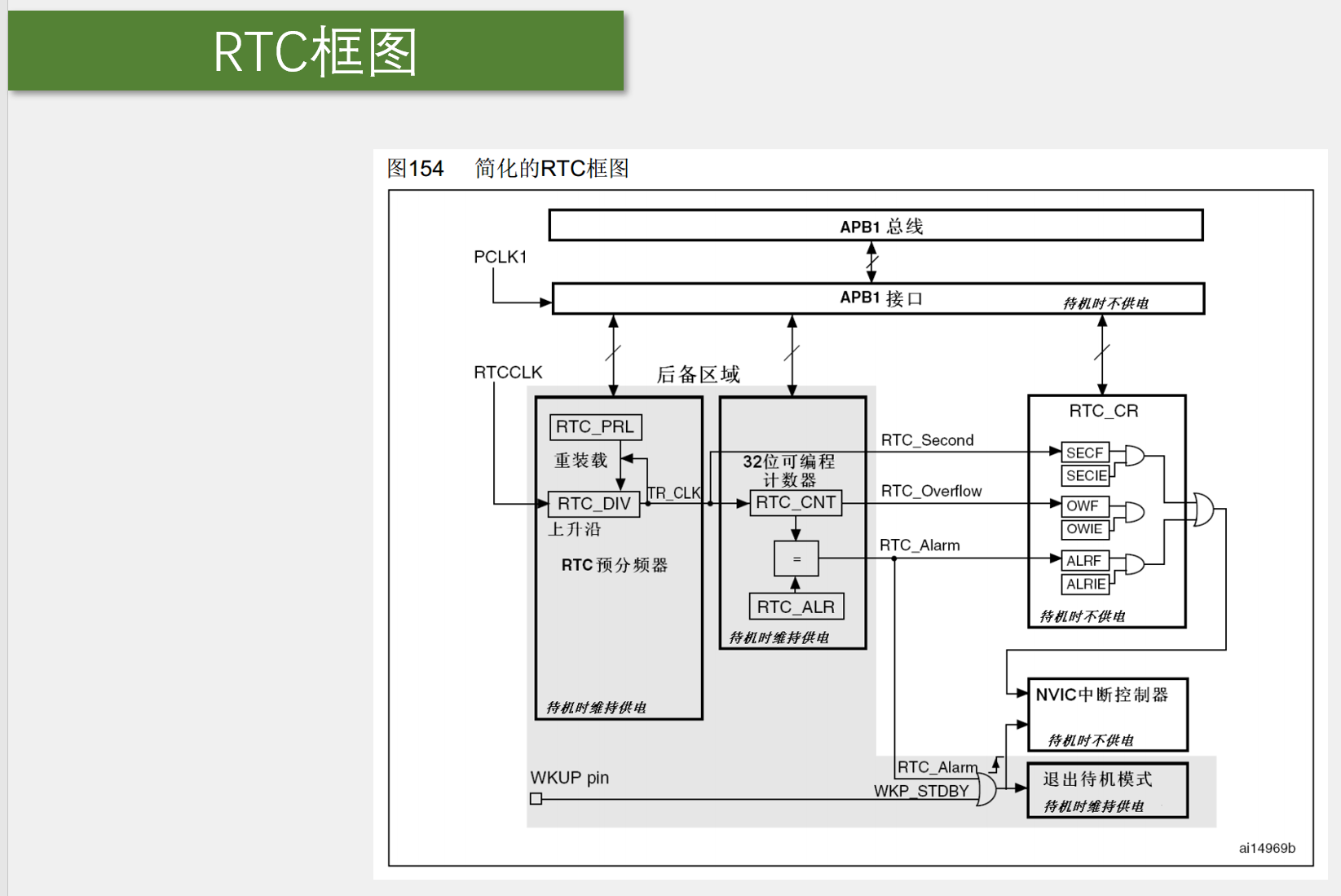

4. RTC 内部框图与寄存器作用

以 “PRL/DIV/CNT/ALR + 三类中断” 为核心链路:

PRL(预分频重装值):设置“预分频目标值”。当计数器从该值减到 0 时产生 Second 事件并重装。

DIV(余数寄存器/当前预分频计数):实时显示预分频器的计数状态(只读)。

CNT(32 位计数器):通常以 1 Hz 递增,代表“秒数”。可直接写入初值。

ALR(闹钟值):当

CNT == ALR时产生 Alarm 事件。溢出(Overflow):

CNT回绕时产生 OW 事件。

中断与标志位(在 RTC_CRL/RTC_CRH):

SEC/SECF/SECIE:每秒中断/标志/中断使能

ALR/ALRF/ALRIE:闹钟中断/标志/中断使能

OW/OWF/OWIE:溢出中断/标志/中断使能

RSF:寄存器同步完成标志(读前要等 1)

RTOFF:写操作完成标志(配置结束前须等 1)

CNF:配置模式使能(写 PRL/CNT/ALR 前必须置位)

关键流程记忆:

读寄存器前 等 RSF=1 → 进入配置 CNF=1 → 写 PRL/CNT/ALR → 退出配置 CNF=0 → 等 RTOFF=1

5. 选择分频参数:从时钟源到 1 Hz

假设 RTCCLK = 32768 Hz (LSE),希望 CNT 每秒加 1,则:

预分频器目标为 32768-1 = 32767(从 32767 计到 0 一共 32768 个脉冲)

将 PRL = 32767,

Second事件即为 1 Hz。

不同内核/系列差异:F2/F4 以后多为 异步/同步双预分频(

PREDIV_A/PREDIV_S),但本质相同:RTCCLK / ((PREDIV_A+1)*(PREDIV_S+1)) = 1 Hz。F1 系列常见的是“PRL(重装值)+ DIV(当前计数)”。

6. 校准(Calibration)与精度评估

ppm 转“每天偏差秒数”:

20 ppm ≈ 1.728 s/天,1 个月约快/慢 ~ 52 s。

校准手段:

硬件校准寄存器(如

BKP_RTCCR或新 RTC 的平滑校准):通过丢/补时钟脉冲微调频率。策略校准:定期 NTP/GPS/上位机校时,以秒级“微调”(不要大跳,避免业务抖动)。

7. Tamper(入侵检测)

通过 TAMPER 引脚或内部事件检测入侵,配置后可在触发时 自动清除所有 BKP 数据寄存器 并产生中断/事件。

适合敏感数据的“防篡改自毁”:密钥、授权信息等存 BKP;一旦 Tamper 触发立即清除。

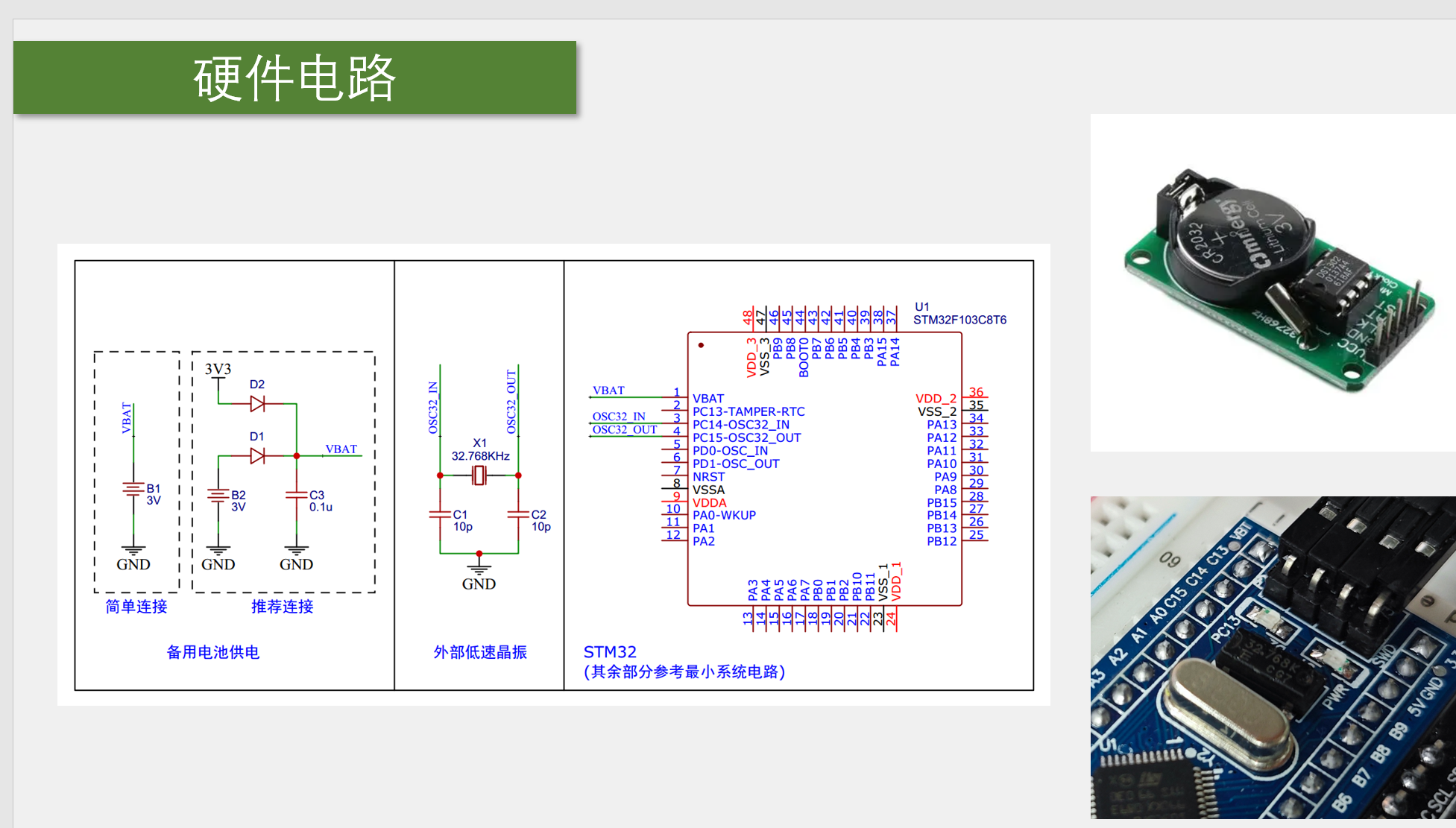

8. 硬件电路与选型要点

8.1 VBAT 供电(两路“或”)

常见做法:主 3.3 V 与纽扣电池通过肖特基二极管做“或门”,再到 VBAT;旁路 0.1 µF 去耦。

选择低正向压降二极管,降低掉电切换时的压降变化。

8.2 LSE 晶振电路

频率 32.768 kHz,数据手册会给出推荐 负载电容 C_L 与 驱动电平。

外部电容计算(粗略):

若

C_L = 12.5 pF、板级杂散C_stray ≈ 2–3 pF,则C1=C2 ≈ 18–21 pF;实际以原厂推荐值为准。关注 ESR 与 Drive Level,避免过驱导致老化或启振失败。

8.3 外置 RTC 模块(如 DS3231)

I²C 接口、内置温补,精度优于裸 LSE,可作为需要高长期稳定性场景的方案。

9. 访问备份域与 RTC 的“必备步骤”

开启时钟:

RCC_APB1ENR打开 PWR 与 BKP 时钟。取消写保护:

PWR_CR.DBP = 1,允许访问备份域。选择 RTC 时钟源:使能 LSE 并等待稳定;选择为

RTCCLK。使能 RTC:

RCC->BDCR.RTCEN = 1。等待同步:读/写前等待

RSF=1。进入配置:

CNF=1;写 PRL/CNT/ALR。退出配置:

CNF=0;等待RTOFF=1。使能中断(可选):

SECIE/ALRIE/OWIE,并配置 NVIC。恢复写保护:

DBP=0(上线产品建议)。

注意:改变 RTC 时钟源会复位备份域(不同系列略有差异),必要时先备份再恢复。