基于ZYNQ ARM+FPGA的声呐数据采集系统设计

目前对声呐数据采集系统的研制,一般选择微

处理器或微控制器、现场可编程门阵列 (field

programmable gate array, FPGA) 或者是数字信号处

理器 (digital signal processor, DSP) 等芯片作为主控

芯片。王敏等[8]采用 DSP 运行 Vxworks 操作系统

实现传输控制协议/互联网协议 (transmission control

protocol/internet protocol, TCP/IP) 网络协议栈,可

以实时将声呐系统采集的数据以及计算结果回传到

计算机。张严品[9]基于 OMAP-L138 芯片设计的水

声信号采集与处理平台,实现了对水声信号的连续

采集、处理、存储和传输等功能,通过轻量级网络

协议栈 (light weight IP, LwIP) 实现安全数字卡中存

储水声数据的上传功能。荣致远[10]结合 FPGA 的

高 速 并 行 处 理 能 力 以 及 高 级 精 简 指 令 集 机器

(advanced RISC machine, ARM) 处理器灵活的进程

控制能力,设计了一种基于 FPGA+ARM 的声呐数

据采集传输系统,满足采集系统高精度和实时性的

要求。荆博原等[11]采用 Artix-7 系列 FPGA 芯片控

制数据的采集与存储来完成多通道数据采集,通过

通用串行总线 2.0 接口将矢量水听器数据传输至上

位机。史鹏腾[12]使用以太网知识产权核实现用户数

据包协议来进行多通道声呐采集数据的高速传输,

并在应用层制定了与上位机交互及丢包处理的通信

协议,克服了用户数据包协议这类不可靠的、面向

无连接的协议带来的数据错误和缺失等问题。

在上述文献中,对声呐数据采集系统的设计主

要集中于使用 DSP 或 FPGA 等单一架构芯片,无

法兼顾利用微处理器以及 DSP 等串行处理器可方

便实现网络协议栈等复杂控制逻辑,以及 FPGA

具有的强大并行处理的优势。但使用 DSP+FPGA

架构也存在一系列问题[13-14]:首先是布线工作相对

比较复杂,需要完成更多的硬件设计工作。其次,

集成度较低,占用面积较大,成本较高。在能耗和

散热方面,这种方案在计算密集任务下会产生较高

的能耗,需要更好的散热以及供电解决方案。目

前,声呐数据采集系统的设计中鲜见水密条件下的

在线程序更新功能,以及使用 TCP 传输协议进行

数据传输时对数据封帧的考虑。

针对 UUV 前置主动声呐小型化、高集成、低

功耗设计,以及水下封闭空间工作条件下程序更新

的需求,本文选择 Xilinx 推出的 Zynq7020 芯片构

建主动声呐数据采集平台。该芯片采用先进的双核

异构架构[15-17],将可编程逻辑单元 (programmable

logic, PL) 和处理系统单元 (processing system, PS)

集成到一个芯片内,兼顾了 FPGA 的并行计算优

势以及处理器系统软件开发的灵活性,克服了传统

双芯片架构中片间互联通信带宽和处理速度瓶颈限

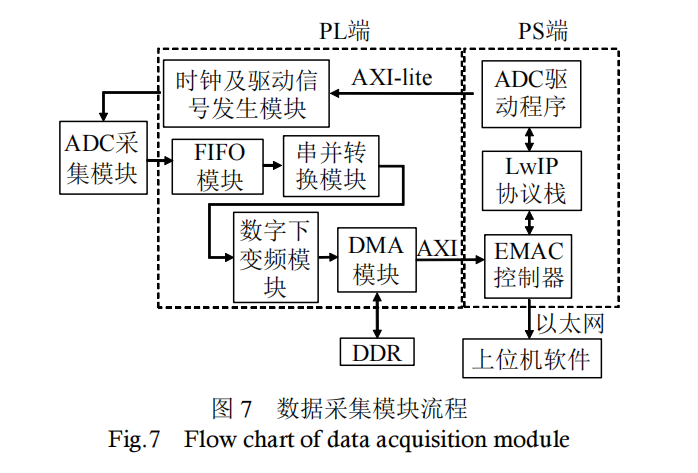

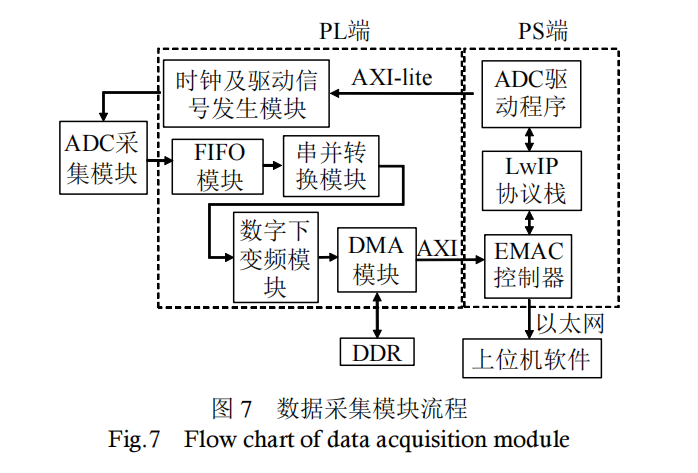

制,集成度高,功耗低。在 PL 端完成数据采集控制

与数字下变频等信号预处理任务,以满足系统实时

性要求。配合开发的上位机软件,在 PS 端的 ARM

处理器上运行 LwIP 网络协议栈实时处理 TCP 数

据流,从而可以充分发挥 Zynq7020 异构架构优

势。对于采集数据传输方案的选择,考虑实时传输

速度、带宽与可靠性要求,本文设计的系统采用以

太网实现主动声呐与上位机软件的数据交互,同时

为保证数据传输的可靠性,本系统采用 TCP/IP 协

议作为数据传输协议,并结合自定义的应用层帧协

议,通过以太网建立下位机与上位机的连接[18]。对

于数据存储介质的选择,系统选用了容量大、读写

速度快的嵌入式多媒体卡 (embeded multimedia card,

eMMC)[19-20]芯片,确保数据记录的完整性和可靠

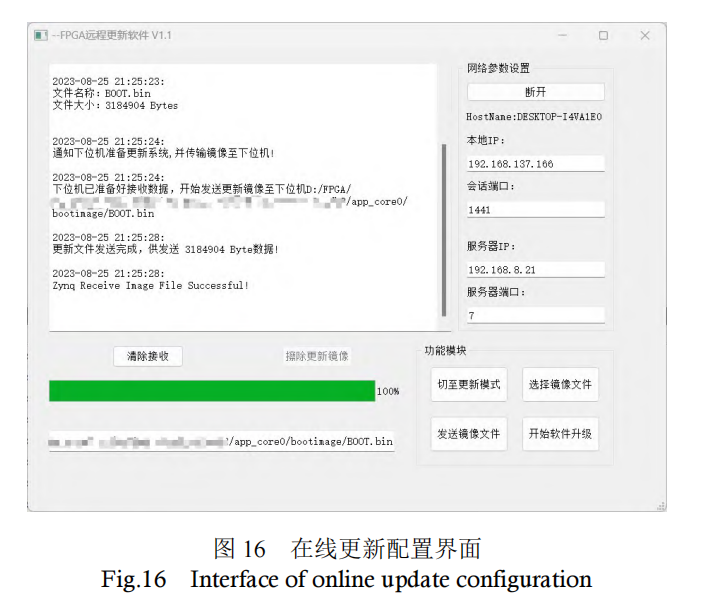

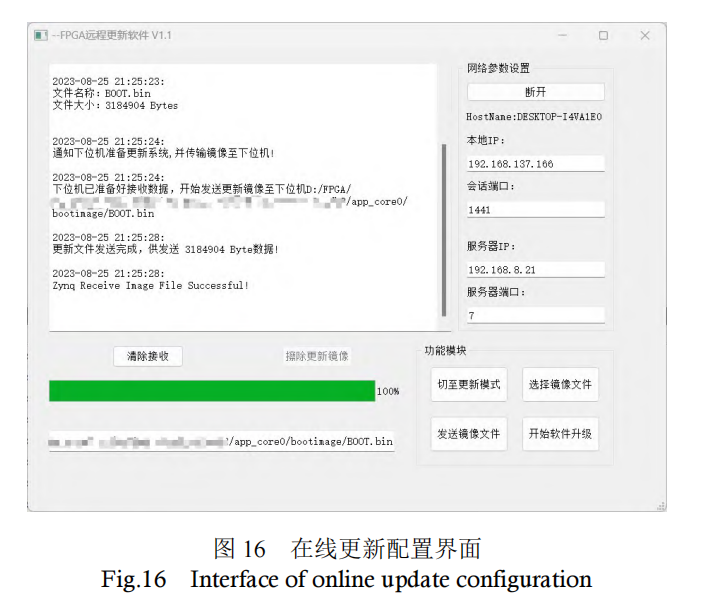

性。对于 FPGA 程序更新方式的选择,系统使用

TCP 以太网实现程序的在线更新,并开发对应的

上位机软件,可以在保证 UUV 水密结构完整的同

时避免复杂的接线操作,方便可控地实现系统

FPGA 程序的更新。

1 系统硬件设计

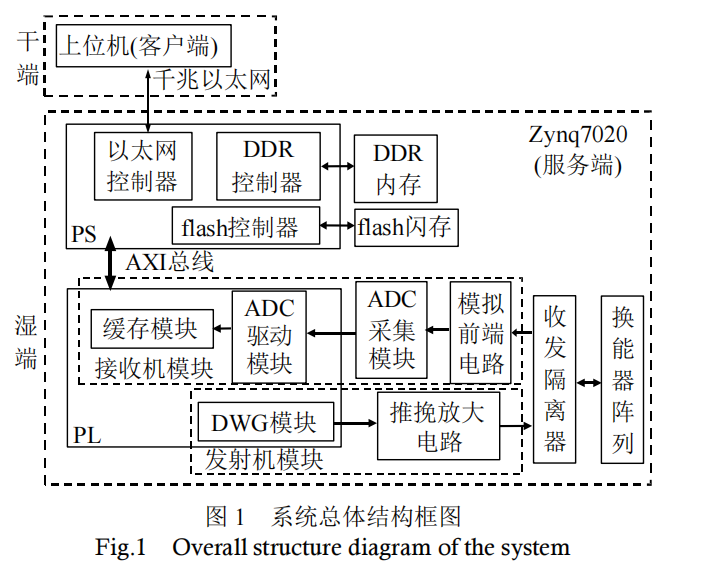

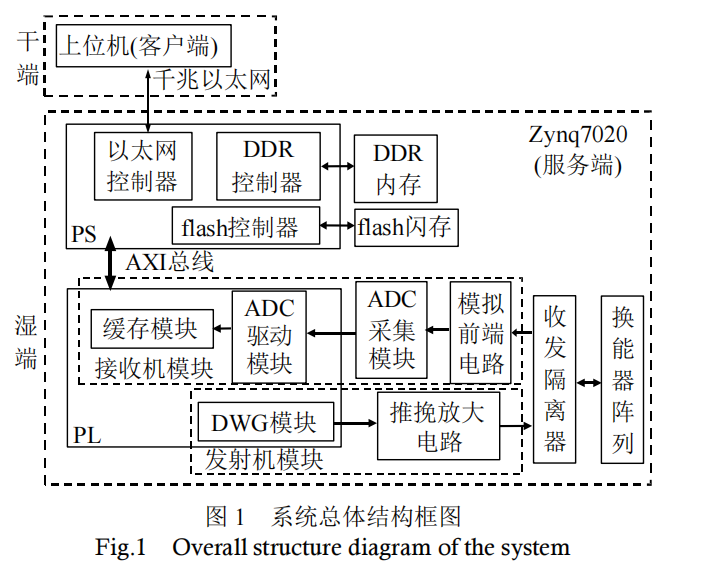

本文系统主要由位于电脑 (PC) 端的上位机软

件以及位于 UUV 内部 (湿端) 的主动声呐发射、接

收电路组成,系统的总体结构如图 1 所示。

4 测试结果与分析

4.1 数据采集部分功能验证

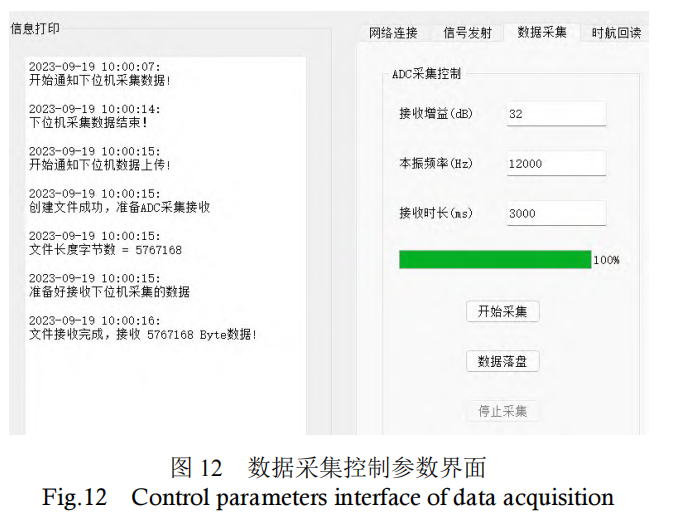

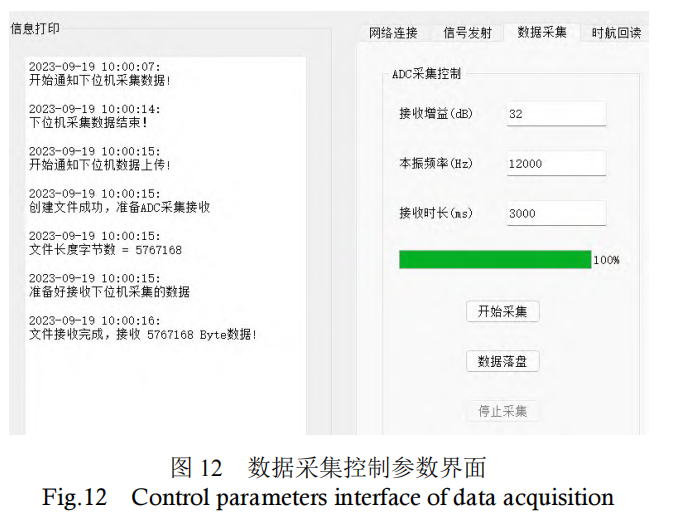

为测试系统数据采集部分功能是否符合预期设

计,选取其中一个采集通道,使用信号发生器产生

一个连续正弦波信号,直接输入到数据采集模块

的 ADC 输入端。输入信号的频率为 13.2 kHz,幅

度为 1 V。上位机数据采集控制参数配置界面如

图 12 所示,设定采集信号长度为 3 s,数字下变频

的中心频率为 12 kHz,点击开始采集按钮,则采

集参数通过以太网下发到下位机,同时通知下位机

数据采集模块开始采集数据。待数据采集完毕后,

点击数据落盘按钮即可通知下位机将采集数据上传

至上位机并保存为.txt 文件。

5 结 论

本文基于 Zynq7020 异构平台设计了一种稳

定、可靠的数据采集存储系统,结合 FPGA 的并

行计算优势以及处理器系统软件开发的灵活性,

在 Zynq7020 PS 端 运 行 LwIP 网 络 协 议 栈 实 现

TCP 协议,通过以太网实现主动声呐与上位机的

数据交互。同时使用自定义的应用层帧格式,在充

分发挥 TCP 协议高可靠性优势的同时避免了数据

包粘连问题,将主动声呐系统数据的实时采集、存

储与回传,以及程序的在线更新功能融合为一体,

具有可扩展性强,灵活性好,集成度高等优点。设

计的在线程序更新功能在避免对 UUV 水密结构破

坏的同时,其更新速度比 JTAG 接口更新方式具有

明显优势,大大提高了实验测试效率。

经过试验证明,本文设计的系统可长时间稳定

运行,采集存储的数据真实可用,贴近实际需求,

为项目后期的理论算法验证、方案改进以及设备调

试等工作提供了有效的数据支持。