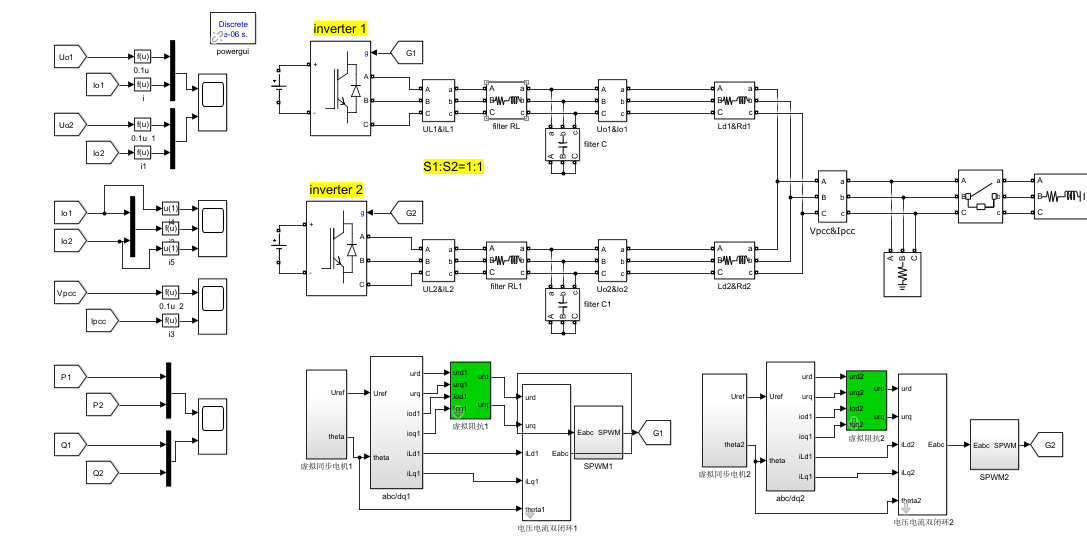

双机并联无功环流抑制虚拟阻抗VSG控制【simulink仿真模型实现】

双机并联虚拟同步发电机(VSG)系统中,因线路阻抗不匹配及参数差异,易引发无功环流。本方案在传统VSG控制基础上,引入自适应虚拟阻抗环节。其核心在于:实时检测两机间无功环流分量,据此动态调节各VSG的虚拟阻抗值,等效补偿实际线路阻抗差异,迫使两机输出电压特性趋于一致,从而实现无功功率的自主均分与环流抑制。

仿真模型核心模块简述:

-

VSG控制:

-

模拟同步发电机机电暂态特性。

-

转子运动方程:实现有功-频率(P-f)下垂及惯性响应。

-

电压调节方程:实现无功-电压(Q-V)下垂控制。

-

输出:基础参考电压指令(幅值

V_mag*,相位角θ*)。

-

-

虚拟阻抗控制(含环流抑制):

-

基础虚拟阻抗:串联于VSG输出端(常为感性),改善功率解耦与稳定性。

-

环流检测:计算两机输出电流差值,提取无功环流分量

ΔI_q。 -

自适应补偿:基于

ΔI_q生成动态虚拟阻抗补偿量ΔZ_v(如PI调节)。 -

合成与压降计算:总虚拟阻抗

Z_v = Z_{v0} + ΔZ_v;计算虚拟压降ΔV_v = Z_v * I_o。 -

输出:修正参考电压

V_ref* = V* - ΔV_v。

-

-

电压电流双闭环控制:

-

外环(电压环):跟踪修正后的

V_ref*,生成电流参考指令I_ref。 -

内环(电流环):快速跟踪

I_ref,生成逆变桥调制信号V_inv_ref。 -

输出:驱动逆变器功率器件的PWM信号。

-

-

锁相环(PLL):

-

精确跟踪公共连接点(PCC)电压相位

θ_{PCC}与频率ω_{PCC}。 -

作用:为VSG同步、坐标变换及控制环路提供相位基准。

-

仿真流程概要: PLL提供同步基准 → VSG生成基础电压指令 → 虚拟阻抗模块依据环流信息动态修正指令 → 双闭环控制精确输出该电压 → 实现并网/并联运行与无功环流抑制。仿真模型旨在验证该控制策略的有效性。

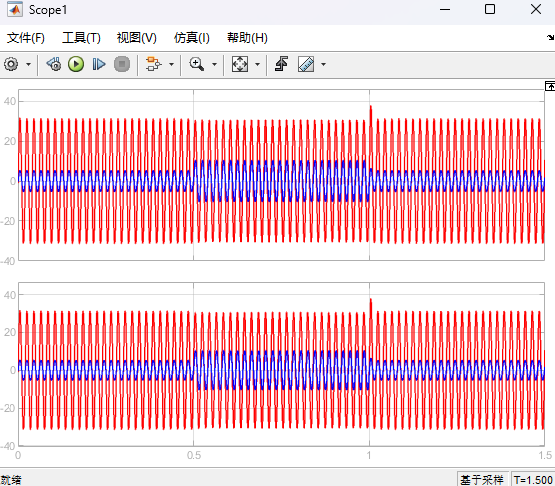

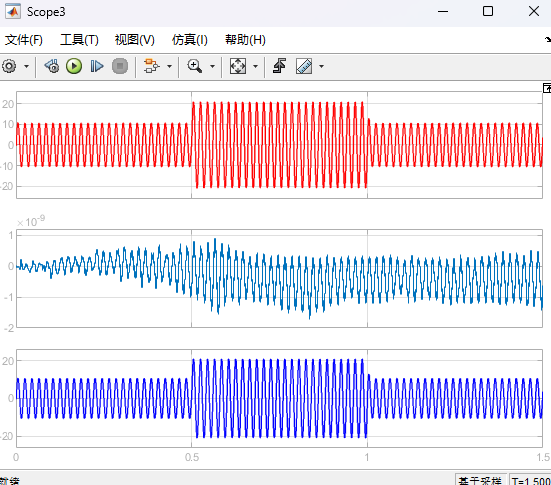

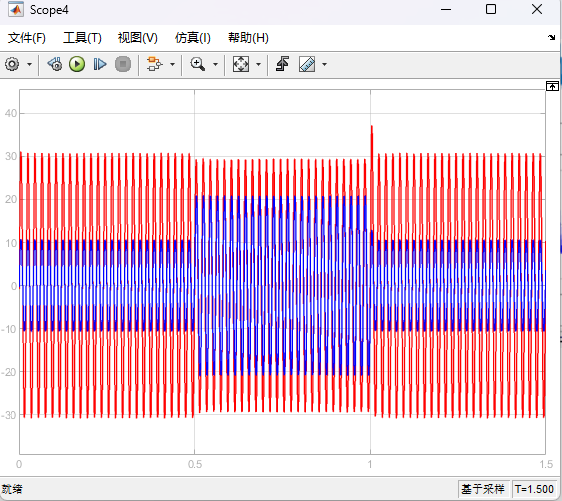

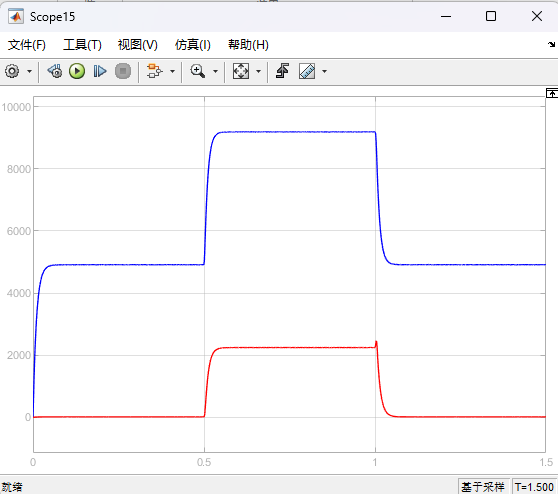

仿真结果:

仿真模型更多详情见原文:

https://mp.weixin.qq.com/s/jpb6Gax5d54IK8zJFwyFdA