Tang Prime 20K板OV5640例程

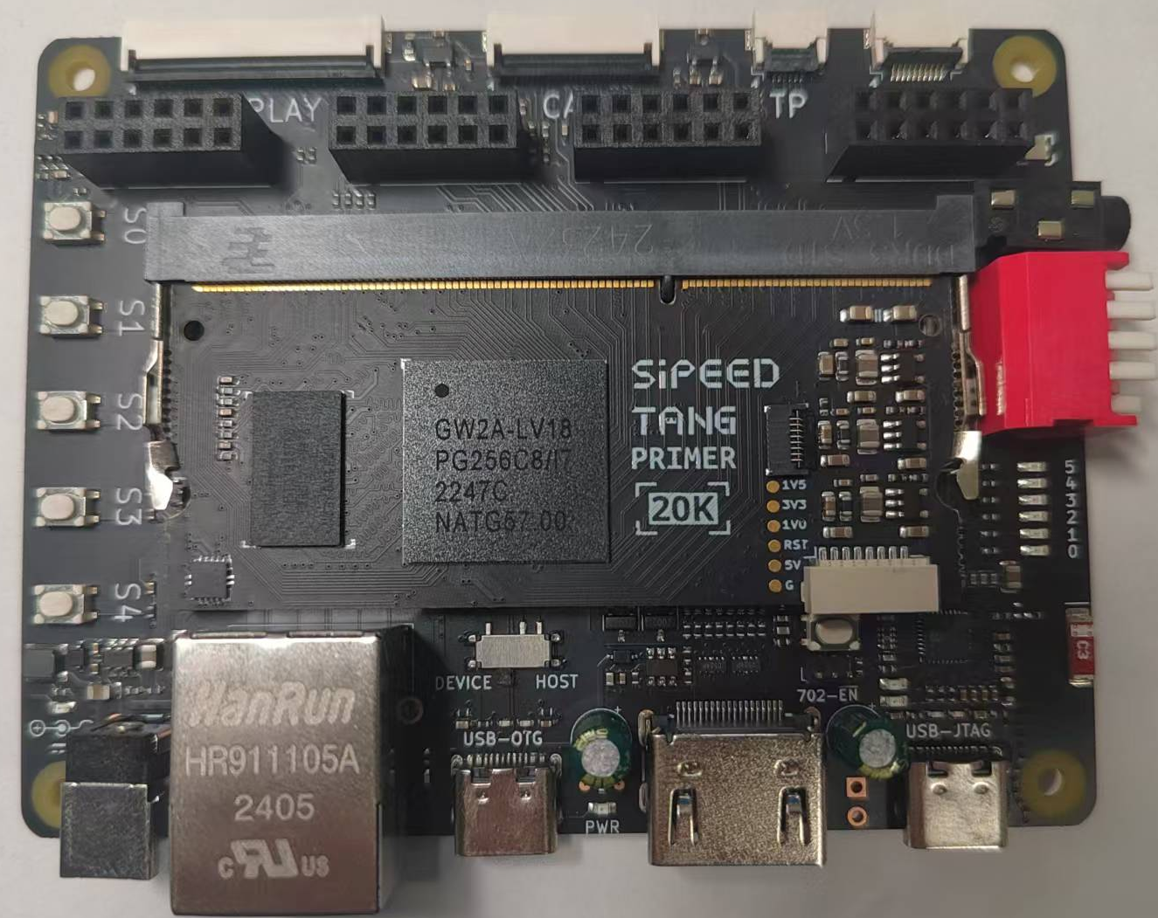

Tang Primer 20K是由开源硬件厂商SiPEED矽速科技推出,是一款以 GW2A-LV18PG256C8/I7 为主芯片的核心板,准备了 2 个扩展板,Dock 和 Lite。板卡包含有HDMI输出,DVP接口(外接OV2640/OV5640摄像头)。另外JTAG下载器已集成在板上,只需一根USB Type-C的线就可以实现下载调试,板卡供电也是依靠这条Type-C的线。板卡相关资料可参考官方网址:https://wiki.sipeed.com/hardware/en/tang/tang-primer-20k/primer-20k.html

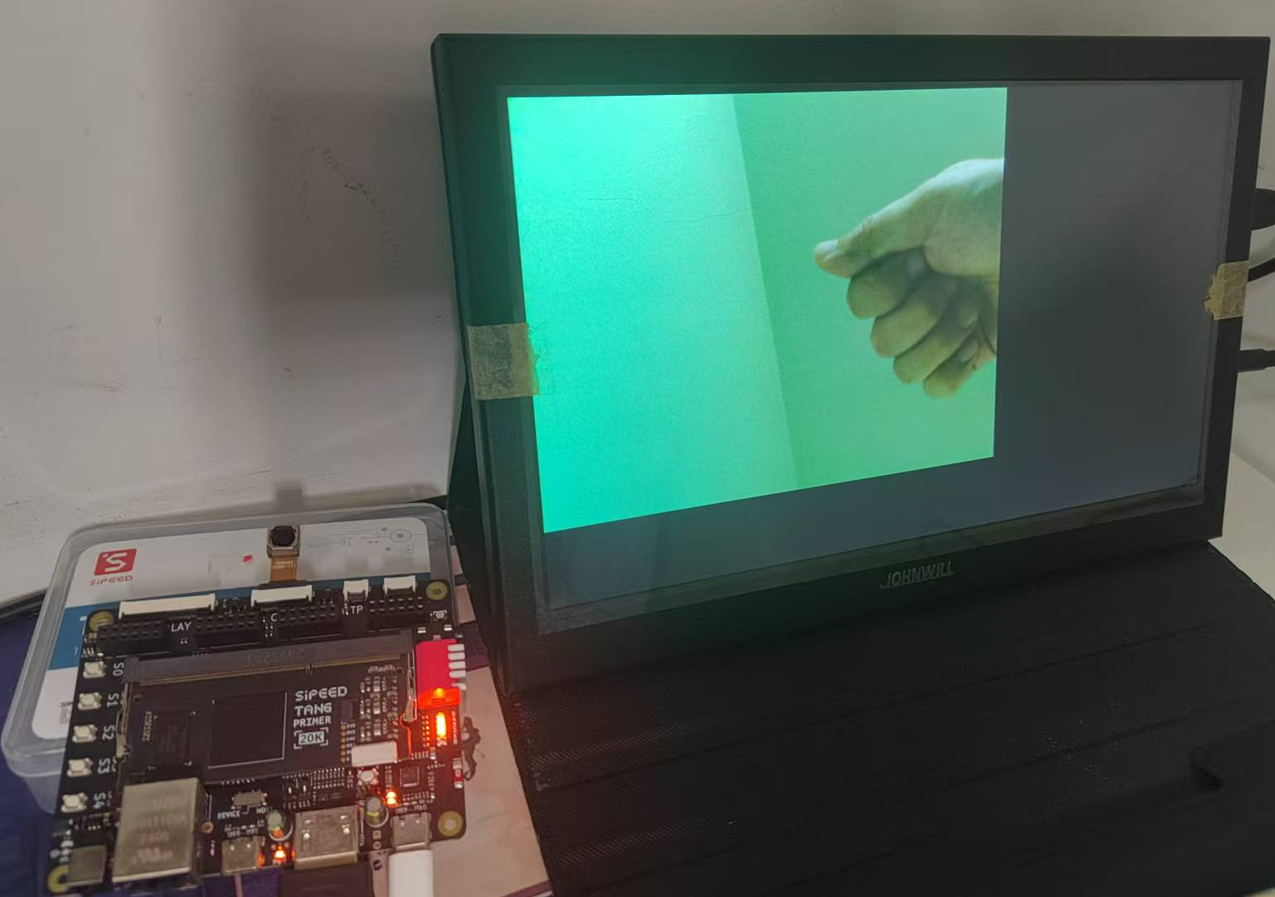

运行camera_hdmi例程

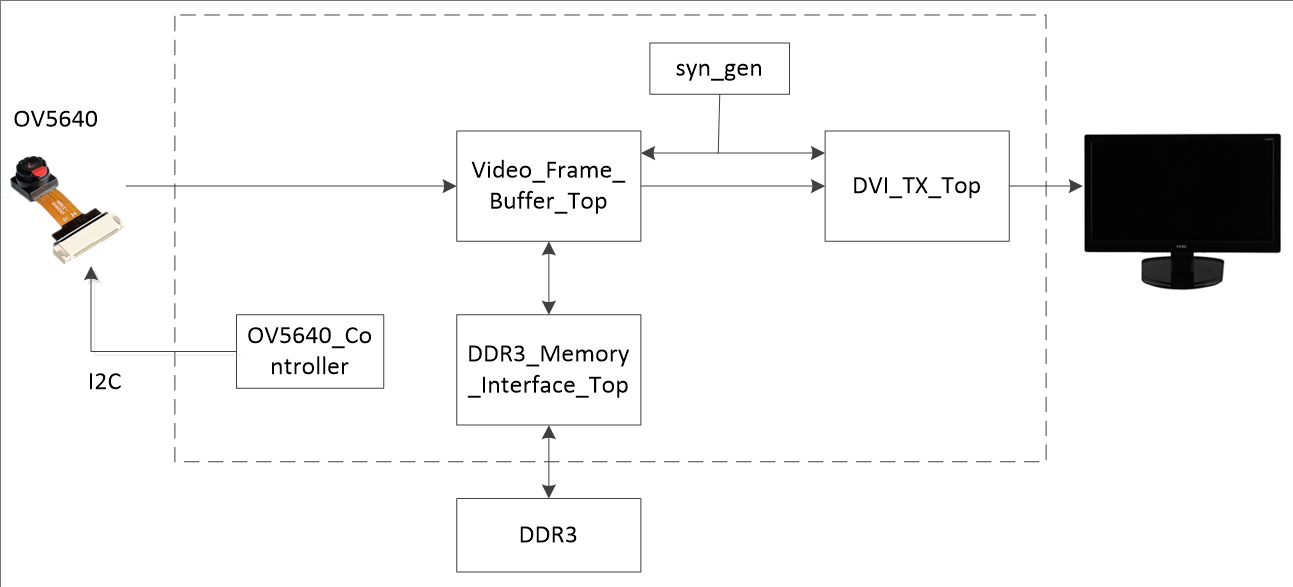

(1)程序主要结构框图

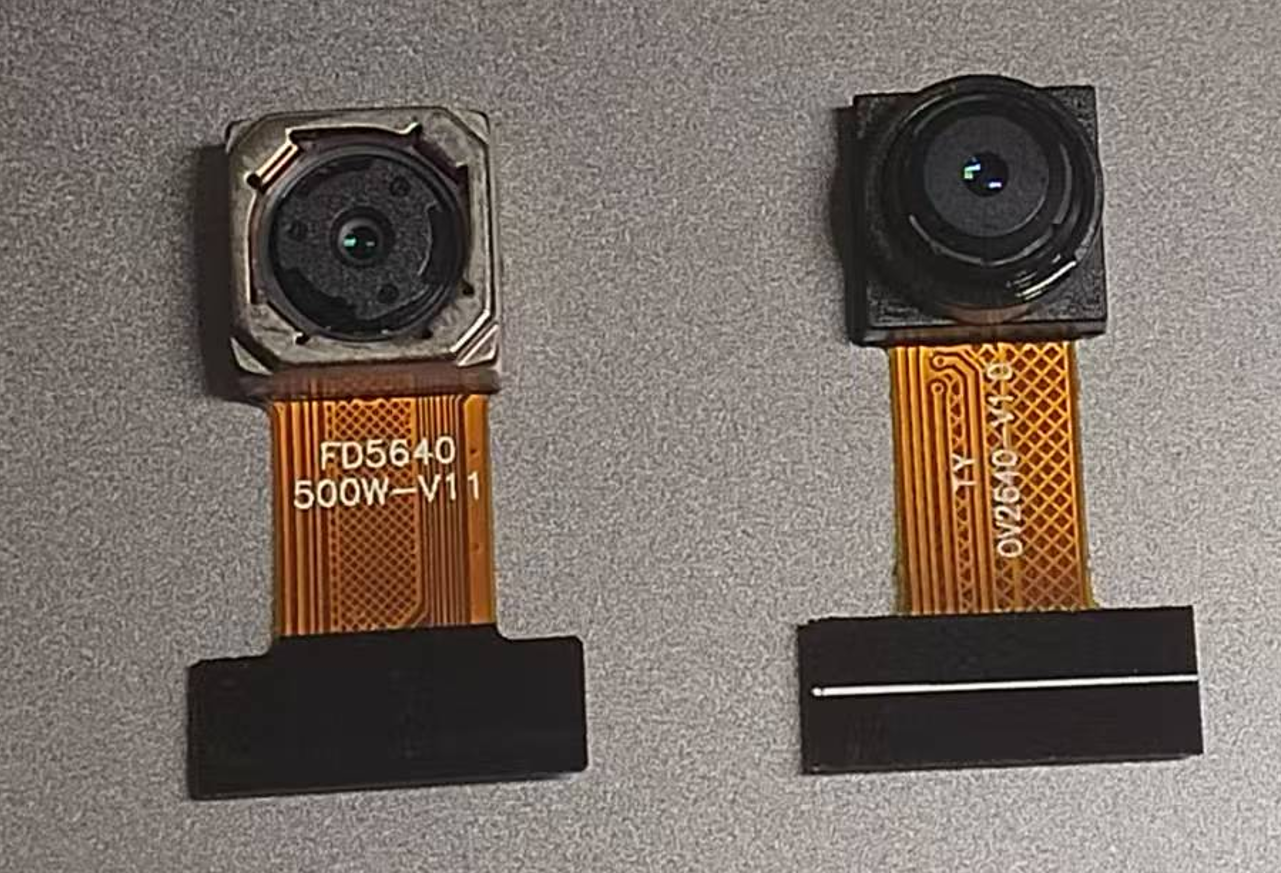

(2)OV5640摄像头和OV2640摄像头接口一样,但寄存器配置存在不同。

主要是I2c寄存器设置发生改变,OV2640的寄存器地址是8bit,OV5640的寄存器地址是16bit。

以下是OV5640的寄存器设置,RGB565输出。

module sccb_Registers #

(parameter HACT = 12'd1280,parameter VACT = 12'd720 ,parameter HTOL = 13'd1892,parameter VTOL = 13'd740

)

(input clk, input rst, input advance, output [23:0] command, output finished

);// Internal signals

reg [23:0] sreg;

reg finished_temp;

reg [9:0] address = 10'd0;// Assign values to outputs

assign command = sreg;

assign finished = finished_temp;// When register and value is FFFF

// a flag is asserted indicating the configuration is finished

always @ (sreg) beginif(sreg == 24'hFFFFFF) beginfinished_temp <= 1'b1;endelse beginfinished_temp <= 1'b0;end

end// Get value out of the LUT

always @ (posedge clk) beginif(rst == 1'b1) begin // reset the configurationaddress <= 10'd0;endelse if(advance == 1'b1) begin // Get the next valueaddress <= address+1'b1;endcase (address) 000 : sreg <= 24'h3008_02;001 : sreg <= 24'h3103_02;002 : sreg <= 24'h3017_ff;003 : sreg <= 24'h3018_ff;004 : sreg <= 24'h3037_13;005 : sreg <= 24'h3108_01;006 : sreg <= 24'h3630_36;007 : sreg <= 24'h3631_0e;008 : sreg <= 24'h3632_e2;009 : sreg <= 24'h3633_12;010 : sreg <= 24'h3621_e0;011 : sreg <= 24'h3704_a0;012 : sreg <= 24'h3703_5a;013 : sreg <= 24'h3715_78;014 : sreg <= 24'h3717_01;015 : sreg <= 24'h370b_60;016 : sreg <= 24'h3705_1a;017 : sreg <= 24'h3905_02;018 : sreg <= 24'h3906_10;019 : sreg <= 24'h3901_0a;020 : sreg <= 24'h3731_12;021 : sreg <= 24'h3600_08;022 : sreg <= 24'h3601_33;023 : sreg <= 24'h302d_60;024 : sreg <= 24'h3620_52;025 : sreg <= 24'h371b_20;026 : sreg <= 24'h471c_50;027 : sreg <= 24'h3a13_43;028 : sreg <= 24'h3a18_00;029 : sreg <= 24'h3a19_f8;030 : sreg <= 24'h3635_13;031 : sreg <= 24'h3636_03;032 : sreg <= 24'h3634_40;033 : sreg <= 24'h3622_01;034 : sreg <= 24'h3c01_34;035 : sreg <= 24'h3c04_28;036 : sreg <= 24'h3c05_98;037 : sreg <= 24'h3c06_00;038 : sreg <= 24'h3c07_07;039 : sreg <= 24'h3c08_00;040 : sreg <= 24'h3c09_1c;041 : sreg <= 24'h3c0a_9c;042 : sreg <= 24'h3c0b_40;043 : sreg <= 24'h3810_00;044 : sreg <= 24'h3811_10;045 : sreg <= 24'h3812_00;046 : sreg <= 24'h3708_64;047 : sreg <= 24'h4001_02;048 : sreg <= 24'h4005_1a;049 : sreg <= 24'h3000_00;050 : sreg <= 24'h3004_ff;051 : sreg <= 24'h4300_61;052 : sreg <= 24'h501f_01;053 : sreg <= 24'h440e_00;054 : sreg <= 24'h5000_a7;055 : sreg <= 24'h3a0f_30;056 : sreg <= 24'h3a10_28;057 : sreg <= 24'h3a1b_30;058 : sreg <= 24'h3a1e_26;059 : sreg <= 24'h3a11_60;060 : sreg <= 24'h3a1f_14;061 : sreg <= 24'h5800_23;062 : sreg <= 24'h5801_14;063 : sreg <= 24'h5802_0f;064 : sreg <= 24'h5803_0f;065 : sreg <= 24'h5804_12;066 : sreg <= 24'h5805_26;067 : sreg <= 24'h5806_0c;068 : sreg <= 24'h5807_08;069 : sreg <= 24'h5808_05;070 : sreg <= 24'h5809_05;071 : sreg <= 24'h580a_08;072 : sreg <= 24'h580b_0d;073 : sreg <= 24'h580c_08;074 : sreg <= 24'h580d_03;075 : sreg <= 24'h580e_00;076 : sreg <= 24'h580f_00;077 : sreg <= 24'h5810_03;078 : sreg <= 24'h5811_09;079 : sreg <= 24'h5812_07;080 : sreg <= 24'h5813_03;081 : sreg <= 24'h5814_00;082 : sreg <= 24'h5815_01;083 : sreg <= 24'h5816_03;084 : sreg <= 24'h5817_08;085 : sreg <= 24'h5818_0d;086 : sreg <= 24'h5819_08;087 : sreg <= 24'h581a_05;088 : sreg <= 24'h581b_06;089 : sreg <= 24'h581c_08;090 : sreg <= 24'h581d_0e;091 : sreg <= 24'h581e_29;092 : sreg <= 24'h581f_17;093 : sreg <= 24'h5820_11;094 : sreg <= 24'h5821_11;095 : sreg <= 24'h5822_15;096 : sreg <= 24'h5823_28;097 : sreg <= 24'h5824_46;098 : sreg <= 24'h5825_26;099 : sreg <= 24'h5826_08;100 : sreg <= 24'h5827_26;101 : sreg <= 24'h5828_64;102 : sreg <= 24'h5829_26;103 : sreg <= 24'h582a_24;104 : sreg <= 24'h582b_22;105 : sreg <= 24'h582c_24;106 : sreg <= 24'h582d_24;107 : sreg <= 24'h582e_06;108 : sreg <= 24'h582f_22;109 : sreg <= 24'h5830_40;110 : sreg <= 24'h5831_42;111 : sreg <= 24'h5832_24;112 : sreg <= 24'h5833_26;113 : sreg <= 24'h5834_24;114 : sreg <= 24'h5835_22;115 : sreg <= 24'h5836_22;116 : sreg <= 24'h5837_26;117 : sreg <= 24'h5838_44;118 : sreg <= 24'h5839_24;119 : sreg <= 24'h583a_26;120 : sreg <= 24'h583b_28;121 : sreg <= 24'h583c_42;122 : sreg <= 24'h583d_ce;123 : sreg <= 24'h5180_ff;124 : sreg <= 24'h5181_f2;125 : sreg <= 24'h5182_00;126 : sreg <= 24'h5183_14;127 : sreg <= 24'h5184_25;128 : sreg <= 24'h5185_24;129 : sreg <= 24'h5186_09;130 : sreg <= 24'h5187_09;131 : sreg <= 24'h5188_09;132 : sreg <= 24'h5189_75;133 : sreg <= 24'h518a_54;134 : sreg <= 24'h518b_e0;135 : sreg <= 24'h518c_b2;136 : sreg <= 24'h518d_42;137 : sreg <= 24'h518e_3d;138 : sreg <= 24'h518f_56;139 : sreg <= 24'h5190_46;140 : sreg <= 24'h5191_f8;141 : sreg <= 24'h5192_04;142 : sreg <= 24'h5193_70;143 : sreg <= 24'h5194_f0;144 : sreg <= 24'h5195_f0;145 : sreg <= 24'h5196_03;146 : sreg <= 24'h5197_01;147 : sreg <= 24'h5198_04;148 : sreg <= 24'h5199_12;149 : sreg <= 24'h519a_04;150 : sreg <= 24'h519b_00;151 : sreg <= 24'h519c_06;152 : sreg <= 24'h519d_82;153 : sreg <= 24'h519e_38;154 : sreg <= 24'h5480_01;155 : sreg <= 24'h5481_08;156 : sreg <= 24'h5482_14;157 : sreg <= 24'h5483_28;158 : sreg <= 24'h5484_51;159 : sreg <= 24'h5485_65;160 : sreg <= 24'h5486_71;161 : sreg <= 24'h5487_7d;162 : sreg <= 24'h5488_87;163 : sreg <= 24'h5489_91;164 : sreg <= 24'h548a_9a;165 : sreg <= 24'h548b_aa;166 : sreg <= 24'h548c_b8;167 : sreg <= 24'h548d_cd;168 : sreg <= 24'h548e_dd;169 : sreg <= 24'h548f_ea;170 : sreg <= 24'h5490_1d;171 : sreg <= 24'h5381_1e;172 : sreg <= 24'h5382_5b;173 : sreg <= 24'h5383_08;174 : sreg <= 24'h5384_0a;175 : sreg <= 24'h5385_7e;176 : sreg <= 24'h5386_88;177 : sreg <= 24'h5387_7c;178 : sreg <= 24'h5388_6c;179 : sreg <= 24'h5389_10;180 : sreg <= 24'h538a_01;181 : sreg <= 24'h538b_98;182 : sreg <= 24'h5580_06;183 : sreg <= 24'h5583_40;184 : sreg <= 24'h5584_10;185 : sreg <= 24'h5589_10;186 : sreg <= 24'h558a_00;187 : sreg <= 24'h558b_f8;188 : sreg <= 24'h501d_40;189 : sreg <= 24'h5300_08;190 : sreg <= 24'h5301_30;191 : sreg <= 24'h5302_10;192 : sreg <= 24'h5303_00;193 : sreg <= 24'h5304_08;194 : sreg <= 24'h5305_30;195 : sreg <= 24'h5306_08;196 : sreg <= 24'h5307_16;197 : sreg <= 24'h5309_08;198 : sreg <= 24'h530a_30;199 : sreg <= 24'h530b_04;200 : sreg <= 24'h530c_06;201 : sreg <= 24'h5025_00;202 : sreg <= 24'h3035_11; //系统时钟分频 //41:15fps, 21:30Fps, 11:60Fps203 : sreg <= 24'h3036_69; //PLL倍频 , 4:3 use 69 , else 72204 : sreg <= 24'h3c07_08;205 : sreg <= 24'h3820_41; //Sensor vflip, 47=N, 41=T, 上下翻转206 : sreg <= 24'h3821_01; //Sensor mirror, 01=N, 07=T, 左右翻转207 : sreg <= 24'h3814_31; // timing X inc208 : sreg <= 24'h3815_31; // timing Y inc209 : sreg <= 24'h3800_00; //TIMING HS start210 : sreg <= 24'h3801_00;211 : sreg <= 24'h3802_00;212 : sreg <= 24'h3803_fa; //4:3 use 04 , else fa213 : sreg <= 24'h3804_0a;214 : sreg <= 24'h3805_3f;215 : sreg <= 24'h3806_06; //4:3 use 07 , else 06216 : sreg <= 24'h3807_a9; //4:3 use 9b , else a9217 : sreg <= {16'h3808, 4'd0, HACT[11:8]}; //DVP 输出水平像素点数高4位218 : sreg <= {16'h3809, HACT[7:0]}; //DVP 输出水平像素点数低8位219 : sreg <= {16'h380a, 4'd0, VACT[11:8]}; //DVP 输出垂直像素点数高3位220 : sreg <= {16'h380b, VACT[7:0]}; //DVP 输出垂直像素点数低8位221 : sreg <= {16'h380c, 3'd0, HTOL[12:8]}; //水平总像素大小高5位222 : sreg <= {16'h380d, HTOL[7:0]}; //水平总像素大小低8位223 : sreg <= {16'h380e, 3'd0, VTOL[12:8]}; //垂直总像素大小高5位224 : sreg <= {16'h380f, VTOL[7:0]}; //垂直总像素大小低8位225 : sreg <= 24'h3813_04; //4:3 use 06 , else 04226 : sreg <= 24'h3618_00;227 : sreg <= 24'h3612_29;228 : sreg <= 24'h3709_52;229 : sreg <= 24'h370c_03;230 : sreg <= 24'h3a02_17;231 : sreg <= 24'h3a03_10;232 : sreg <= 24'h3a14_17;233 : sreg <= 24'h3a15_10;234 : sreg <= 24'h4004_02;235 : sreg <= 24'h4713_03; 236 : sreg <= 24'h4407_04;237 : sreg <= 24'h460c_20;238 : sreg <= 24'h4837_22;239 : sreg <= 24'h3824_02;240 : sreg <= 24'h5001_83;//4:3 use a3 , else 83241 : sreg <= 24'h3b07_0a;242 : sreg <= 24'h503d_00; //彩条测试使能 //0x00:正常模式 0x80:彩条显示243 : sreg <= 24'h3016_00; //闪光灯禁用 //Disable244 : sreg <= 24'h301c_00;245 : sreg <= 24'h3019_00;//关闭闪光灯246 : sreg <= 24'h3031_08;//Bypass regulator247 : sreg <= 24'h302c_C2;//output drive 4x248 : sreg <= 24'hffff_ff;default : sreg <= 24'hFFFF_FF; // End configurationendcase

end endmodule