uvm tlm preface

Transaction Level Modeling是一种用于构建组件和系统高度抽象模型的建模风格。在该方案中,数据被表示为事务(包含随机、协议特定信息的类对象),通过称为TLM接口的特殊端口在不同组件之间流动。这带来了更高层次的抽象,由于现代验证环境中存在大量与不同协议相关的信号,这种抽象变得极为必要。若能将信号中的数据及其变化表示为事务(如写操作/读操作),将大幅简化理解、调试和验证的复杂度。

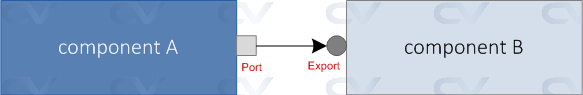

UVM提供了一套事务级通信接口,可用于组件间的互联,从而实现数据包在组件间的传输。这种设置的优点在于它能将组件与其他组件的变化隔离开来,同时提升可重用性和灵活性——因为现在您只需将某个组件替换为另一个同样具有TLM接口的组件即可。

class simple_packet extends uvm_object;`uvm_object_utils (simple_packet)rand bit [7:0] addr;rand bit [7:0] data;bit rwb;constraint c_addr { addr > 8'h2a; };constraint c_data { data inside {[8'h14:8'he9]};endclasssimple_packet 类对象将作为一笔事务,通过 TLM 接口端口 port 和 export 从 componentA 传输至 componentB。