PMIC电源噪声对SOC芯片电源完整性的影响

PMU是电源管理单元,负责给SOC供电,调节电压和电流,确保各个模块正常工作。而电源完整性是确保电源分配网络(PDN)能够提供稳定、干净的电压和电流,避免噪声干扰SOC的正常运行。

那电源噪声具体指的是什么呢?可能包括电压波动、高频噪声、地弹等等。这些噪声来源可能来自PMU本身的开关噪声,比如DC-DC转换器的开关操作,或者是其他外部因素,比如负载瞬态变化、PCB布局问题等等。

接下来,需要考虑PMU的电源噪声如何传递到SOC。PMU通常通过电源轨给SOC供电,如果PMU输出的电压有噪声,这些噪声会通过电源网络传递到SOC的各个部分。SOC内部可能有多个电源域,不同的模块对电源噪声的敏感度不同。比如,数字电路可能对高频噪声有一定的容忍度,但模拟电路比如ADC、PLL等对噪声非常敏感,容易受到干扰。

电源完整性受到影响的话,可能导致SOC出现各种问题,比如时序错误、信号完整性下降、误码率增加,甚至系统崩溃。所以,PMU的噪声控制对SOC的稳定运行至关重要。

接下来分析影响的具体机制。比如,PMU的开关频率和SOC的敏感频段是否有重叠,如果PMU的开关噪声频率接近SOC内部某些电路的工作频率,可能会引起共振,放大噪声影响。另外,电源分配网络的阻抗特性也很重要,如果PDN在高频下阻抗过高,那么噪声电压会更大,导致SOC供电电压不稳定。

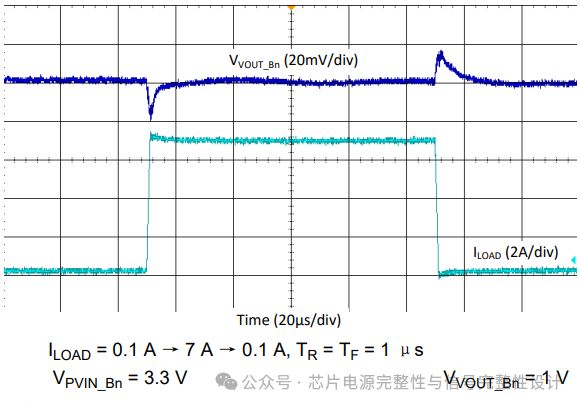

还要考虑PMU负载瞬态响应。当SOC的负载突然变化时,比如从低功耗模式切换到高性能模式,PMU需要快速调整输出电压以维持稳定。如果PMU的响应速度不够快,或者瞬态响应过程中产生过冲或下冲,这会导致电压波动,影响SOC的电源完整性。

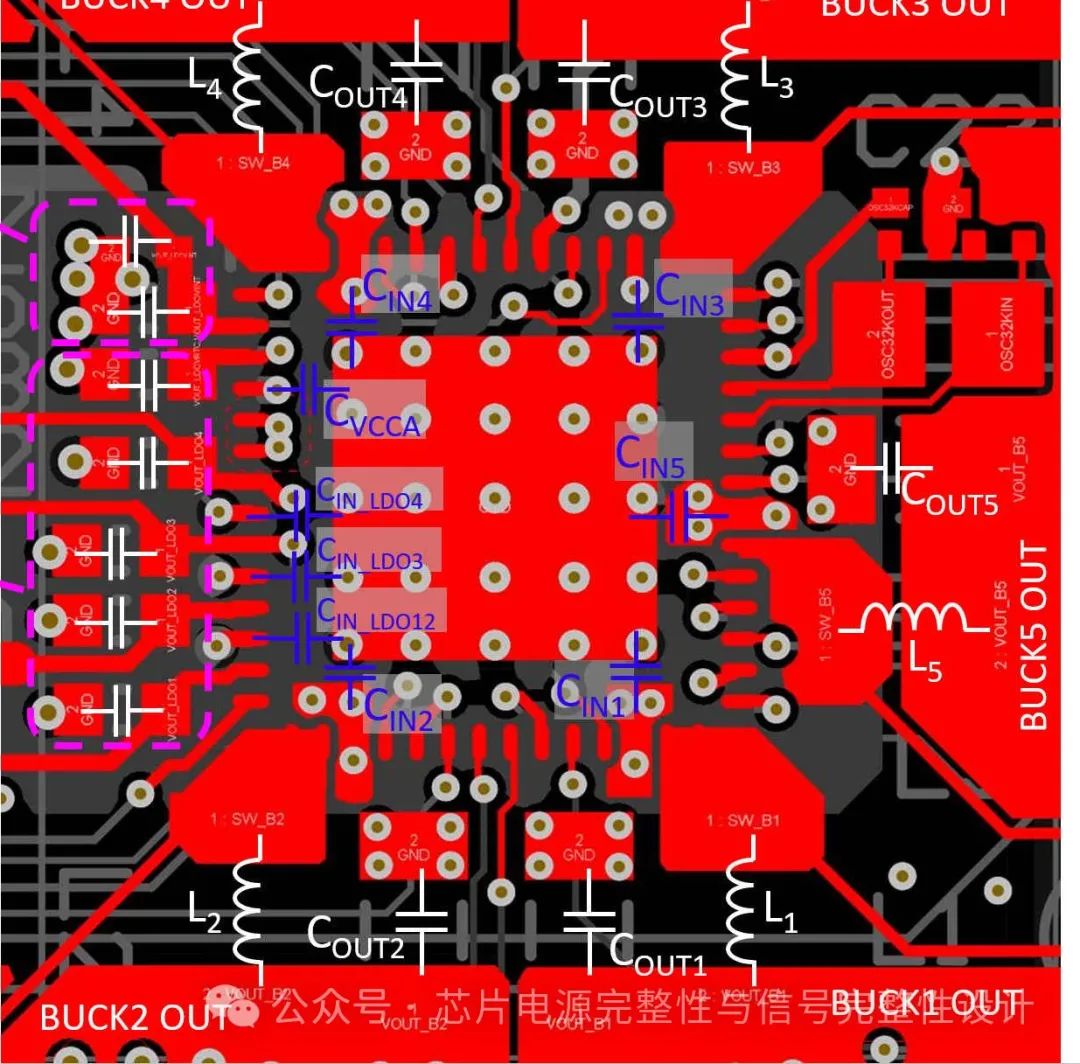

此外,PCB布局和封装设计也会影响噪声传递。比如,PMU和SOC之间的电源路径是否足够短,是否有足够的去耦电容,地平面设计是否良好,这些都可能影响噪声的传播和抑制。

可能的解决方案包括优化PMU的设计,比如使用更高效的DC-DC转换器拓扑结构,增加滤波电容,改善反馈控制环路以提升瞬态响应。另外,在SOC端,可能需要设计更鲁棒的电源分配网络,合理布置去耦电容,使用电源隔离技术,以及进行充分的电源完整性仿真和测试。

同时还要关注一些芯片细节,比如不同工艺节点下SOC对电源噪声的敏感度是否有差异,或者PMU与SOC之间的协同设计策略,比如动态电压频率调整(DVFS)如何影响电源噪声和完整性。另外,热效应也可能影响电源噪声,温度变化可能导致PMU的性能漂移,进而影响输出电压的稳定性。

还需要考虑测试和测量的方法,如何在实际系统中准确测量PMU输出的噪声,以及如何评估这些噪声对SOC的影响。可能需要使用示波器、频谱分析仪等工具,进行时域和频域的分析。

下面将从噪声的产生机制、传播路径、对SOC的影响、设计优化方法等方面进行全面分析,确保覆盖关键点,并给出有效的解决方案。

PMU(电源管理单元)芯片的电源噪声对SoC(系统级芯片)电源完整性(PI)的影响涉及多个层面,需要从噪声产生机制、传播路径、SoC敏感度以及缓解策略等方面进行系统分析。以下为深入探讨:

1. PMU电源噪声的产生机制及来源

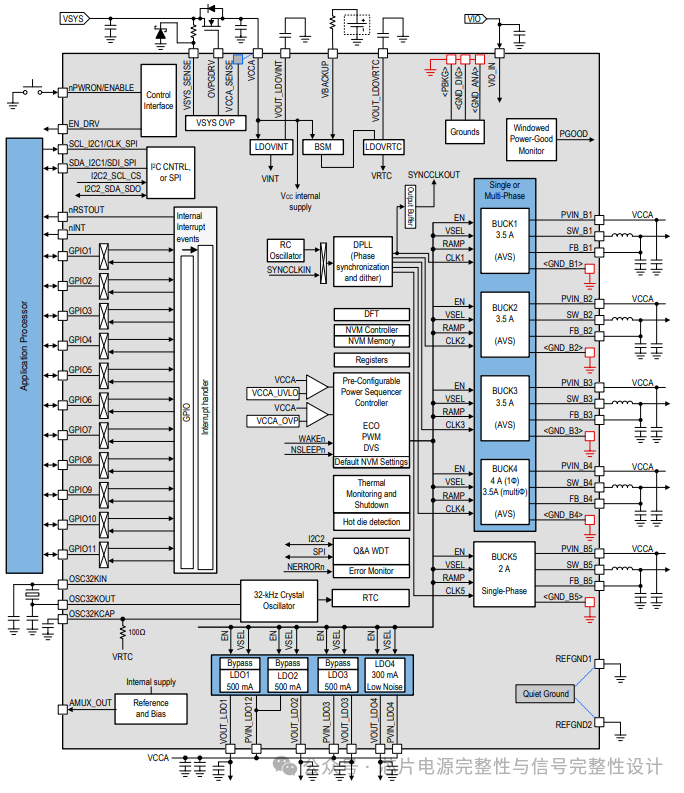

PMU内部关键模块(如DC-DC转换器、LDO等)是主要噪声源:

· 开关噪声:Buck/Boost转换器的开关动作导致高频纹波(数百kHz至MHz),其幅值与开关频率、电感/电容参数及负载电流相关。

· 地弹与串扰:快速切换电流(di/dt)引发地弹噪声,通过共模路径耦合至SoC电源网络。

· 负载瞬态响应:SoC动态负载变化(如CPU突发运算)导致PMU输出电压瞬时跌落(Undershoot)或过冲(Overshoot),瞬态恢复时间不足会加剧噪声。

· 热噪声与器件非线性:PMU内部MOSFET导通电阻、电感磁芯损耗等产生的热噪声,以及非线性元件导致的谐波失真。

2. 电源噪声对SoC电源完整性的影响

2.1 直接效应

· 电压域稳定性:PMU输出噪声直接叠加在SoC电源轨上,若超出容忍范围(如±3%额定电压),可能导致逻辑错误或功能失效。

· 时序违例:电源噪声导致时钟抖动(Jitter)和逻辑门延时变化,在高频设计中可能违反建立/保持时间(Setup/Hold Time)。

· 模拟电路性能劣化:PLL、ADC/DAC等模块对电源敏感,噪声可能引起相位噪声增加、信噪比(SNR)下降。

2.2 间接效应

· 信号完整性(SI)耦合:电源噪声通过PDN阻抗耦合至信号线,导致串扰和误码率(BER)上升,电源引入的信号抖动增加,影响高速信号timing margin,导致接口ac timing违例,特别是存储类高速接口速率越高对电源质量的需求越严格。

· 电磁干扰(EMI):高频噪声通过辐射或传导途径干扰周边电路,可能引发系统级EMC问题。

3. 噪声传播路径与PDN阻抗分析

3.1 传输路径

· 传导路径:PMU输出至SoC的电源网络(PCB走线、封装互连、片上金属层)构成主要传导路径,其阻抗特性(Z(f))决定噪声衰减程度。

· 辐射路径:高频噪声通过空间耦合至邻近敏感电路,需关注PCB布局与屏蔽设计。

3.2 PDN阻抗关键频段

· 低频段(<1MHz):由去耦电容和PCB平面电容主导,需确保足够容值以抑制低频纹波。

· 中频段(1MHz~100MHz):封装和片上电容起主要作用,需优化电容分布与ESL(等效串联电感)。

· 高频段(>100MHz):片上电容与金属层RC网络主导,需通过片上纳米级电容(如MOS电容)降低阻抗。

4. 设计优化与噪声抑制策略

4.1 PMU端优化

· 拓扑选择:采用多相Buck转换器分散开关噪声频谱,或使用LDO为噪声敏感模块供电。

· 动态响应增强:优化补偿网络(如Type III补偿器)以提升负载瞬态响应速度,减少电压跌落。

· 同步整流与软开关技术:降低开关损耗和di/dt噪声。

· 选择合理的低频瞬态LC组合:降低瞬态开关噪声。

4.2 PDN设计

· 阻抗设计:通过频域仿真(如ANSYS SIwave)优化PDN阻抗曲线,确保目标频段内Z(f)低于目标阻抗(Ztarget)。

· 去耦策略:混合使用大容量电解电容(低频)、陶瓷电容(中频)和嵌入式电容(高频),设计的电容组合需要覆盖住全频段范围,物理设计也要保障能缩短电流回路。

4.3 SoC端加固

· 电源域隔离:数字与模拟电源域独立供电,芯片内部采用深阱隔离或Guard Ring减少耦合;外部数字、模拟电源采用各自的数字地或者模拟地进行隔离,减少相互干扰。如果数字模拟合并也要保证各自的总噪声都能满足各自的电源噪声需求。

· 自适应电压调节(AVS):根据工作负载动态调整电压,降低静态噪声裕量需求。

4.4 系统级协同设计

· 时序分析与协同仿真:结合电源噪声模型与时序分析工具(如PrimeTime),评估噪声对时序的边际影响。

· EMI/EMC设计:优化PCB叠层、电源分割与滤波电路,抑制共模噪声辐射。

5. 未来挑战与趋势理解

· 先进工艺节点:3nm以下工艺的薄氧化层对电压波动更敏感,需更严格的噪声容限设计。

· Chiplet技术:多芯片集成下PMU与SoC的跨封装噪声耦合机制复杂化,需3D PDN协同优化。

· AI驱动设计:利用机器学习算法快速迭代PDN参数,实现噪声与能效的Pareto最优。

PMU电源噪声对SoC电源完整性的影响贯穿从芯片设计到系统集成的全流程。需通过多物理场协同仿真、PDN阻抗优化及系统级噪声抑制技术,在能效与稳定性间取得平衡。未来,随着工艺演进与应用场景复杂化,跨层级协同设计与智能化优化工具将成为关键突破口。