【zynq7020】PL的“Hello LED”

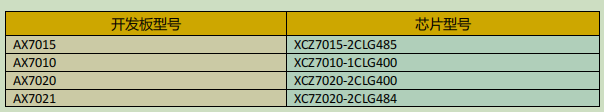

AX7020------xc7z020clg400-2

“-2”表示速率等级,数字越大,性能越好,速率高的芯片向下兼容速率低的芯片

通过一个 LED 例程来熟悉 PL(FPGA)的开发流程,熟悉 Vivado 软件的基本操作,这个开发流程和不带 ARM 的 FPGA 芯片完全一致

在本例程中,我们要做的是 LED 灯控制实验,每秒钟控制开发板上的 LED 灯翻转一次,实现亮、灭、亮、灭的控制

创建Vivado工程(这里和FPGA开发流程一致,简单描述)

1.Create New Project

2.Next

3.在弹出的对话框中输入工程名和工程存放的目录,我们这里取一个 led 的工程名。需要注意工程路径“Project location”不能有中文、空格,路径名称也不能太长

4.在工程类型中选择“RTL Project”

5.目标语言“Target language”选择“Verilog”,虽然选择 Verilog,但 VHDL 也可以使用,支持

多语言混合编程。

6.点击“Next”,不添加任何文件

7.在“Default Part”选项中,器件家族“Family”选择“Zynq-7000”,封装类型“Package”选择“clg400”,减少我们选择范围。AC7010 在下拉列表中选择“xc7z010clg400-1”,AC7020在下拉列表中选择“xc7z020clg400-2”(知道芯片型号直接在Search框搜索即可)

8.点击“Finish”就可以完成以后名为“led”工程的创建。

Verilog代码

点击 Project Manager 下的 Add Sources 图标(或者使用快捷键 Alt+A)

选择添加或创建设计源文件“Add or create design sources”,点击“Next”

选择创建文件“Create File

文件名“File name”设置为“led”,点击“OK

点击“Finish”,完成“led.v”文件添加

在弹出的模块定义“Define Module”,中可以指定“led.v”文件的模块名称“Module name”, 这里默认不变为“led”,还可以指定一些端口,这里暂时不指定,点击“OK”。

在弹出的对话框中选择“Yes”

双击“led.v”可以打开文件,然后编辑

编写“led.v”,这里定义了一个 32 位的寄存器 timer, 用于循环计数 0~49999999(1 秒钟), 计数到 49999999(1 秒)的时候, 寄存器 timer 变为 0,并翻转四个 LED。这样原来 LED 是灭的话,就会点亮,如果原来 LED 为亮的话,就会熄灭。编写好后的代码如下:

led.v

'timescale 1ns/1ps

module led(input sys_clk,output reg led);reg[31:0] timer_cnt;always@(posedge sys_clk)beginif(timer_cnt>=32'd49_999_999)beginled<=~led;timer_cnt<=32'd0;endelsebeginled<=led;timer_cnt<=timer_cnt+32'd1;endend

endmodule编写好代码后保存,点击菜单“File -> Save All Files"(直接点保存按钮)

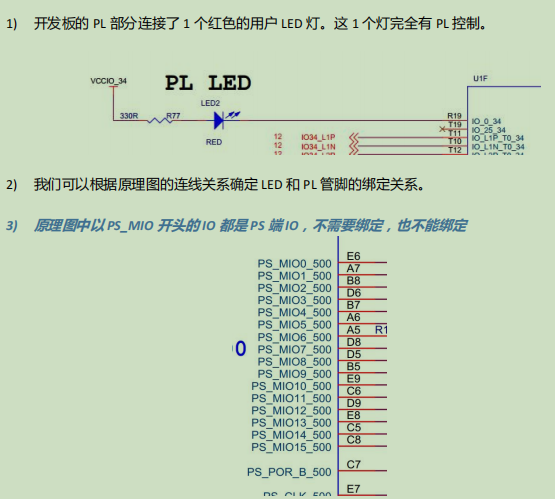

添加管脚约束

Vivado 使用的约束文件格式为 xdc 文件,xdc 文件里主要是完成管脚的约束,时钟的约束, 以

及组的约束。这里我们需要对 led.v 程序中的输入输出端口分配到 FPGA 的真实管脚上。

直接添加xdc文件

led.xdc

set_property IOSTANDARD LVCMOS33 [get_ports sys_clk]

set_property PACKAGE_PIN U18 [get_ports sys_clk]set_property IOSTANDARD LVCMOS33 [get_ports led]

set_property PACKAGE_PIN R19 [get_ports led]按照引导添加

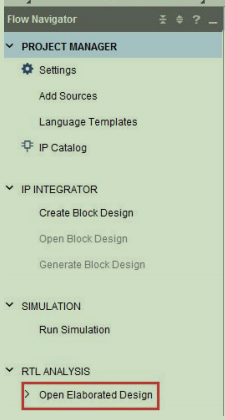

点击“Open Elaborated Design”

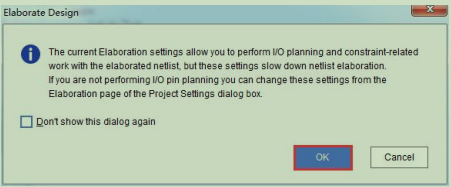

在弹出的窗口中点击“OK”按钮

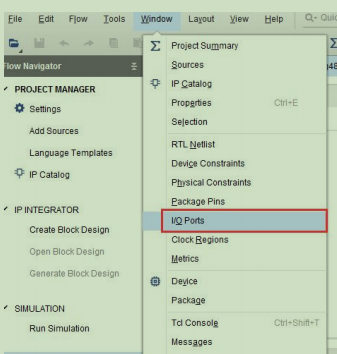

在菜单中选择“Window -> I/O Ports”

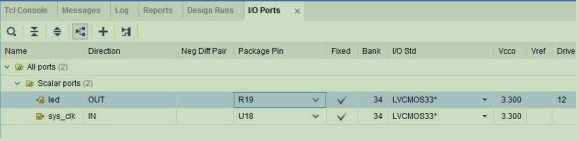

在弹出的 I/O Ports 中可以看到管脚分配情况

给 LED 和时钟分配管脚、电平标准,完成后点击保存图标

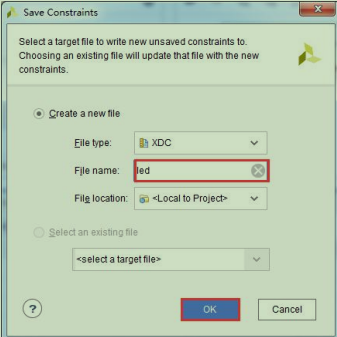

弹出窗口,要求保存约束文件,文件名我们填写“led”,文件类型默认“XDC”,点击“OK”

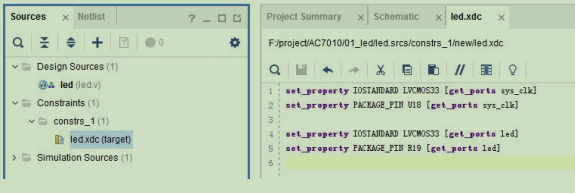

打开刚才生成的“led.xdc”文件,我们可以看到是一个 TCL 脚本,如果我们了解这些语法,

完全可以通过自己编写 led.xdc 文件的方式来约束管脚

总结

最基本的 XDC 编写的语法,普通 IO 口只需约束引脚号和电压,管脚约束如

set_property PACKAGE_PIN "引脚编号" [get_ports “端口名称”]

电平信号的约束如下:

set_property IOSTANDARD "电平标准" [get_ports “端口名称”]

这里需要注意文字的大小写,端口名称是数组的话用{ }刮起来,端口名称必须和源代码中的名字一致,且端口名字不能和关键字一样。

电平标准中“LVCMOS33”后面的数字指 FPGA 的 BANK 电压,LED 所在 BANK 电压为 3.3 伏,

所以电平标准为“LVCMOS33”。Vivado 默认要求为所有 IO 分配正确的电平标准和管脚编号

添加时序约束

一个 FPGA 设计除了管脚分配以外,还有一个重要的约束,那就是时序约束,这里通过向导方式演示如果进行一个时序约束

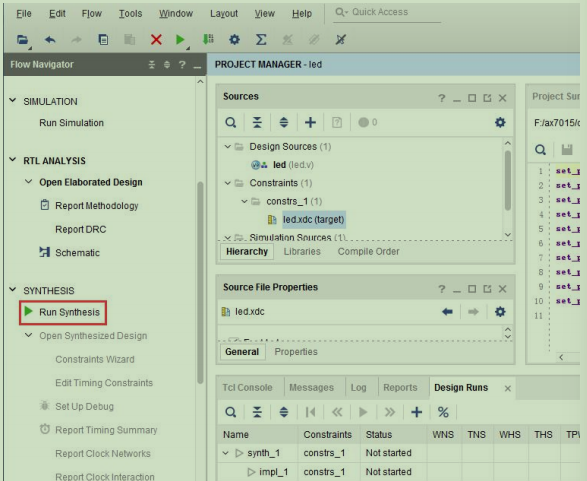

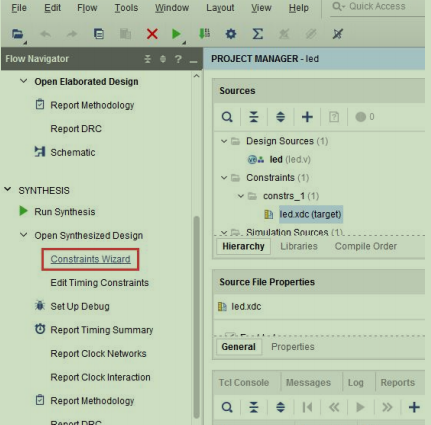

点击“Run Synthesis”开始综合

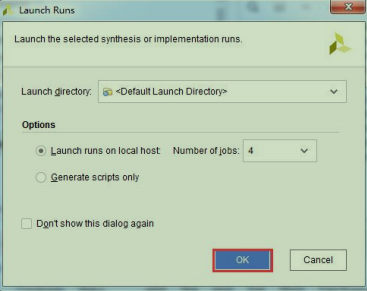

弹出对话框点击“OK”

综合完成以后点击“Cancel”

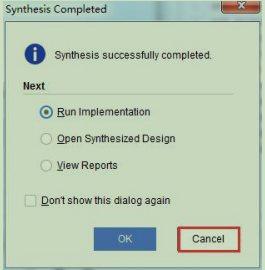

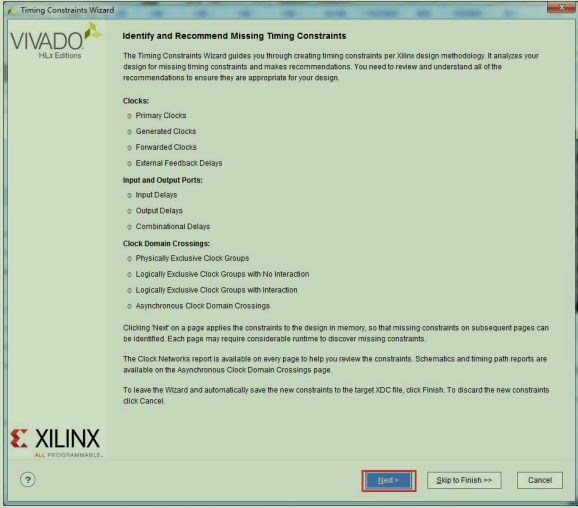

点击“Constraints Wizard

在弹出的窗口中点击“Next”

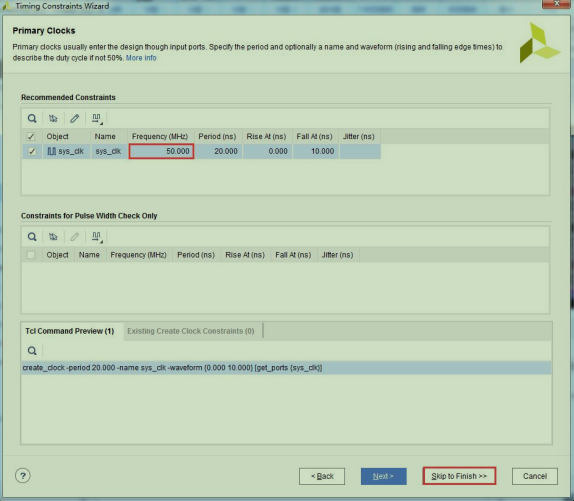

时序约束向导分析出设计中的时钟,这里把“sys_clk”频率设置为 50Mhz,然后点击“Skip to Finish”结束时序约束向导。

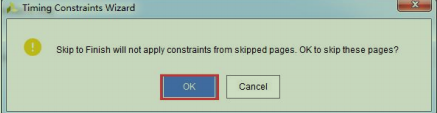

弹出的窗口中点击“OK”

点击“Finish”

这个时候 led.xdc 文件已经更新,重新加载文件即可

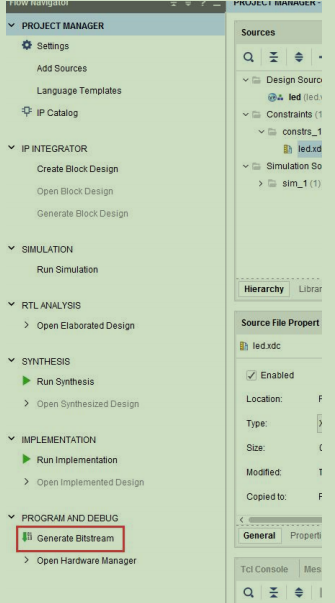

生成bit文件

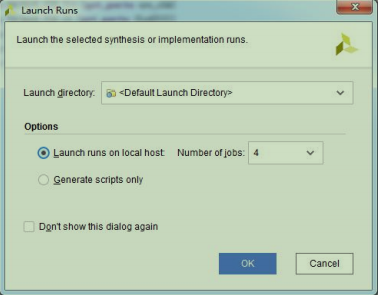

编译的过程可以细分为综合、布局布线、生成 bit 文件等,这里我们直接点击“Generate

Bitstream”,直接生成 bit 文件

在弹出的对话框中可以选择任务数量,这里和 CPU 核心数有关,一般数字越大,编译越快,

点击“OK”

这个时候开始编译,可以看到右上角有个状态信息,在编译过程中可能会被杀毒软件、电

脑管家拦截运行,导致无法编译或很长时间没有编译成功。

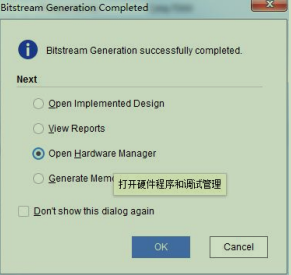

编译中没有任何错误,编译完成,弹出一个对话框让我们选择后续操作,这里选项“Open

Hardware Manger”,点击“OK”,当然,也可以选择“Cancel”,然后在左边导航栏选择“Open

Hardware Manger

下载调试

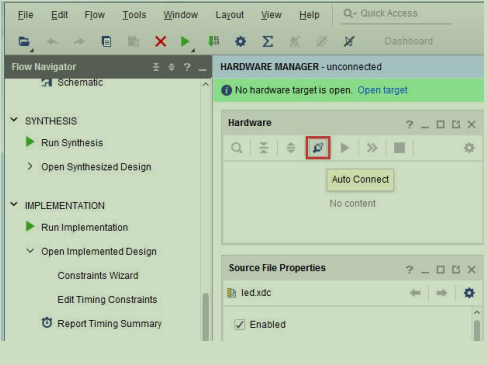

连接好开发板的 JTAG 接口,给开发板上电

在“HARDWARE MANAGER”界面点击“Auto Connect”,自动连接设备

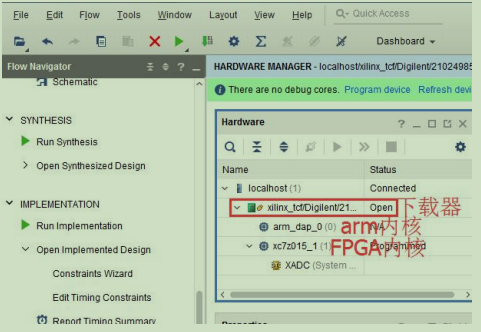

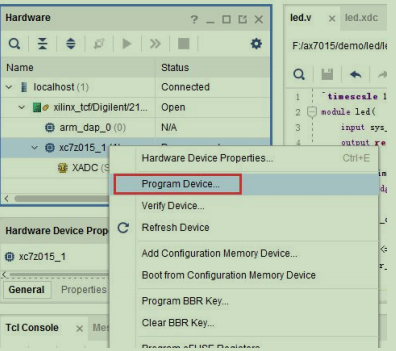

可以看到 JTAG 扫描到 arm 和 FPGA 内核(图中为 xc7z015,AC7010 开发板实际为xc7z010_1, AC7020 开发板实际为 xc7z020_1),还有一个 XADC,可以检测系统电压、温度

选择 xc7z010_1 或 xc7z020_1,右键“Program Device...”

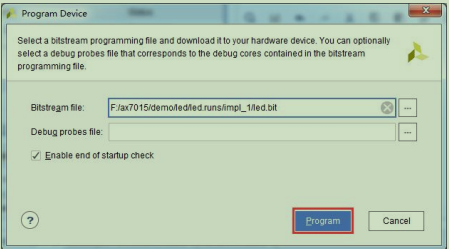

在弹出窗口中点击“Program”

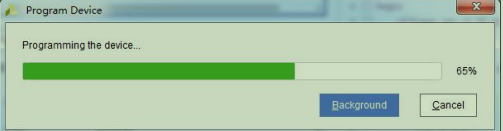

等待下载

如果把程序烧录到 Flash,需要 PS 系统的配合才能完成,只有 PL的工程不能直接烧写 Flash

ZYNQ笔记(0):C语言基础知识复习 - 咸鱼IC - 博客园

ZYNQ笔记(1):PL端——led灯 - 咸鱼IC - 博客园