26考研 | 王道 | 计算机组成原理 | 七、输入输出系统

26考研 | 王道 | 计算机组成原理 | 七、输入输出系统

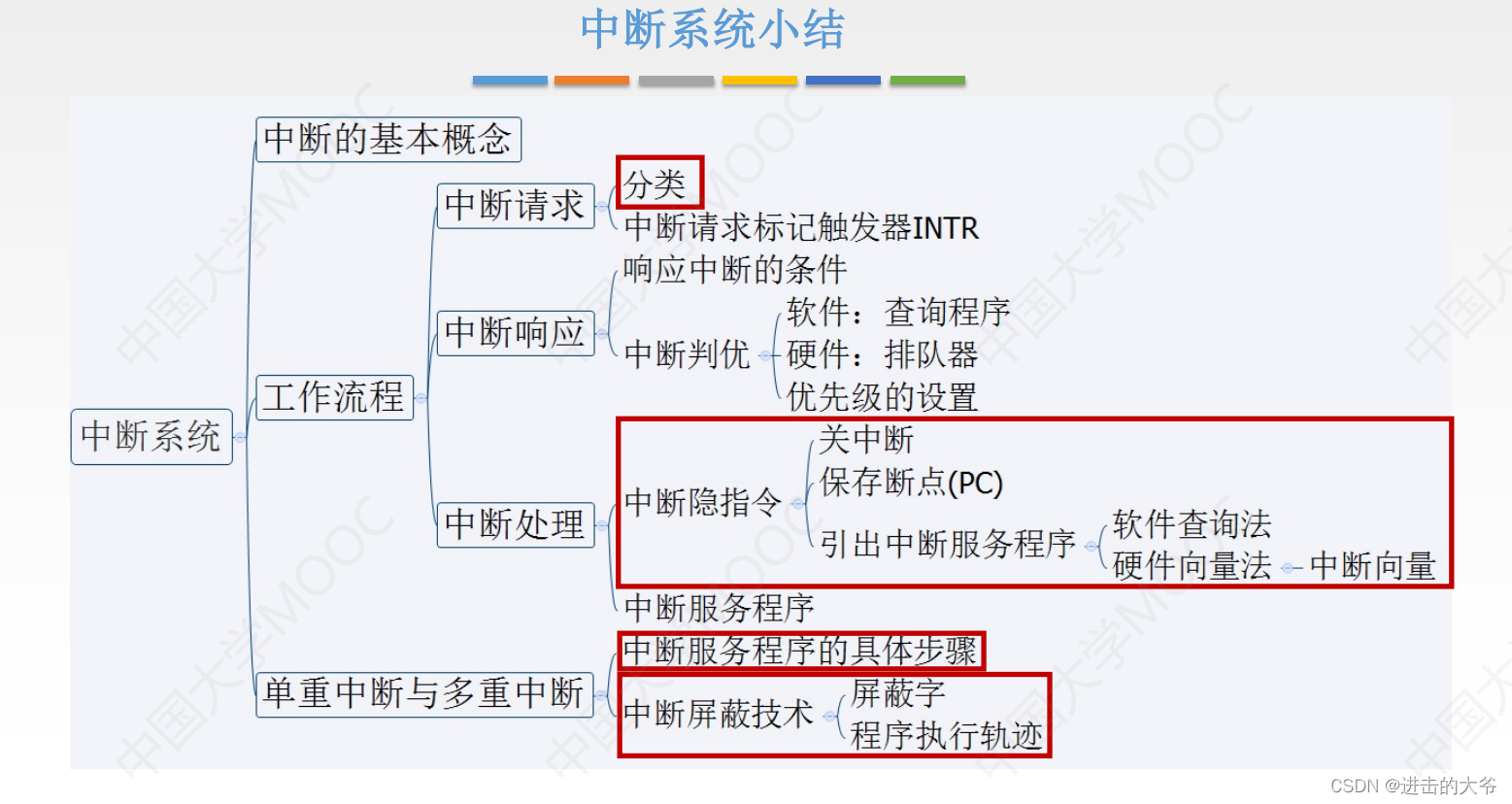

文章目录

- 26考研 | 王道 | 计算机组成原理 | 七、输入输出系统

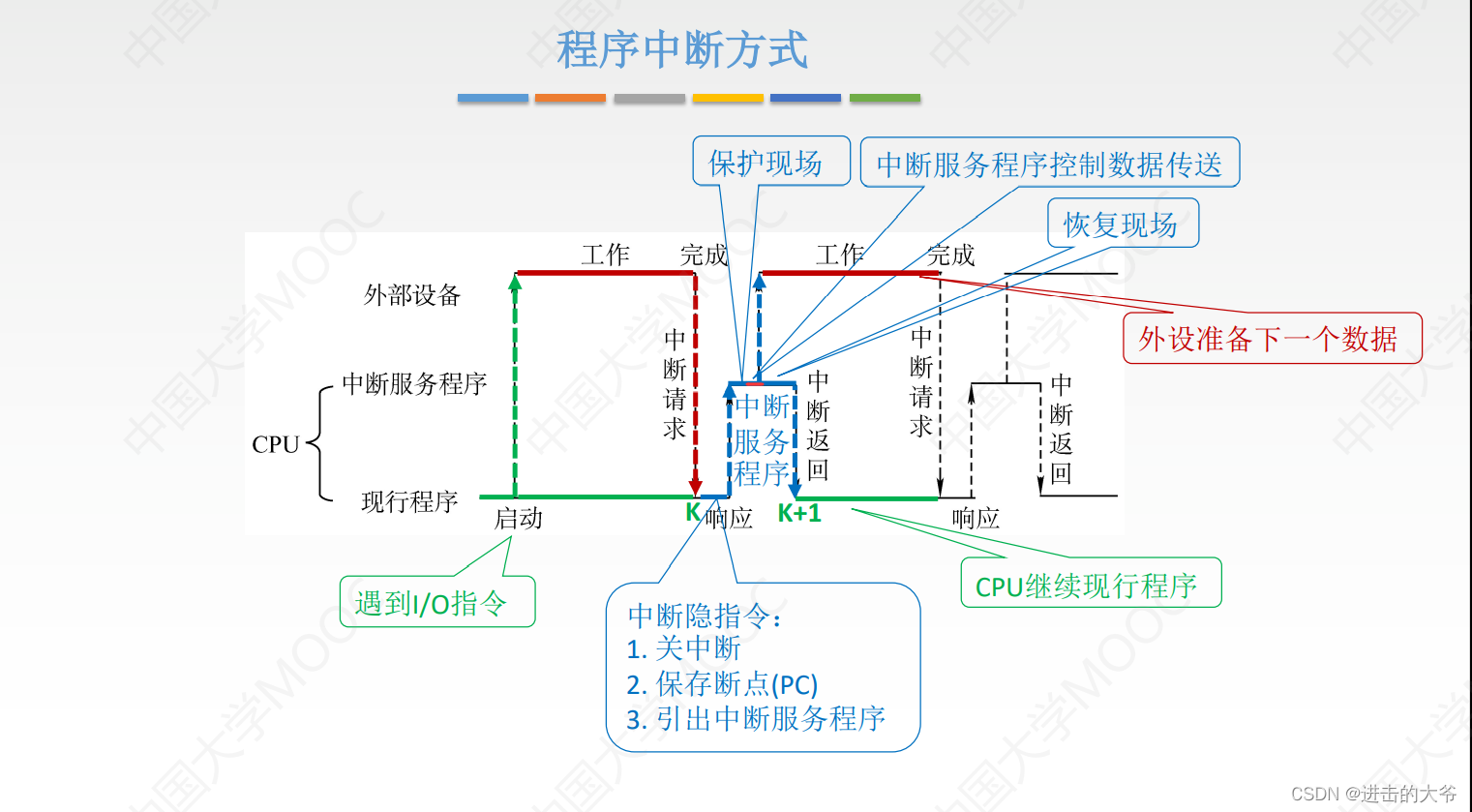

- 7.1 输入输出系统及I/O控制方式

- 外部设备(考纲没有,做个了解)

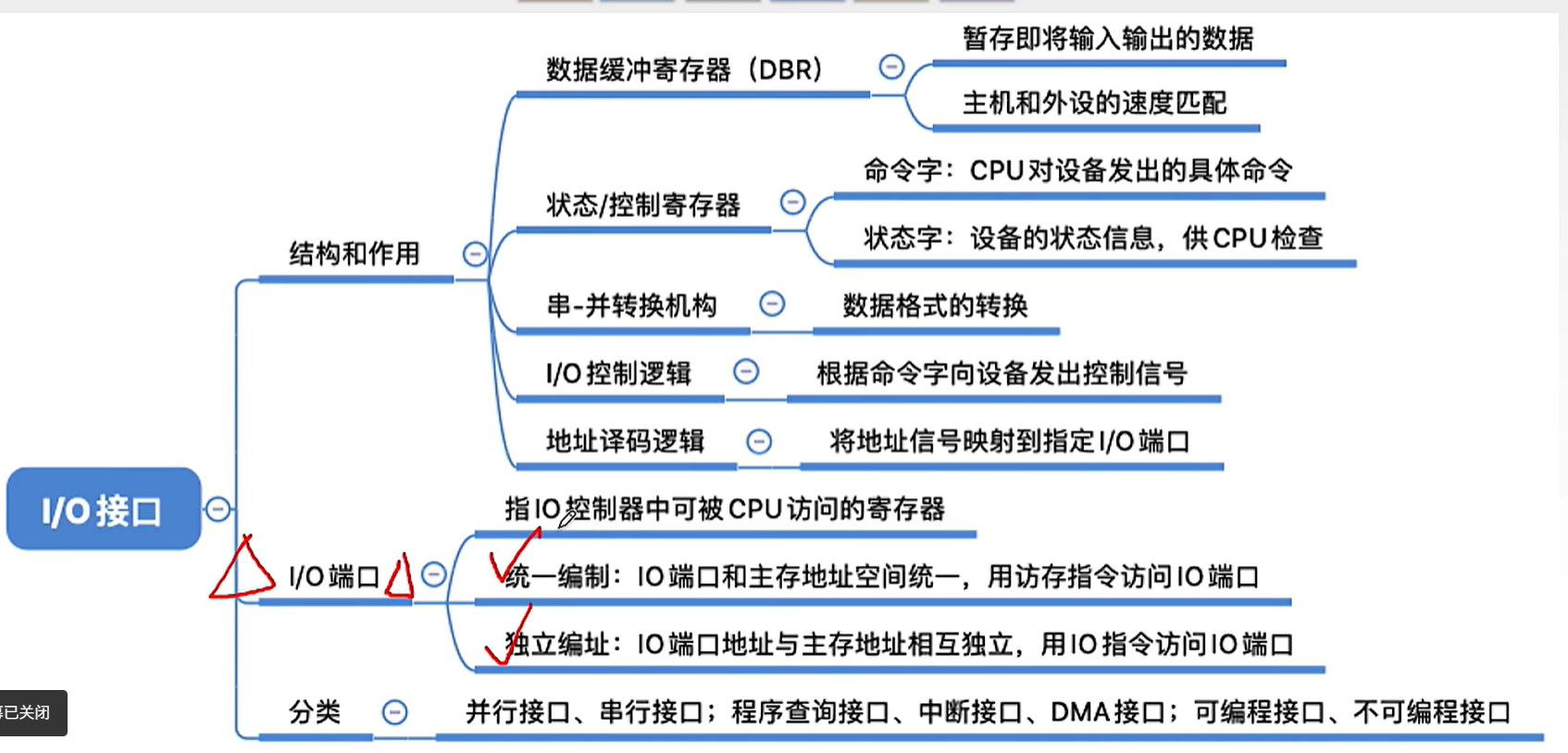

- 7.2 I/O接口

- 7.3 I/O方式

- 1. 程序查询方式

- 2. 中断的作用和原理

- 1.**中断响应阶段(硬件自动完成)**

- **2. 中断处理阶段(操作系统/驱动主导)**

- **3. 中断返回阶段**

- 3. 多重中断

- 4. 程序中断方式

- 5. DMA方式

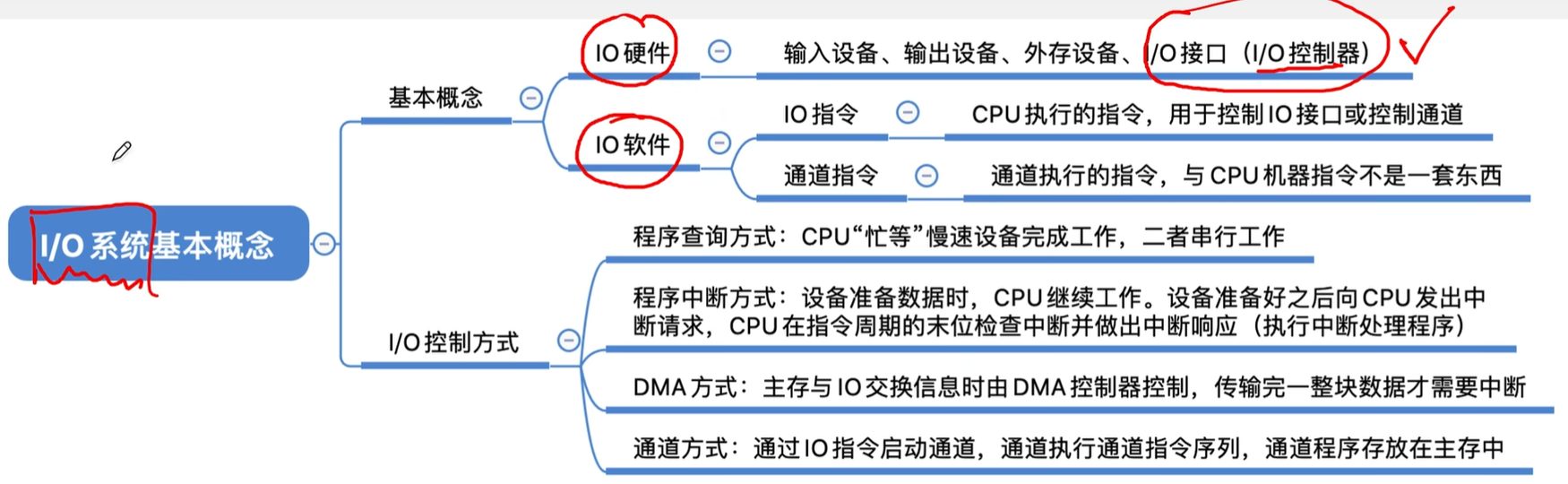

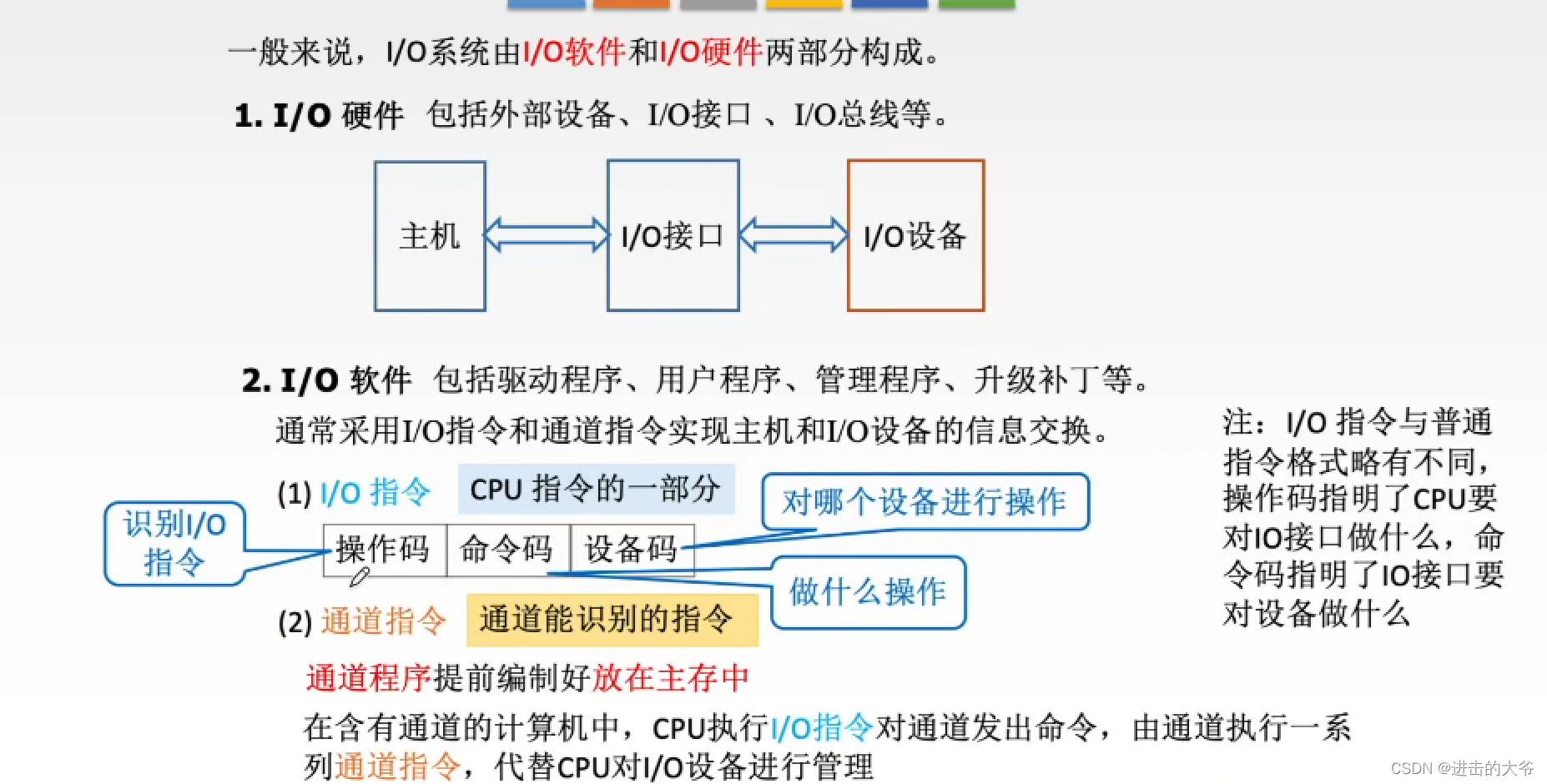

7.1 输入输出系统及I/O控制方式

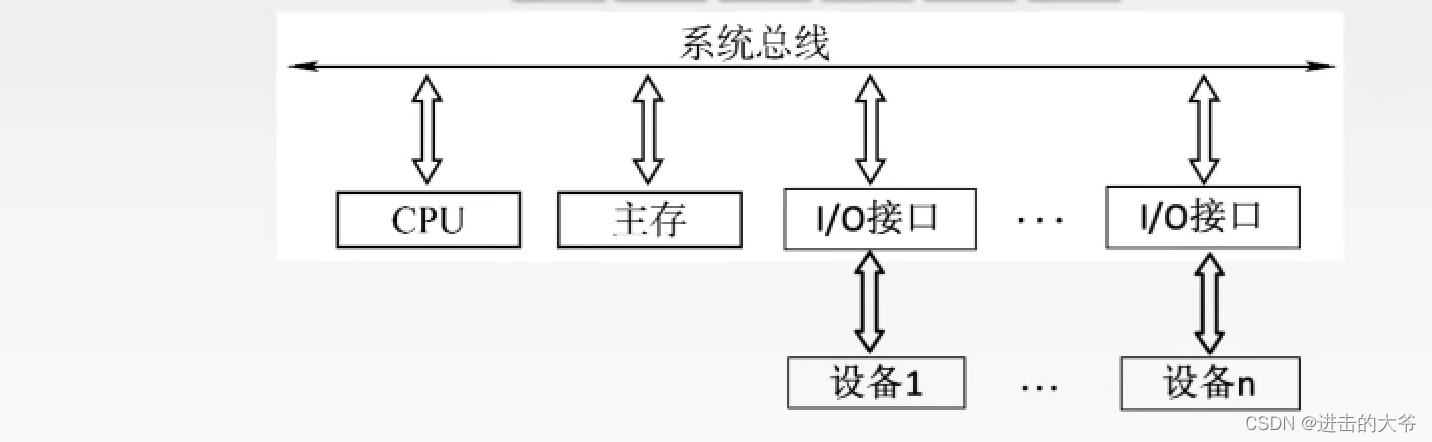

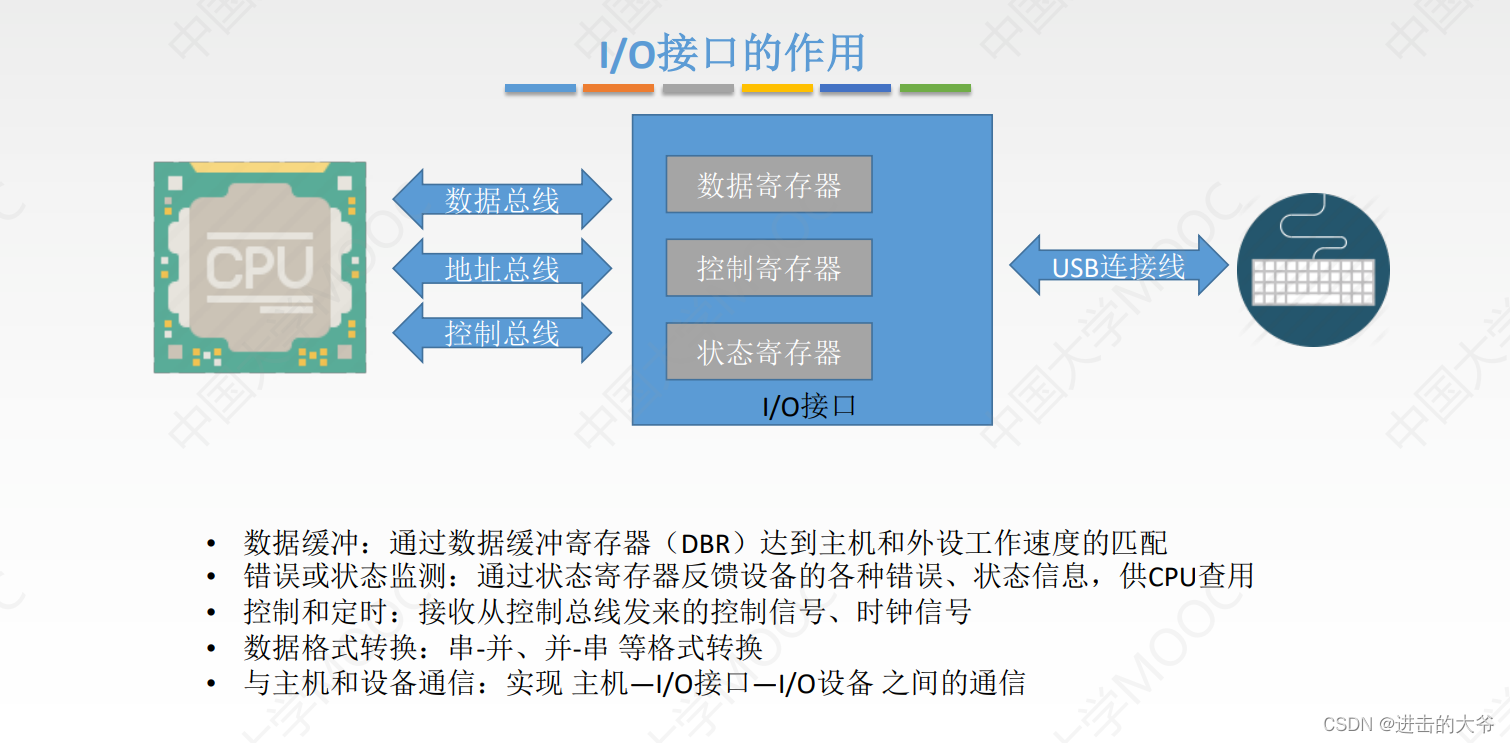

I/O接口:又称I/O控制器、设备控制器、负责协调主机与外部设备之间的数据传输。(I/O控制器就是一块芯片,常被集成在主板上)

I/O控制方式简介

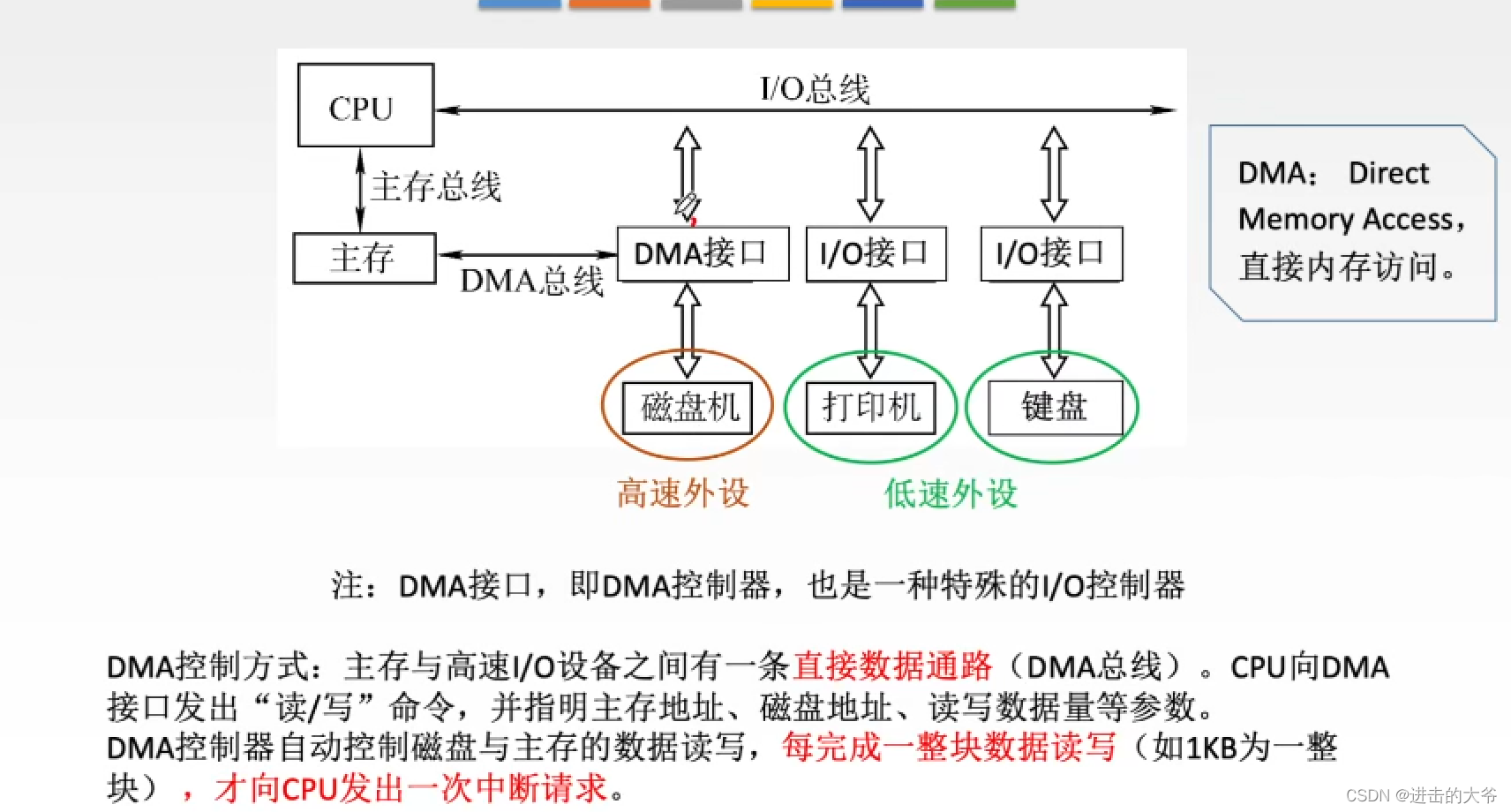

DMA控制方式

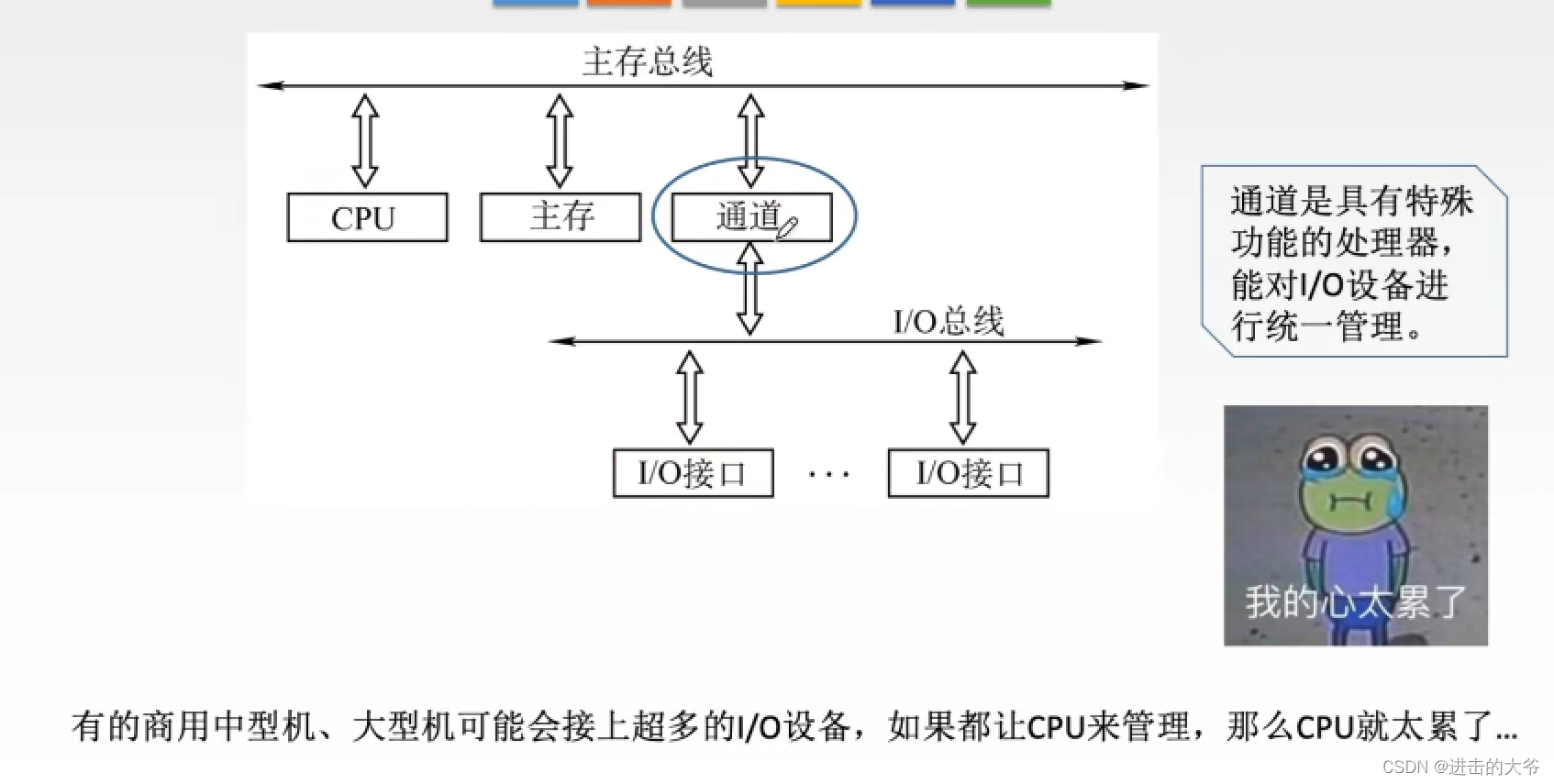

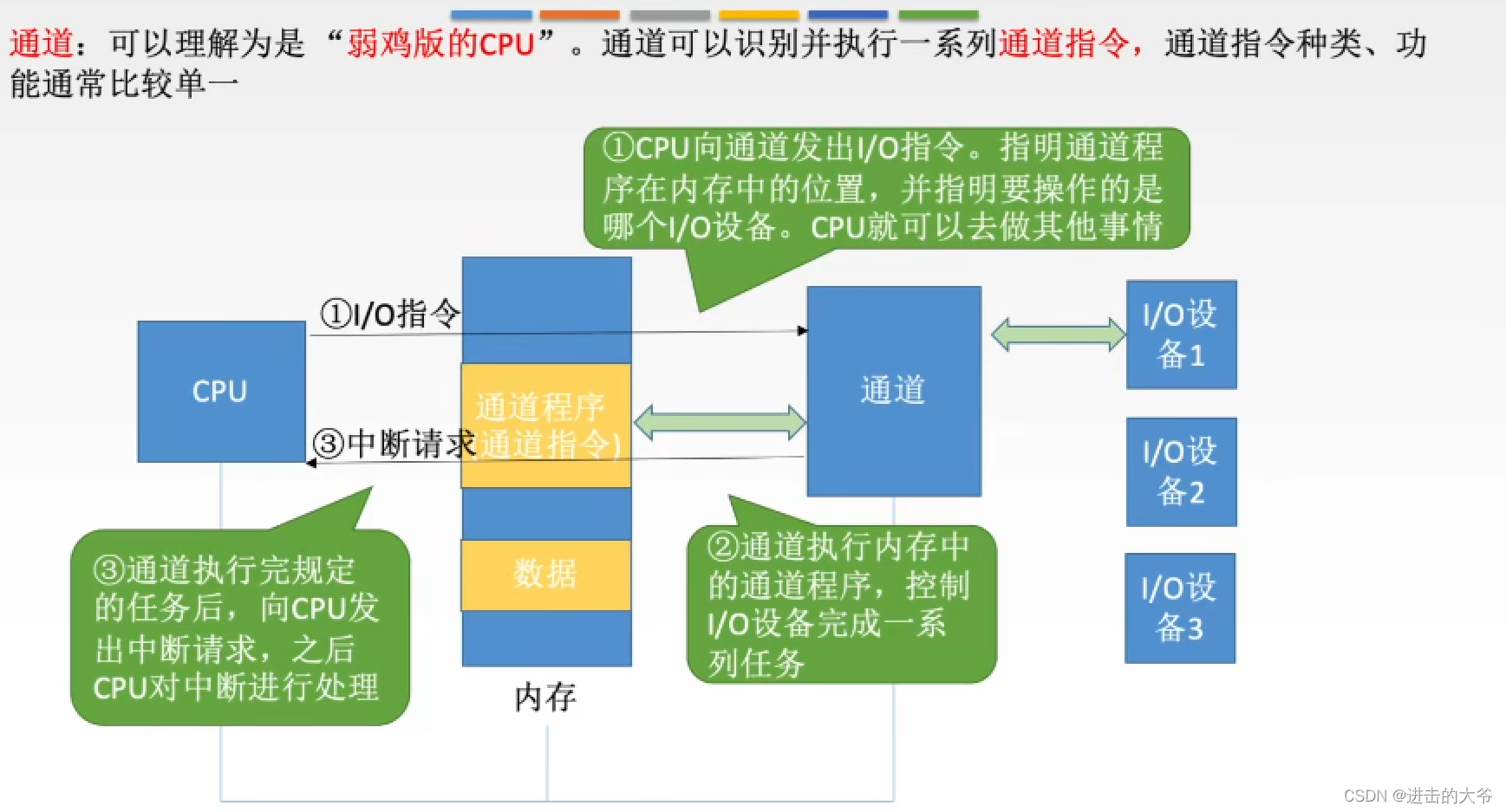

通道控制方式

I/O系统基本组成

在配有通道的计算机系统中,用户需要输入输出时,引起的中断是 访管中断 (因为这时调用的是系统提供的接口,要去请求操作系统服务,此时会使得访管中断)

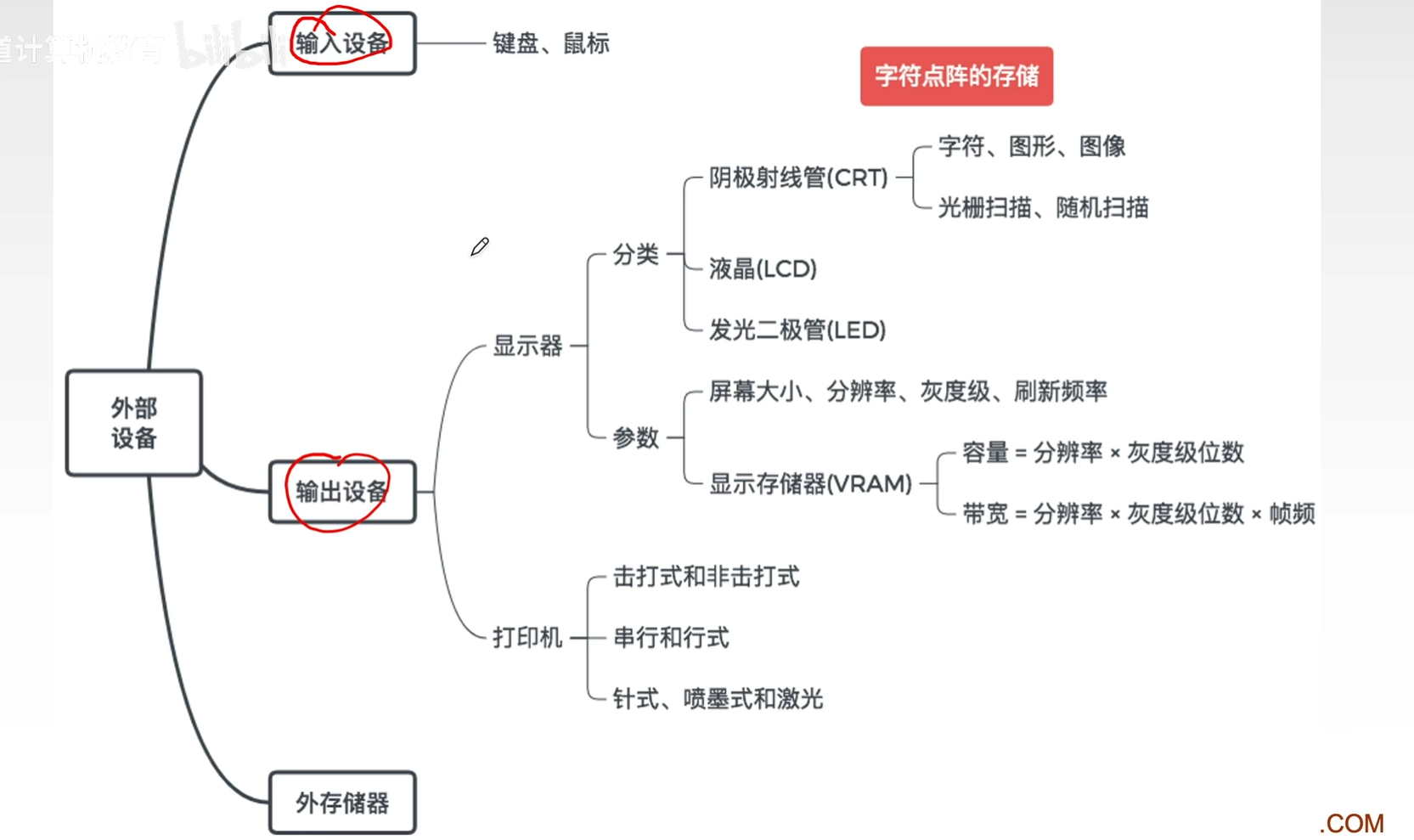

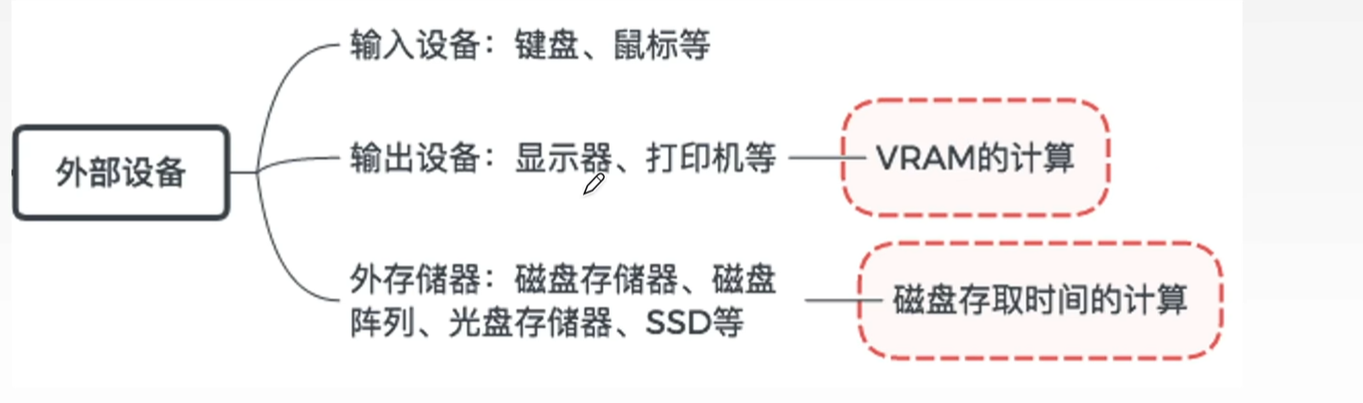

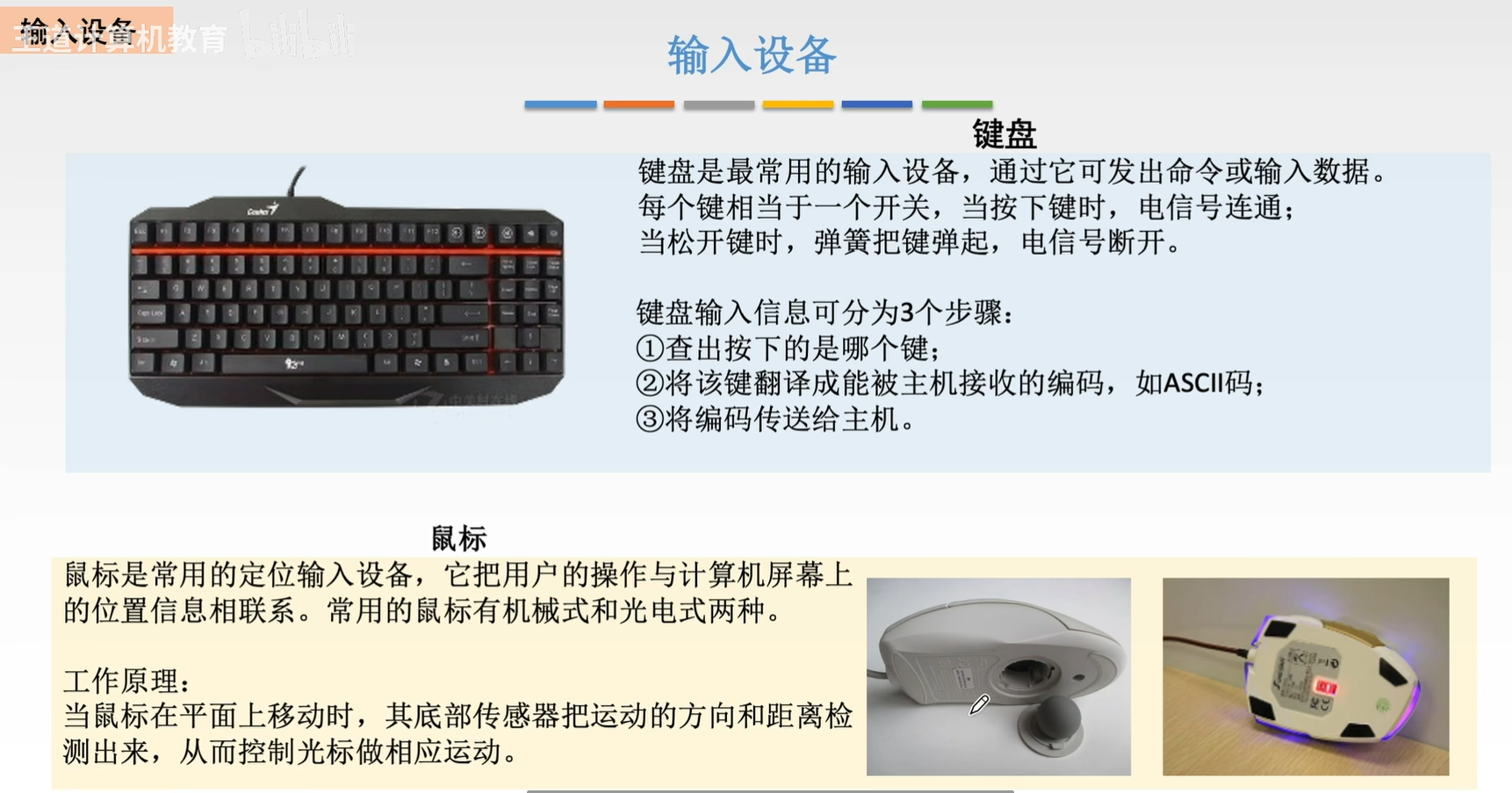

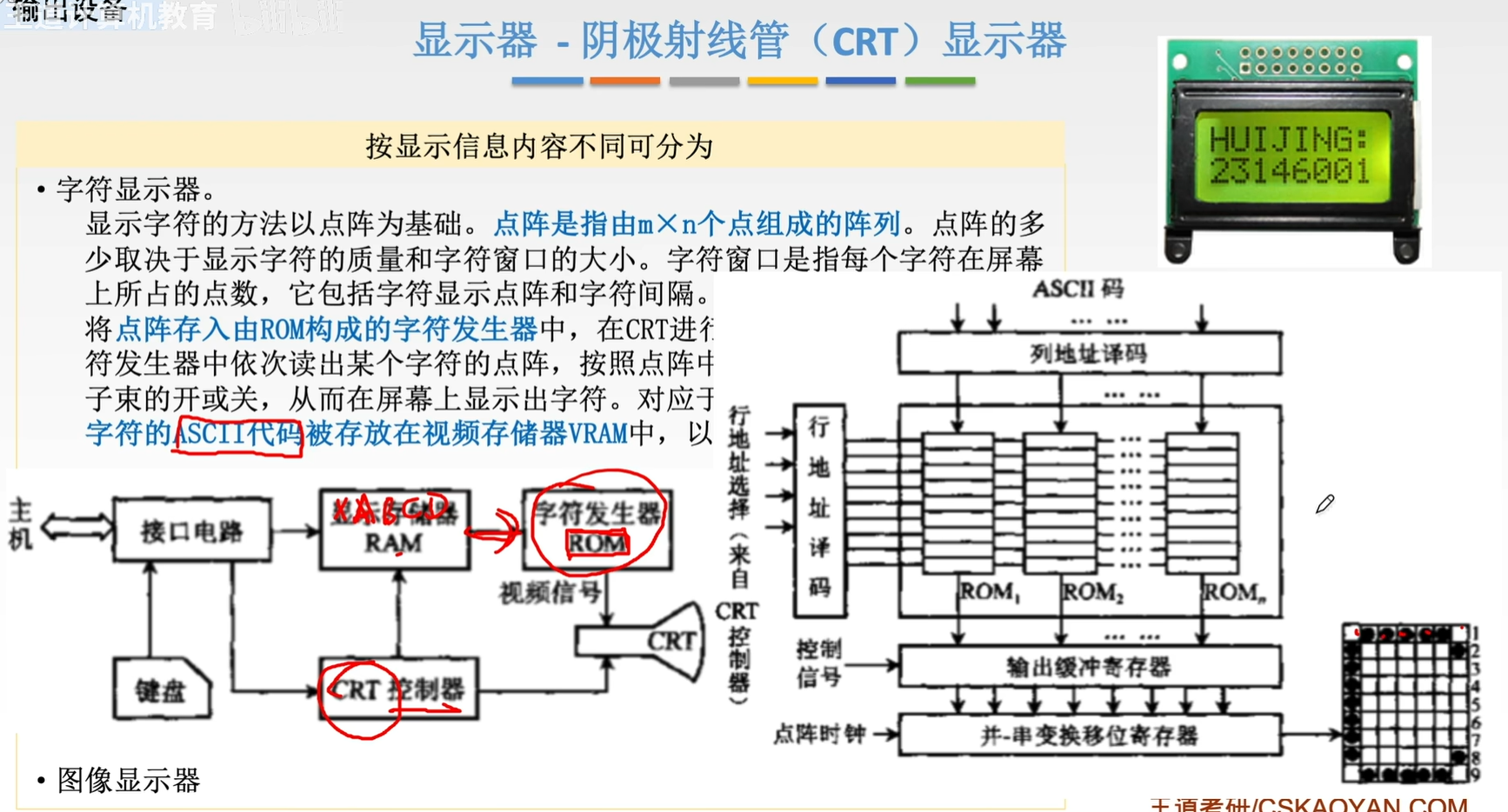

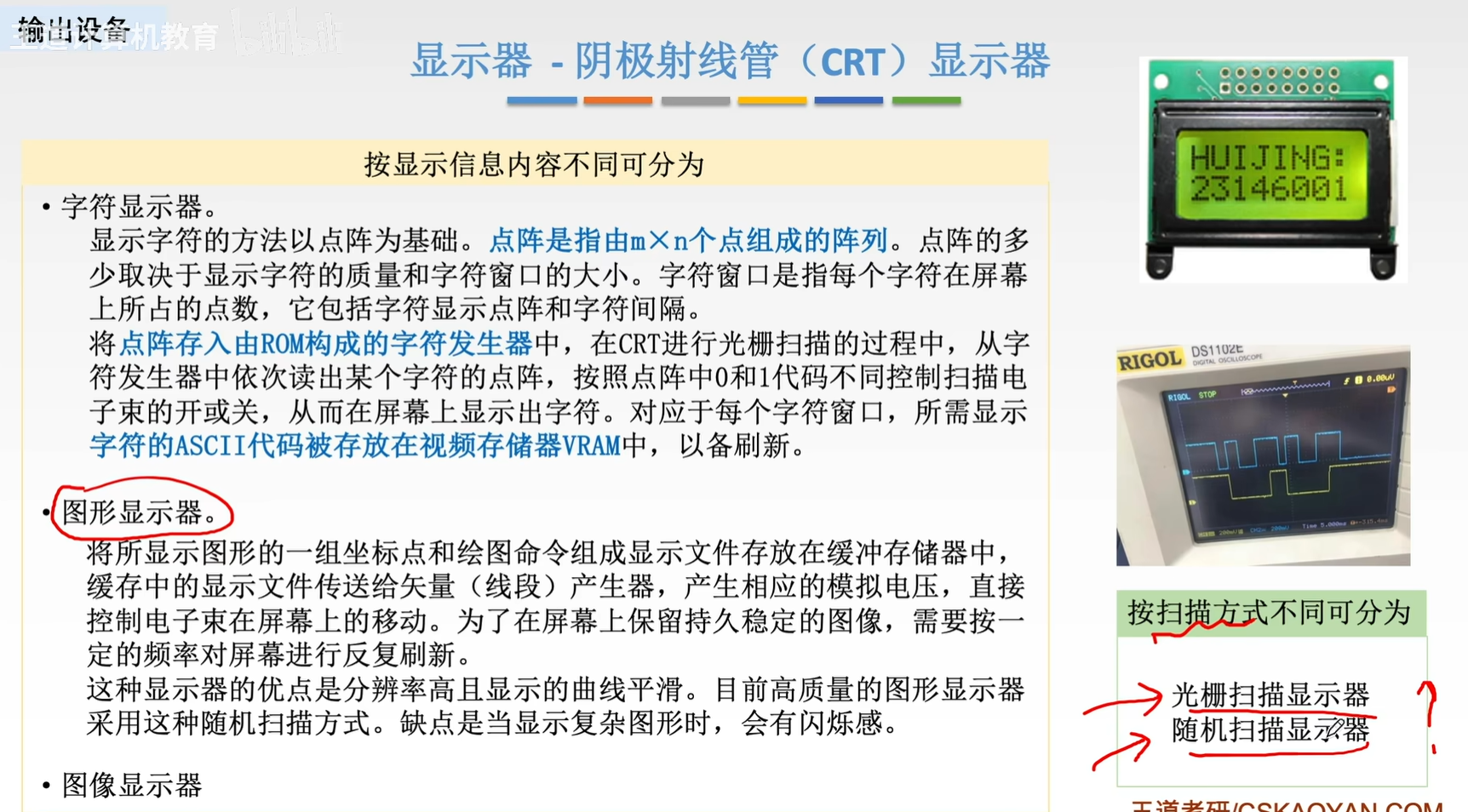

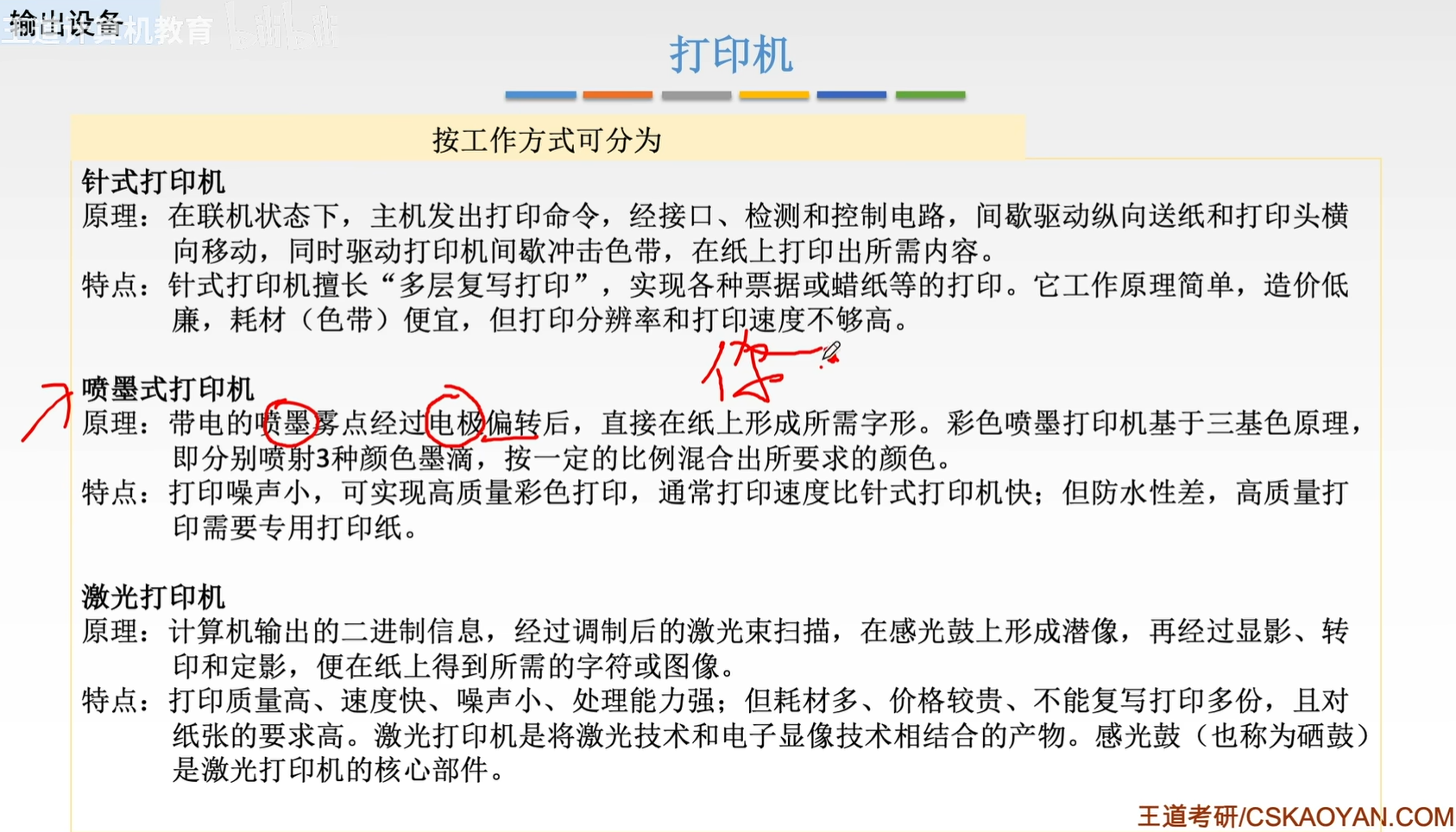

外部设备(考纲没有,做个了解)

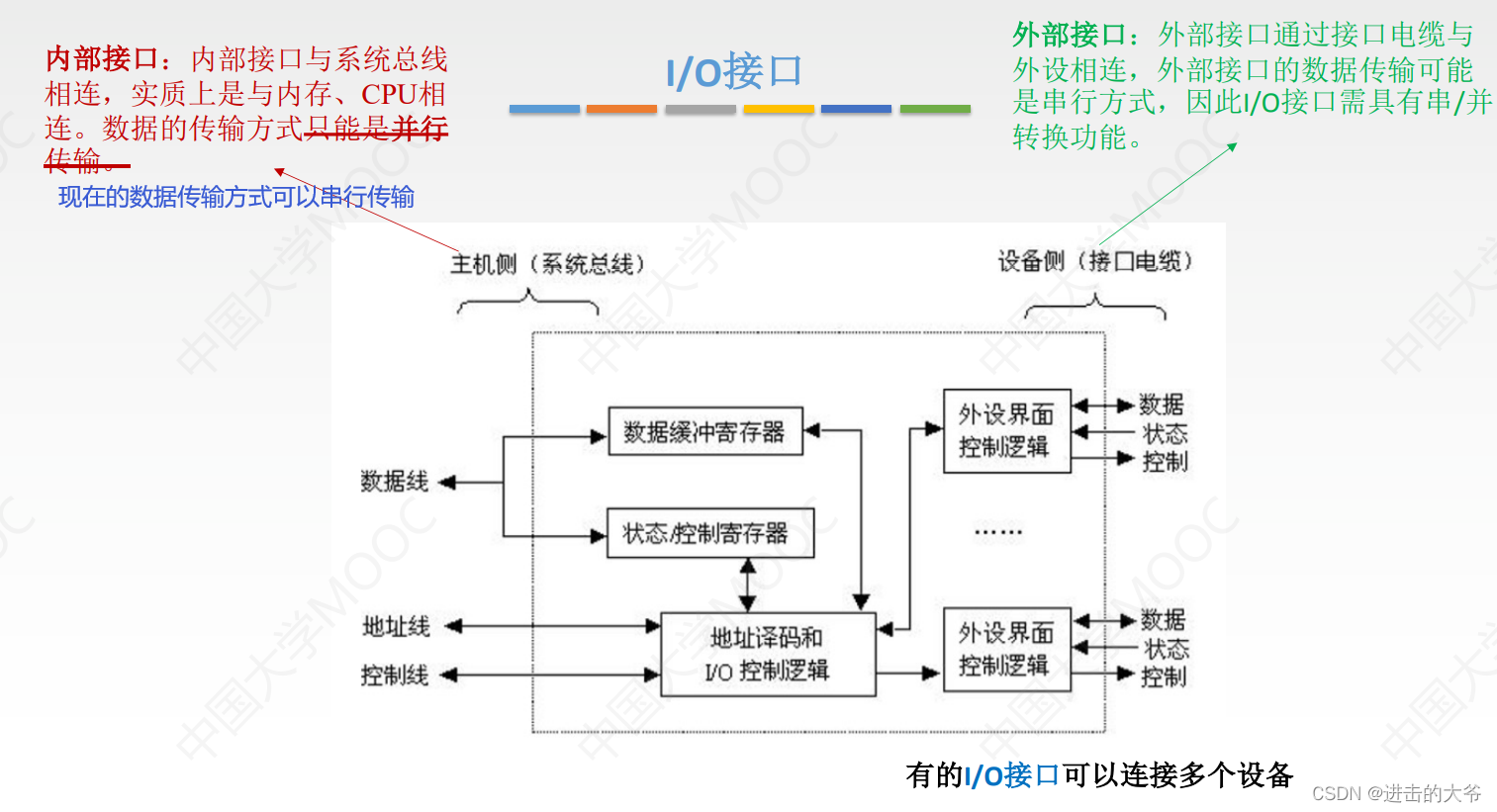

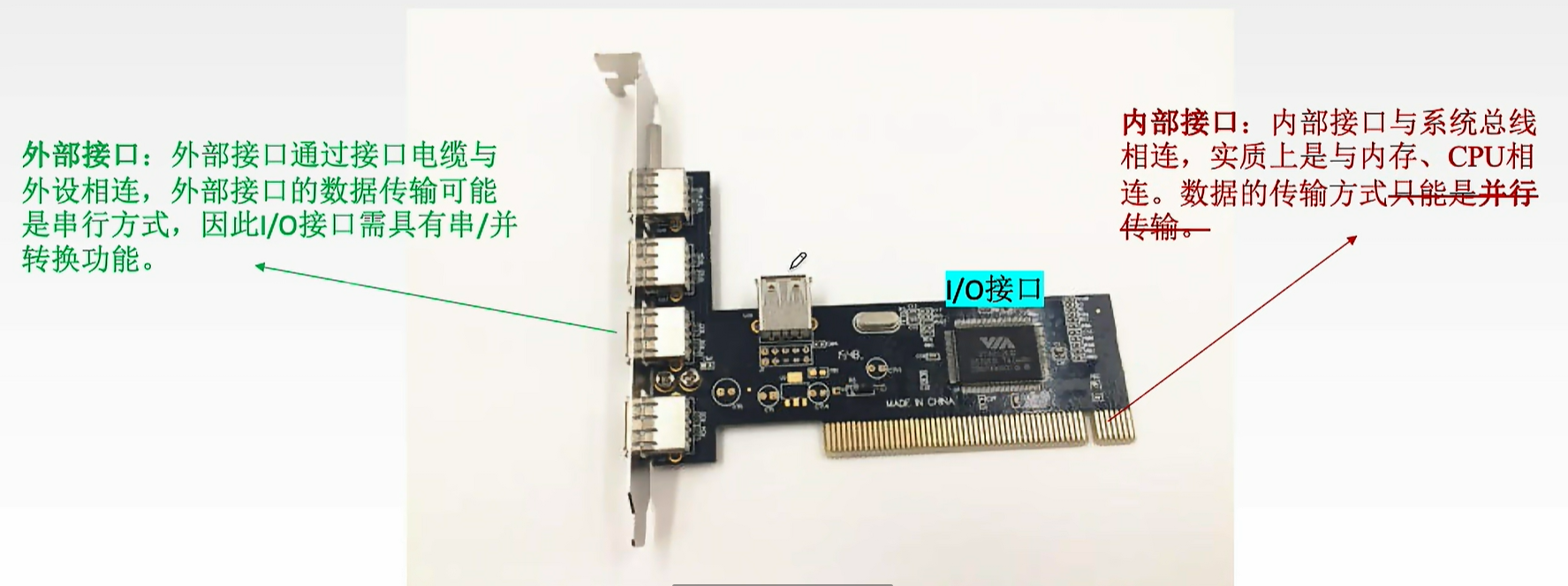

7.2 I/O接口

磁盘驱动器是磁头、磁盘和读写电路组成的,也就是常说的磁盘本身,不是I/O接口

功能:选址功能、传送命令功能、传送数据功能、反映I/O设备工作状态的功能

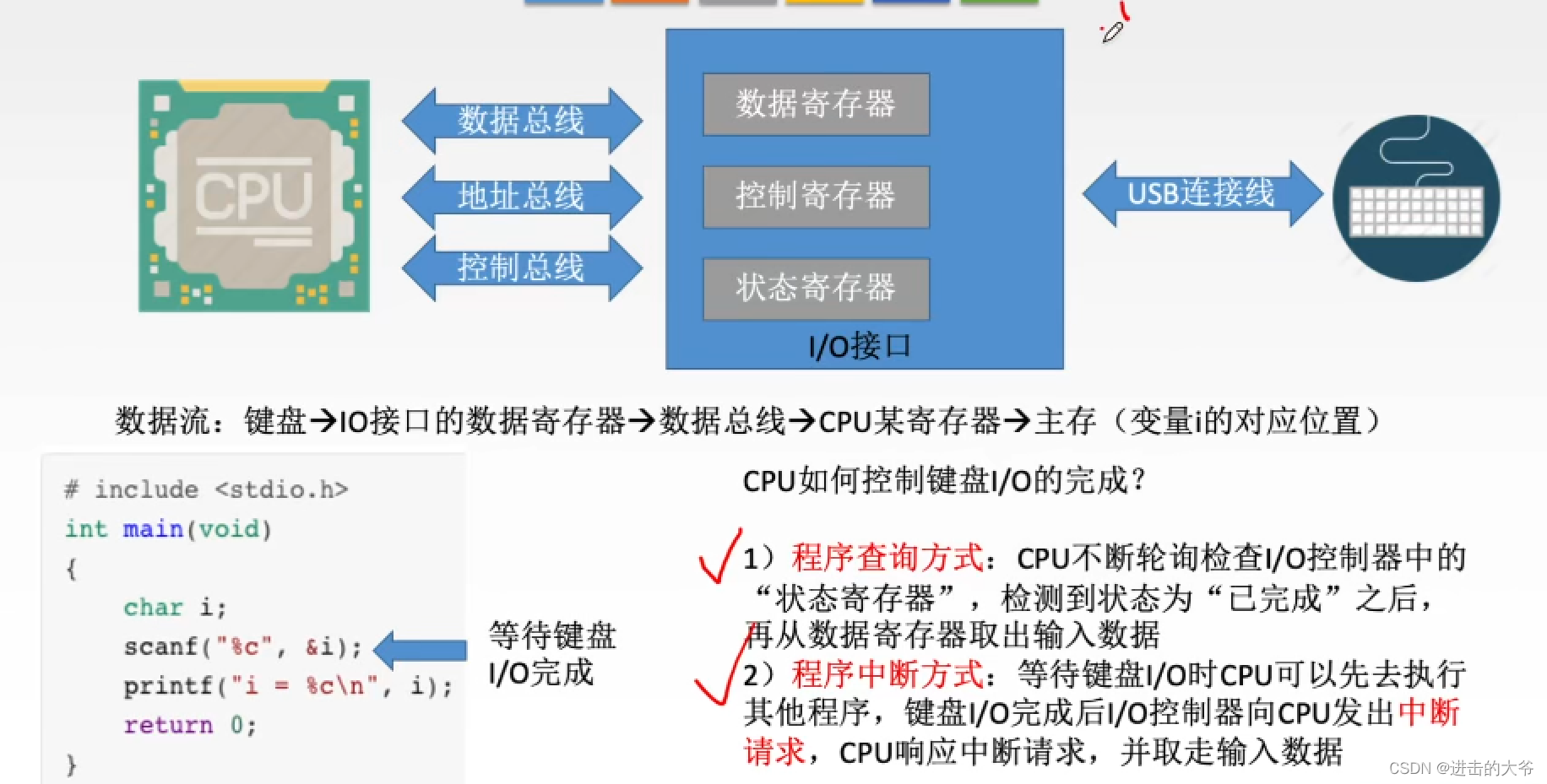

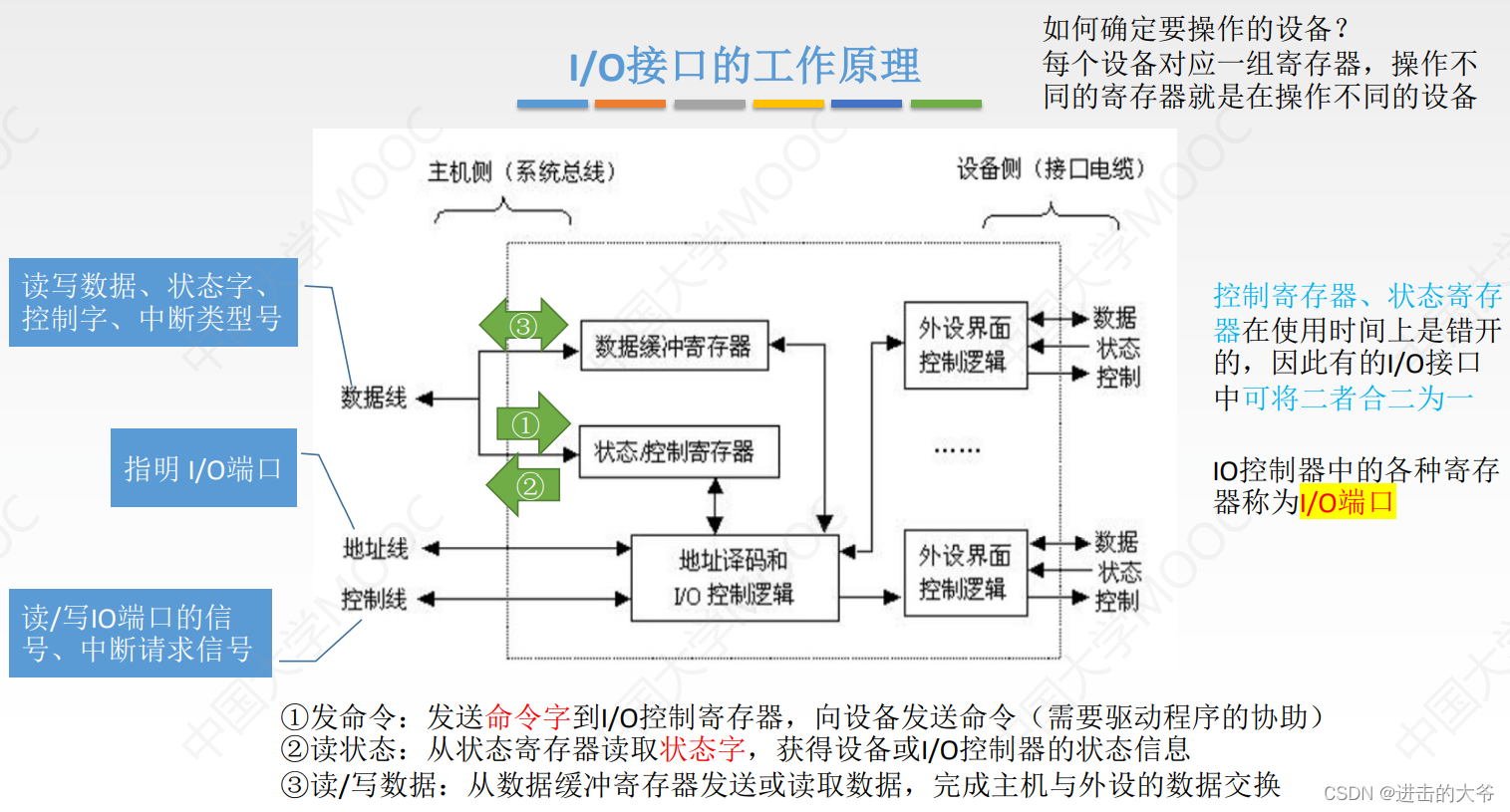

I/O接口的工作原理

接口和设备之间不会传送中断请求信号

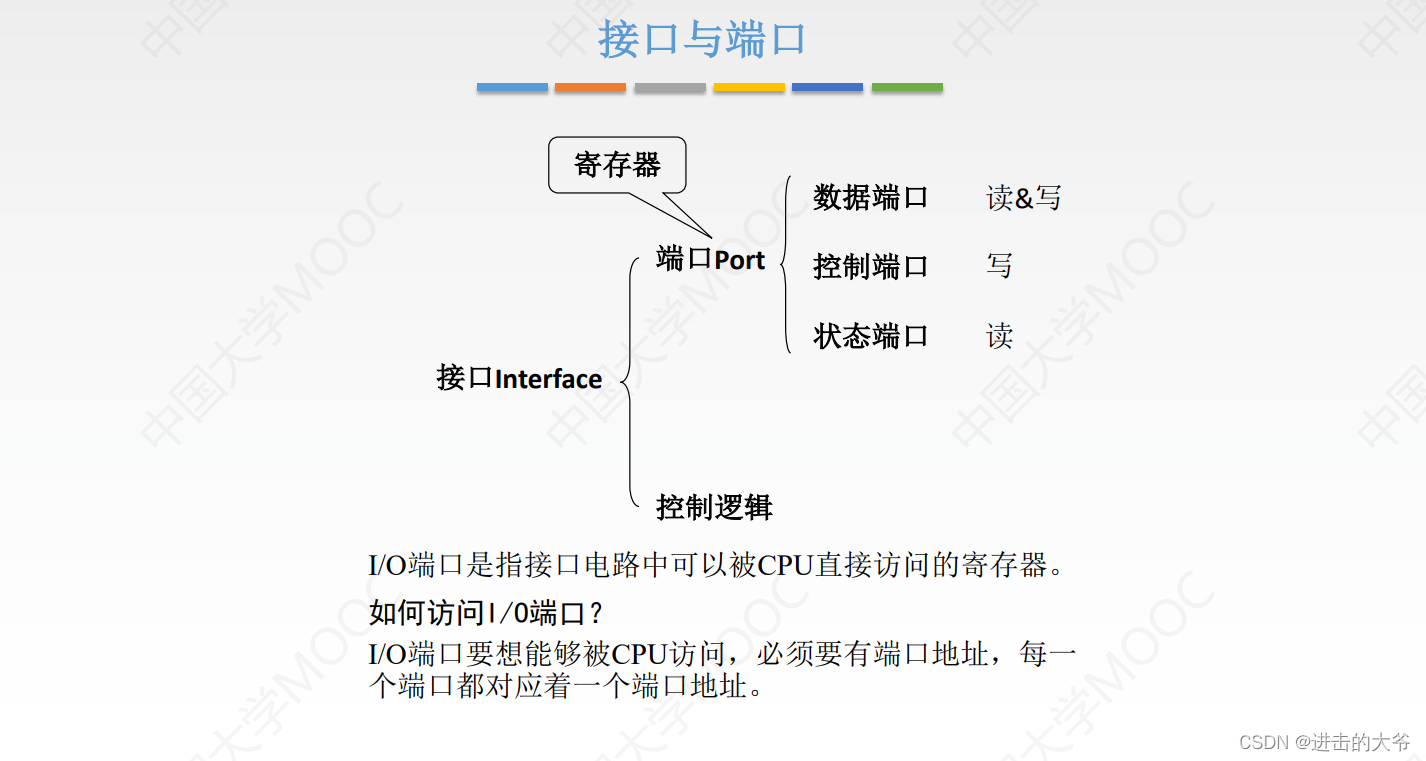

接口与端口

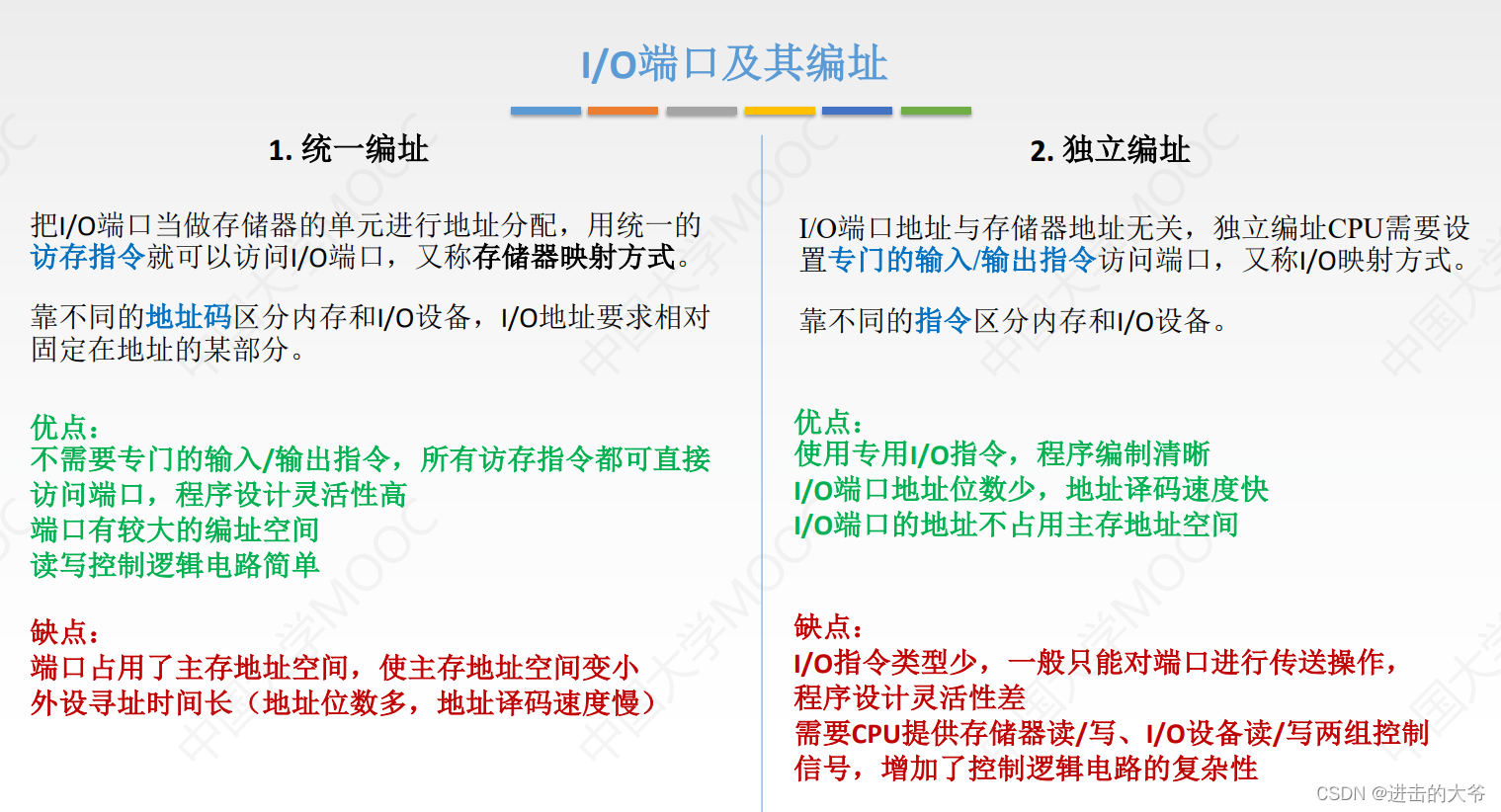

统一编址 V.S. 独立编址

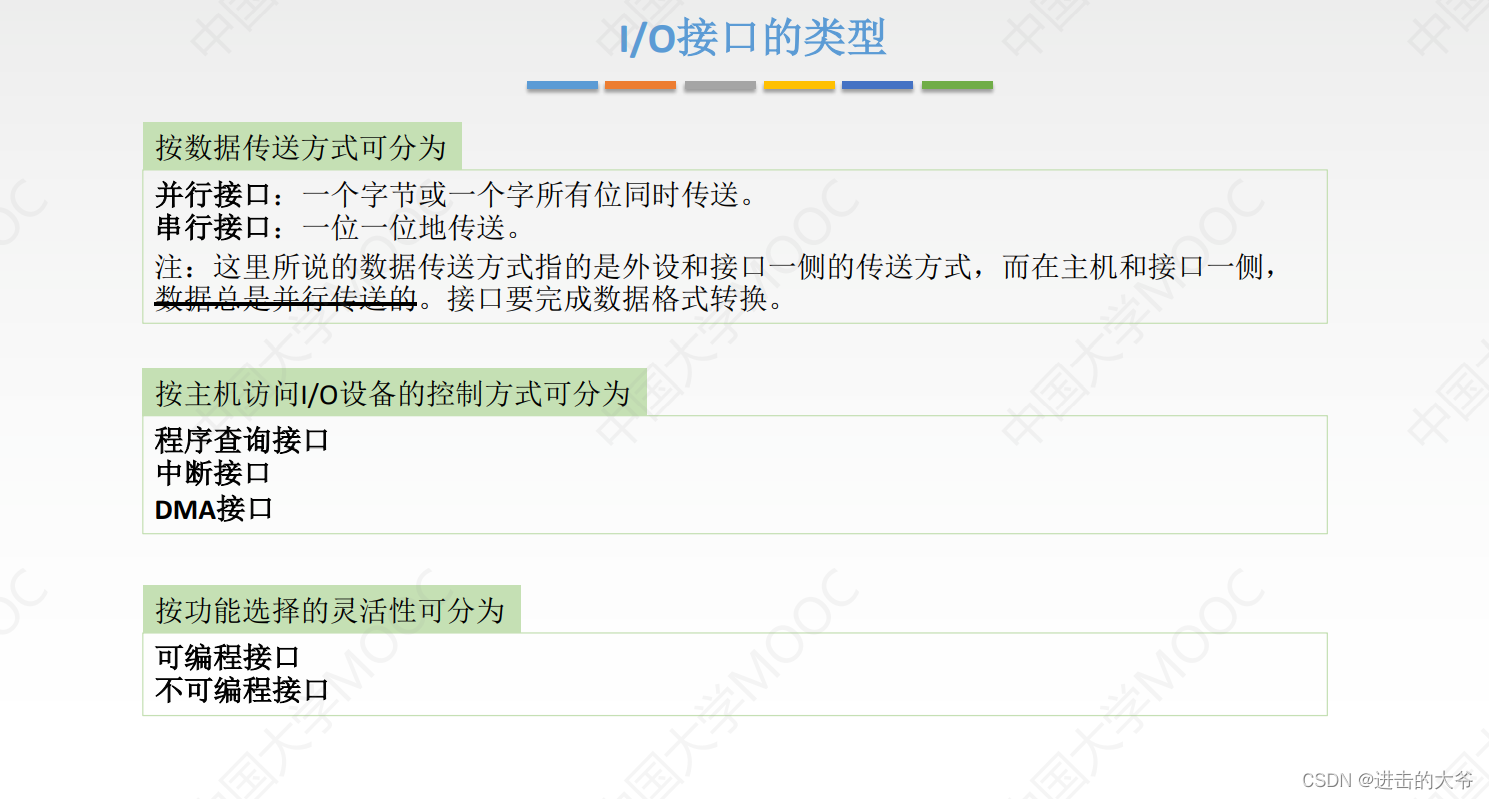

I/O接口的类型

磁盘驱动器向盘片磁道记录数据时采用穿行方式写入

USB就是串行接口

程序员进行系统调用访问设备使用的是逻辑地址

7.3 I/O方式

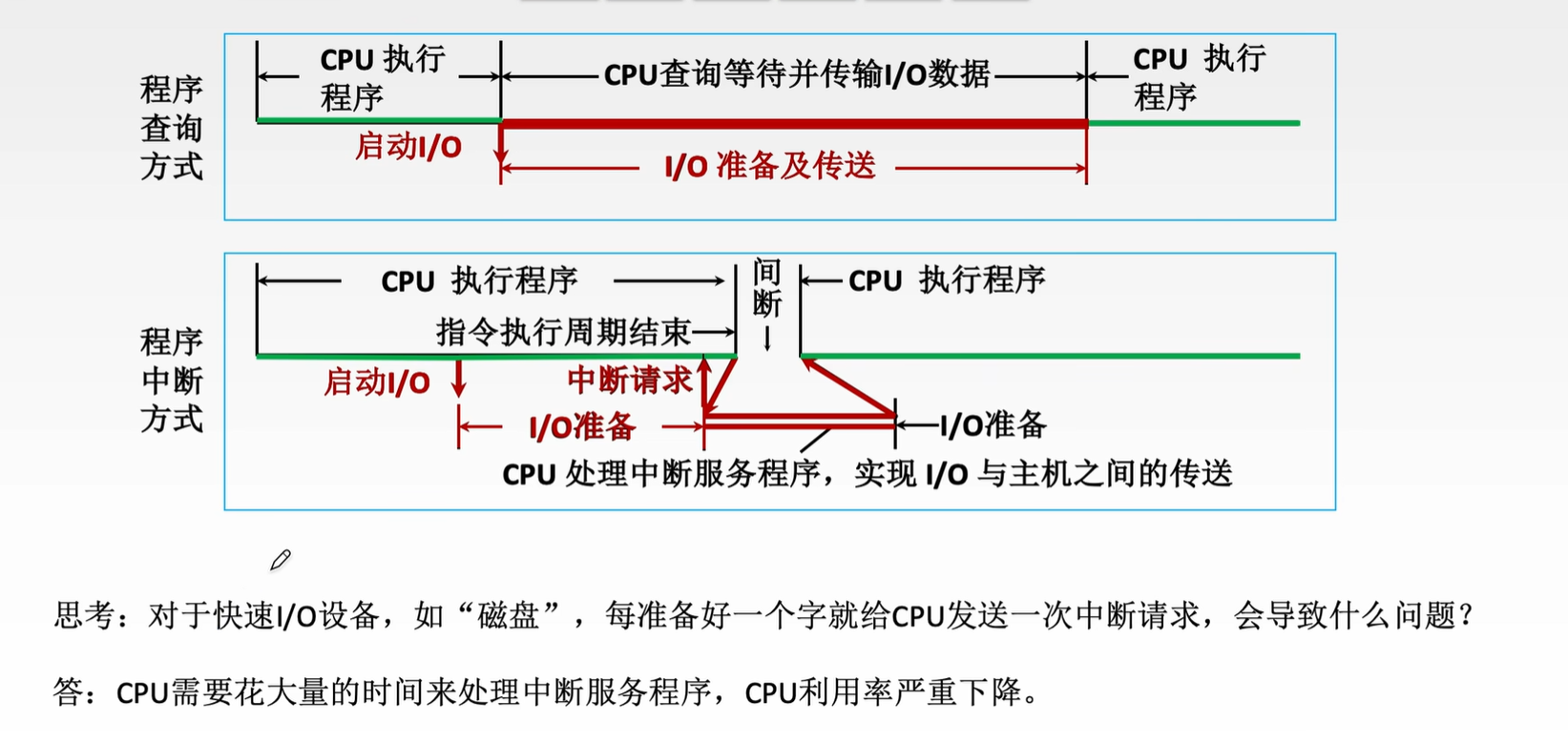

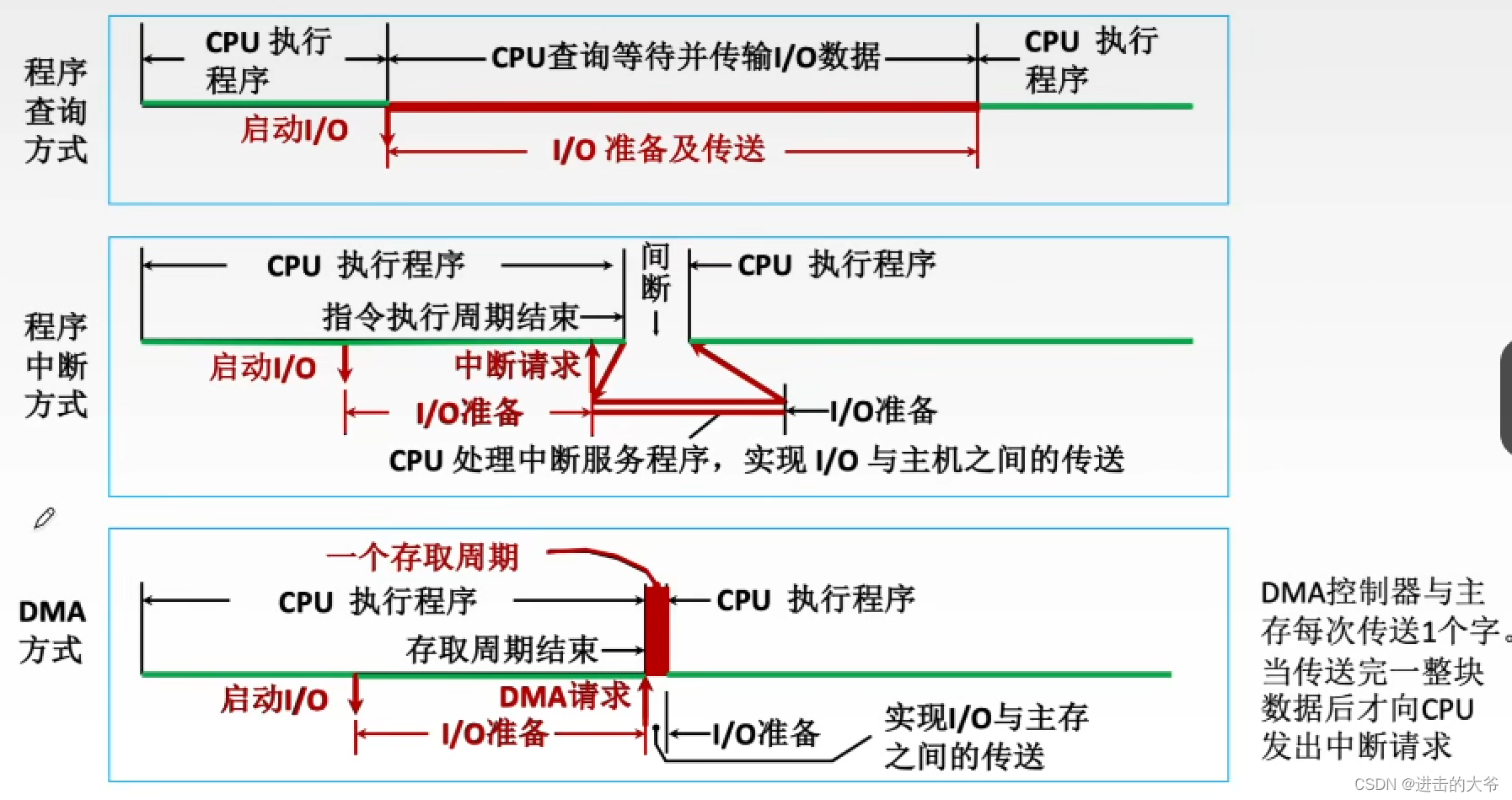

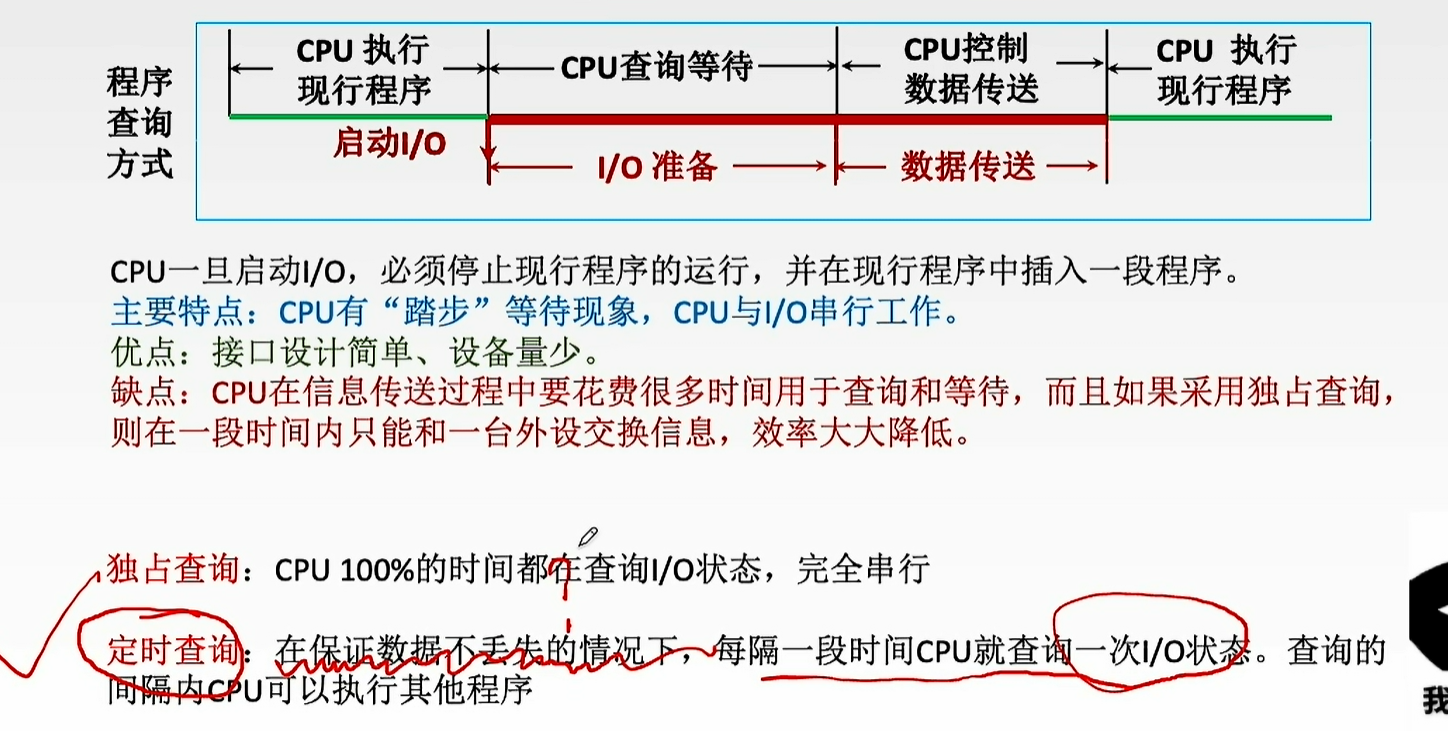

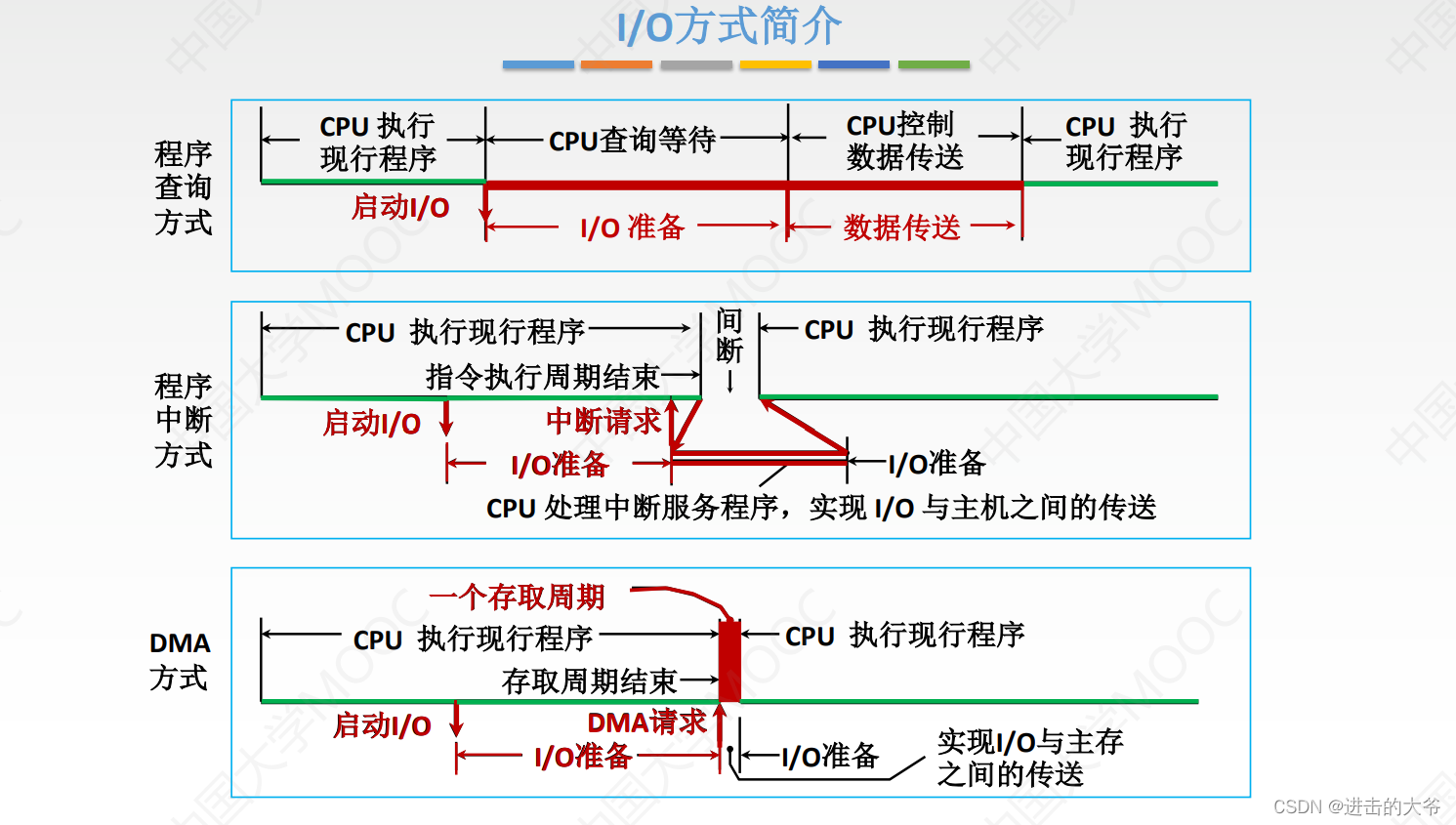

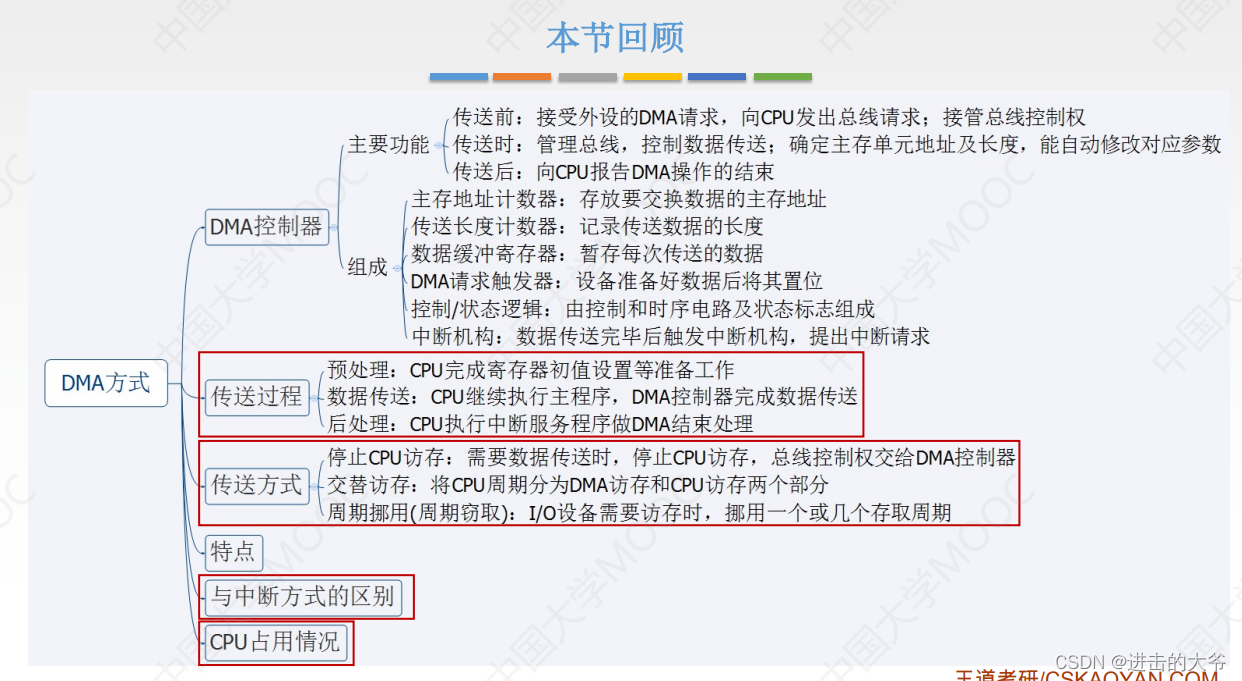

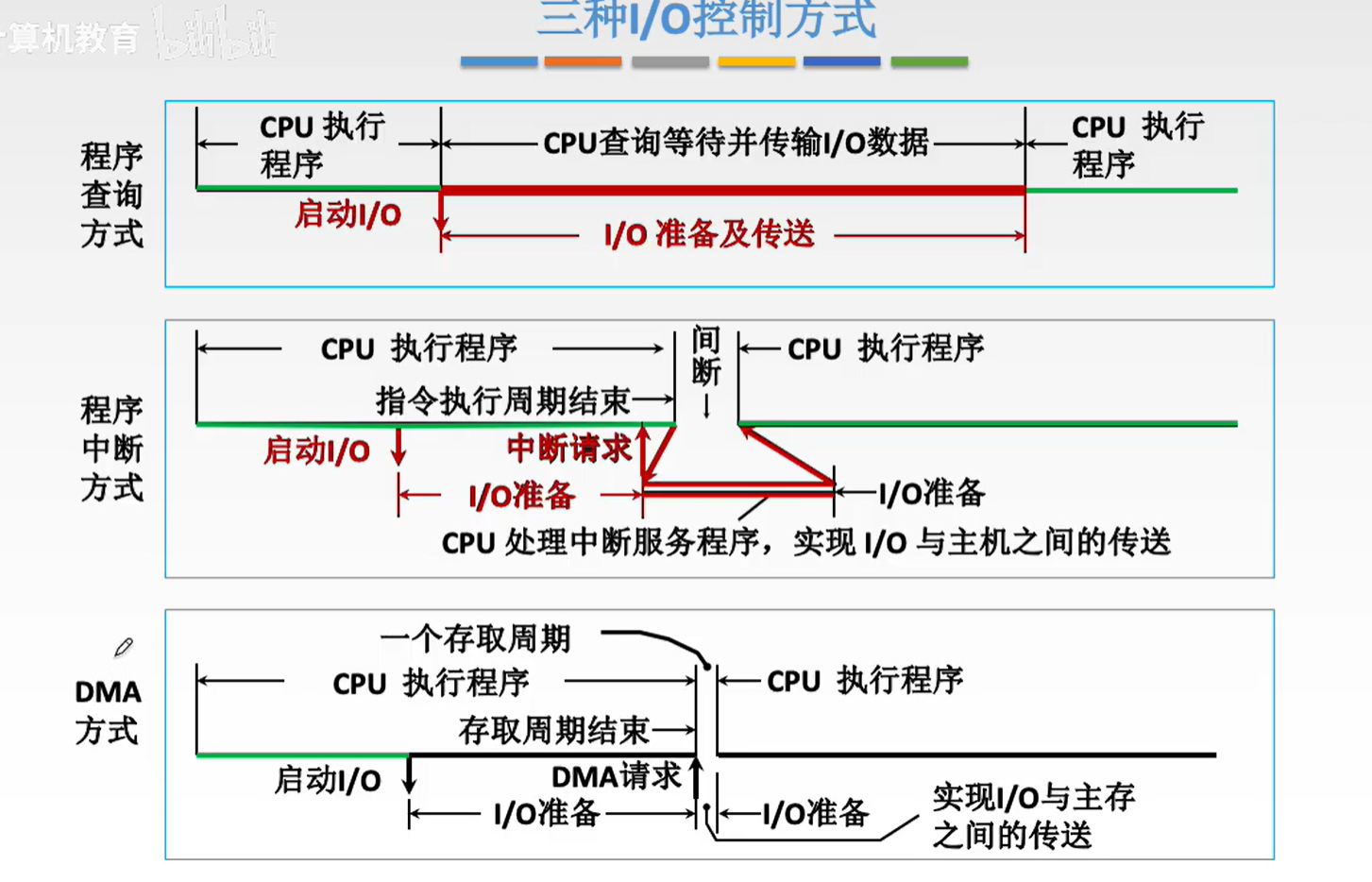

1.在各种I/O方式中,这三种方式的特点如下所示:

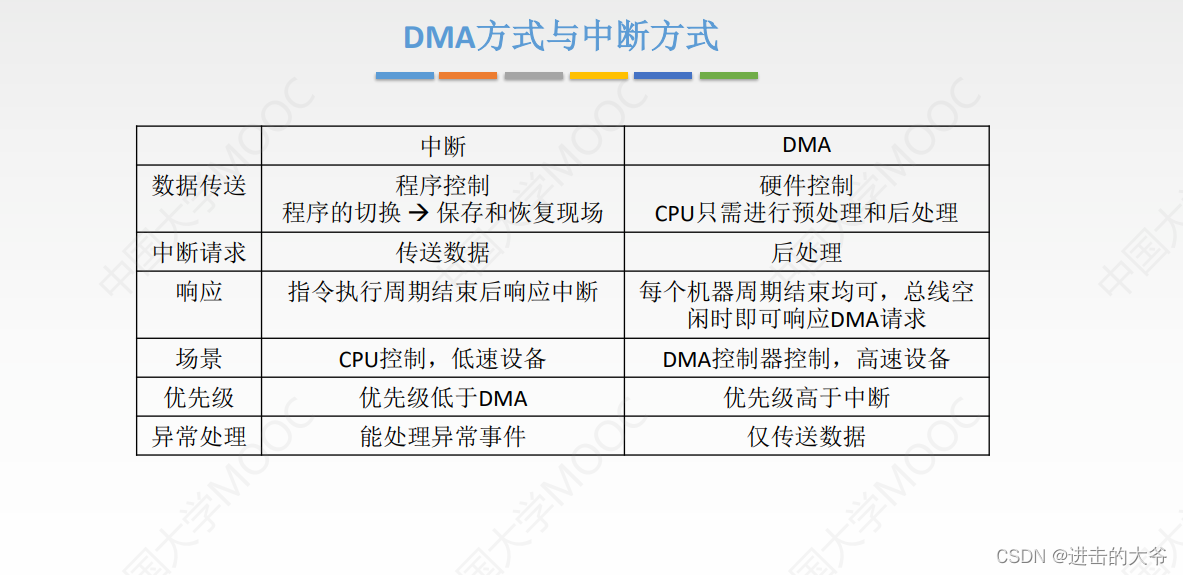

2.DMA优先级高于程序中断的优先级

3.程序中断方式需要保护现场,DMA方式在传输过程中不需要保护现场

4.程序中断过程是由硬件(称中断隐指令)和中断服务程序共同完成的

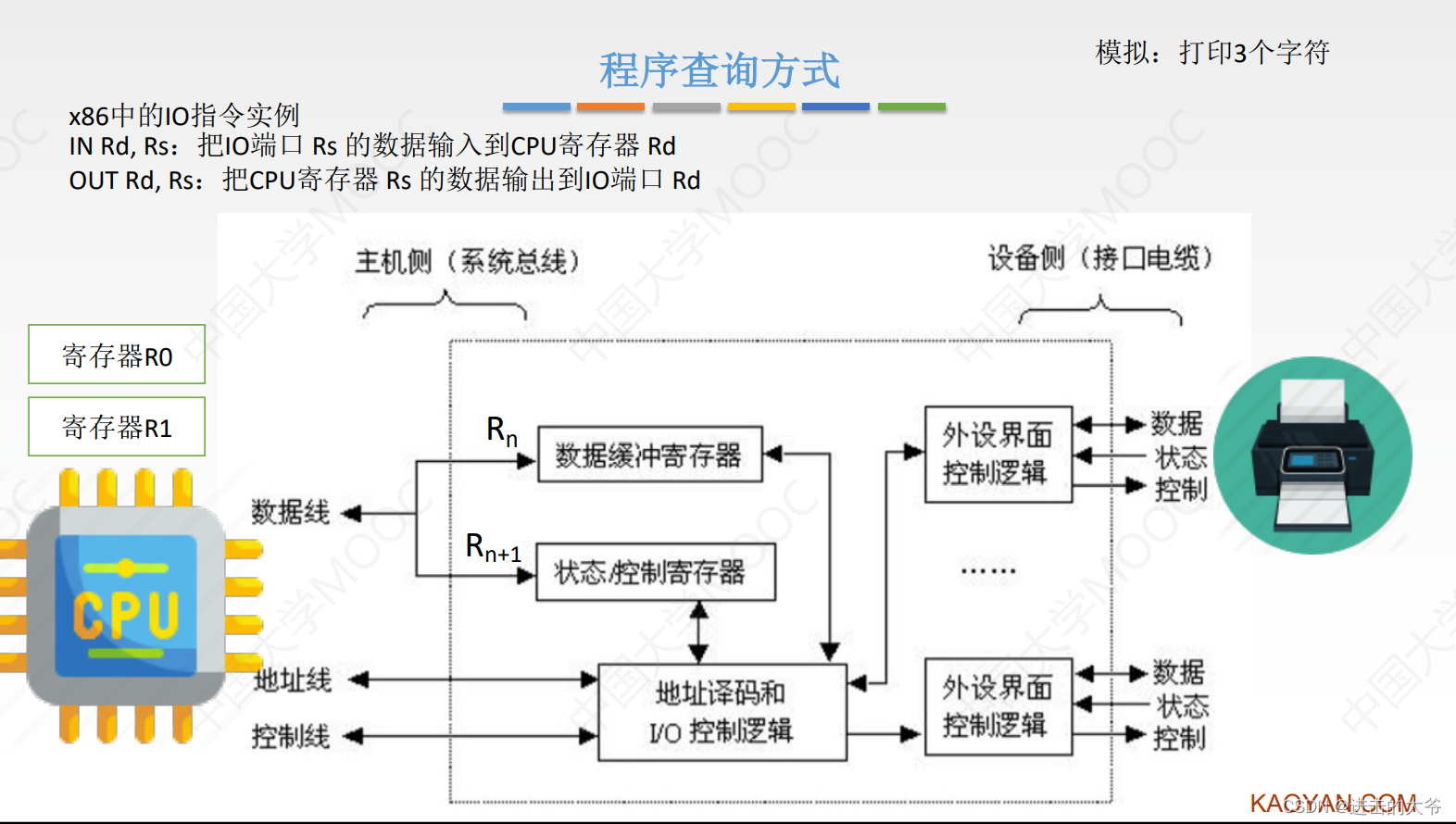

5.中断I/O方式下,CPU执行中断服务程序时会执行相应的I/O指令,实现CPU的通用寄存器和外设接口中的寄存器之间的直接数据交换

6.中断请求的是CPU时间,要求CPU执行程序来处理发生的相关事件

7.CPU对外部中断的响应不可能发生在一条指令的执行过程中

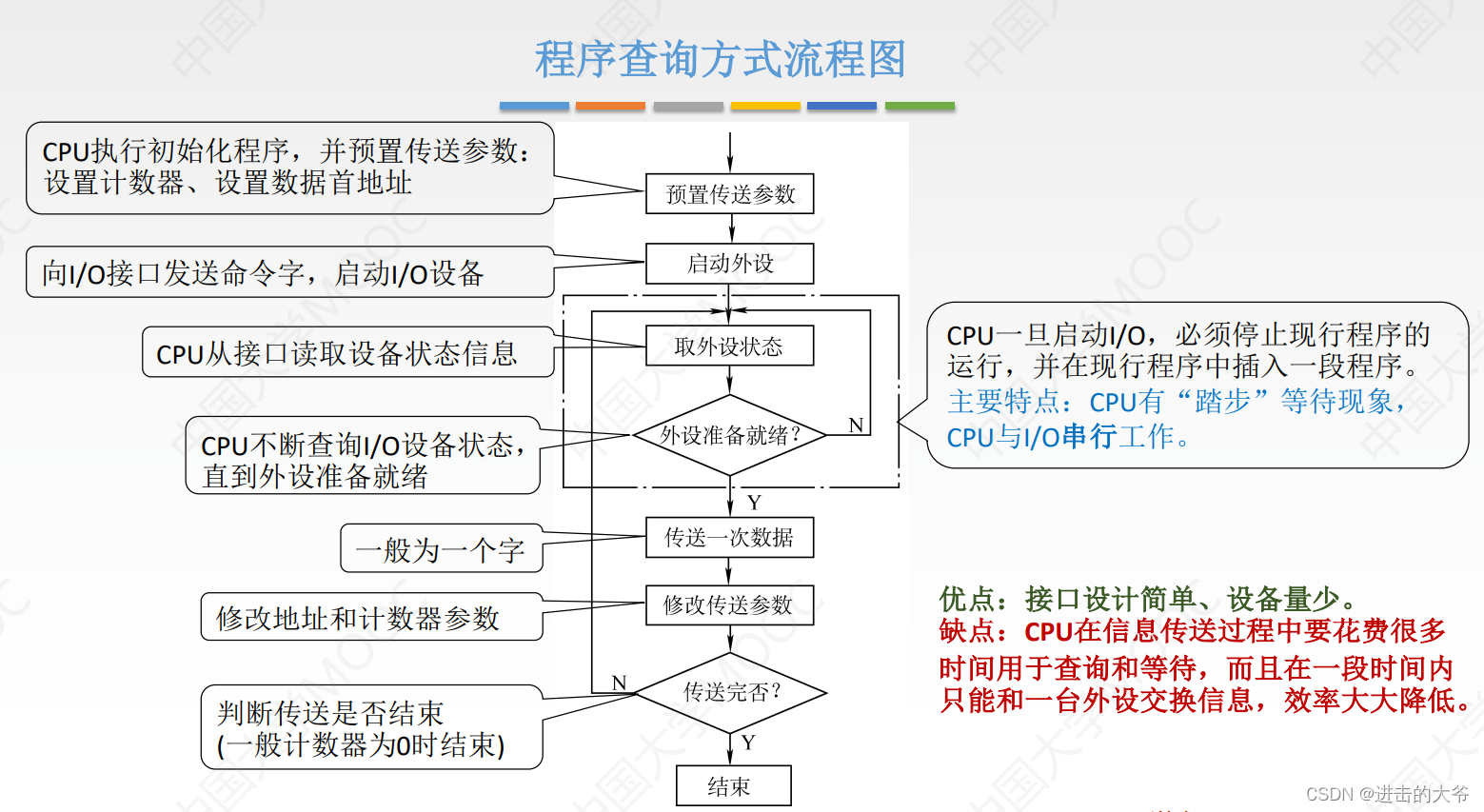

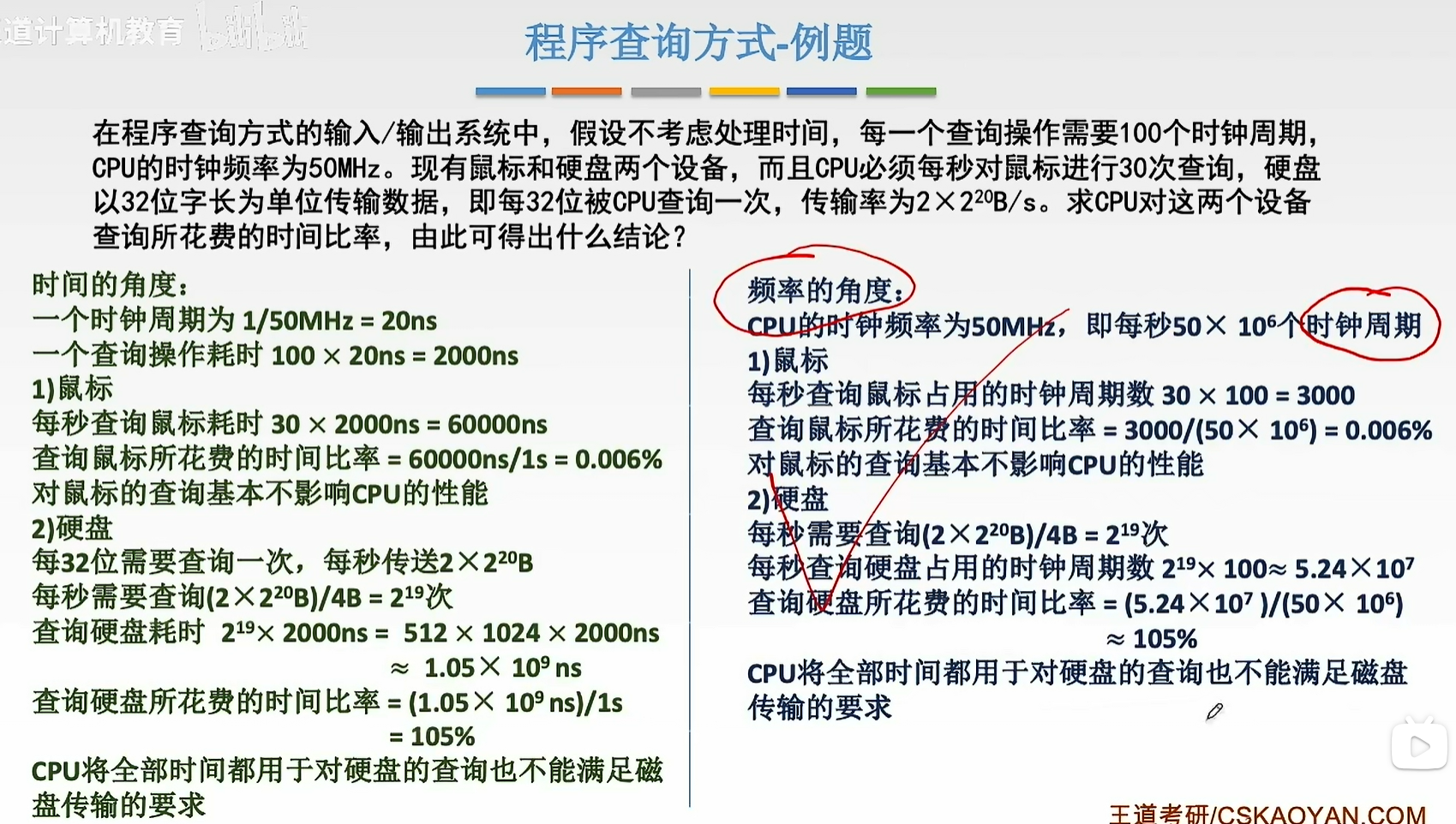

1. 程序查询方式

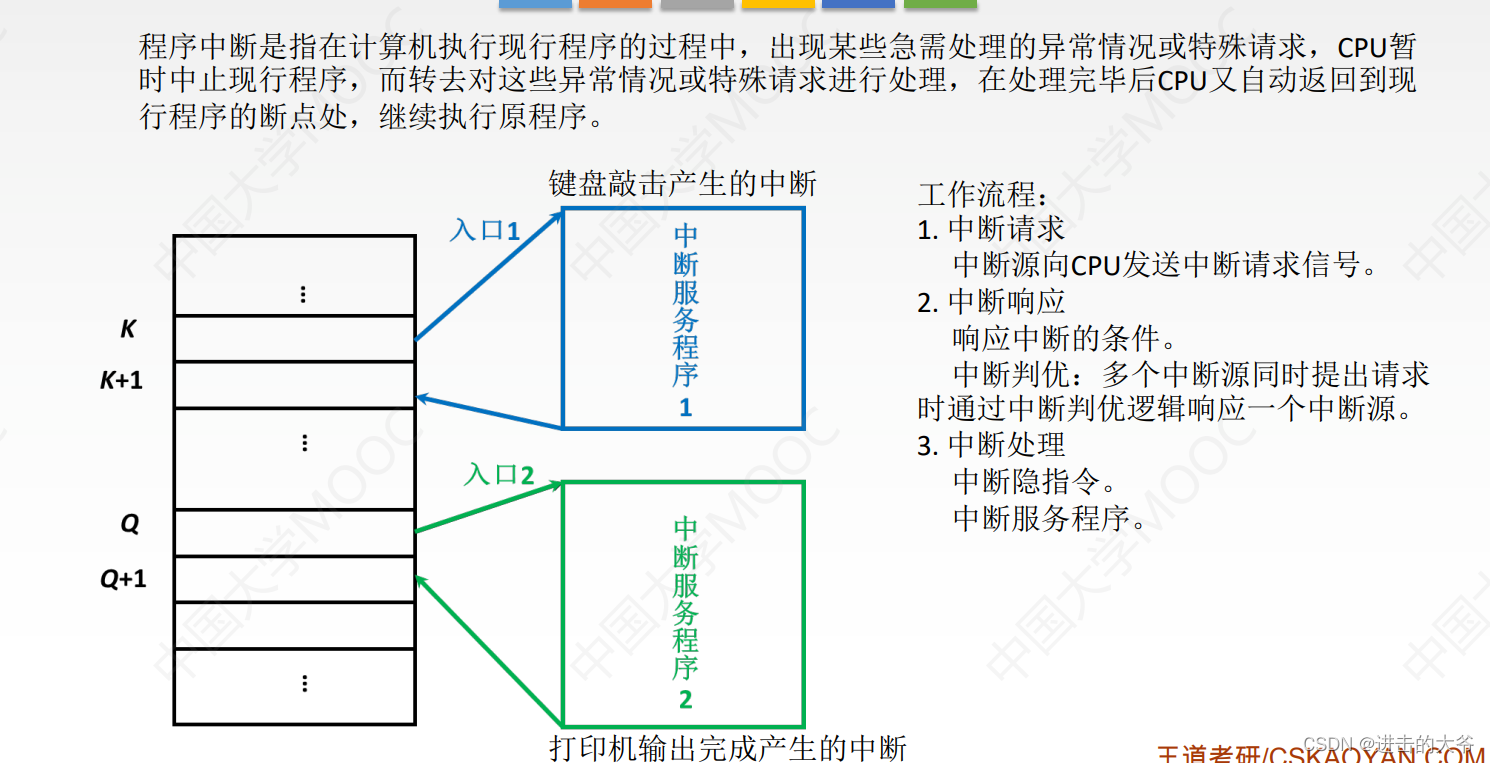

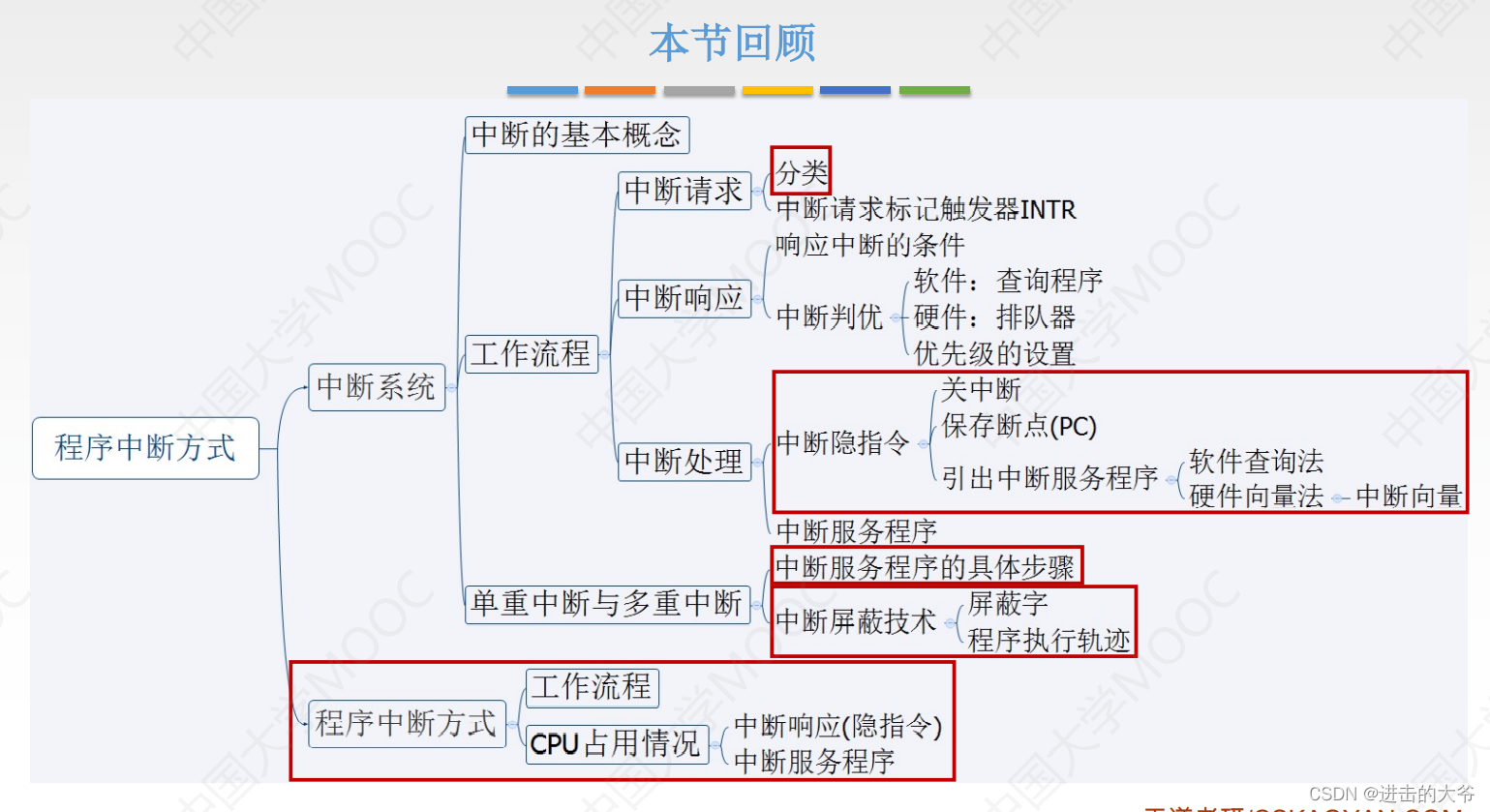

2. 中断的作用和原理

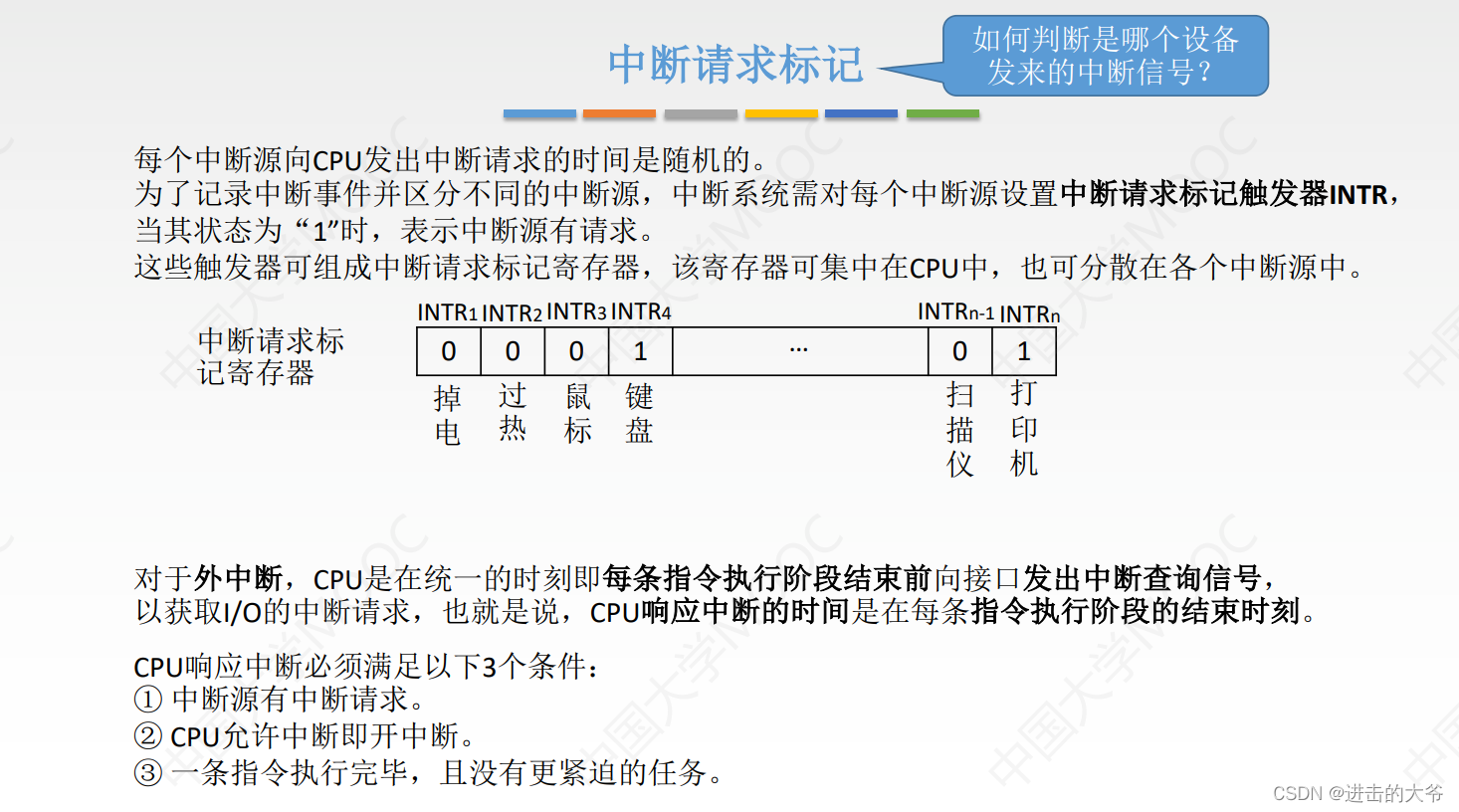

1.CPU响应中断的三个条件:中断源有中断请求、CPU允许中断以及开中断、一条指令执行完毕并且没有更紧迫的任务

(开中断时,CPU只要检测到中断请求就进行中断响应,不管多重还是单重)

2.中断服务程序一般是操作系统模块

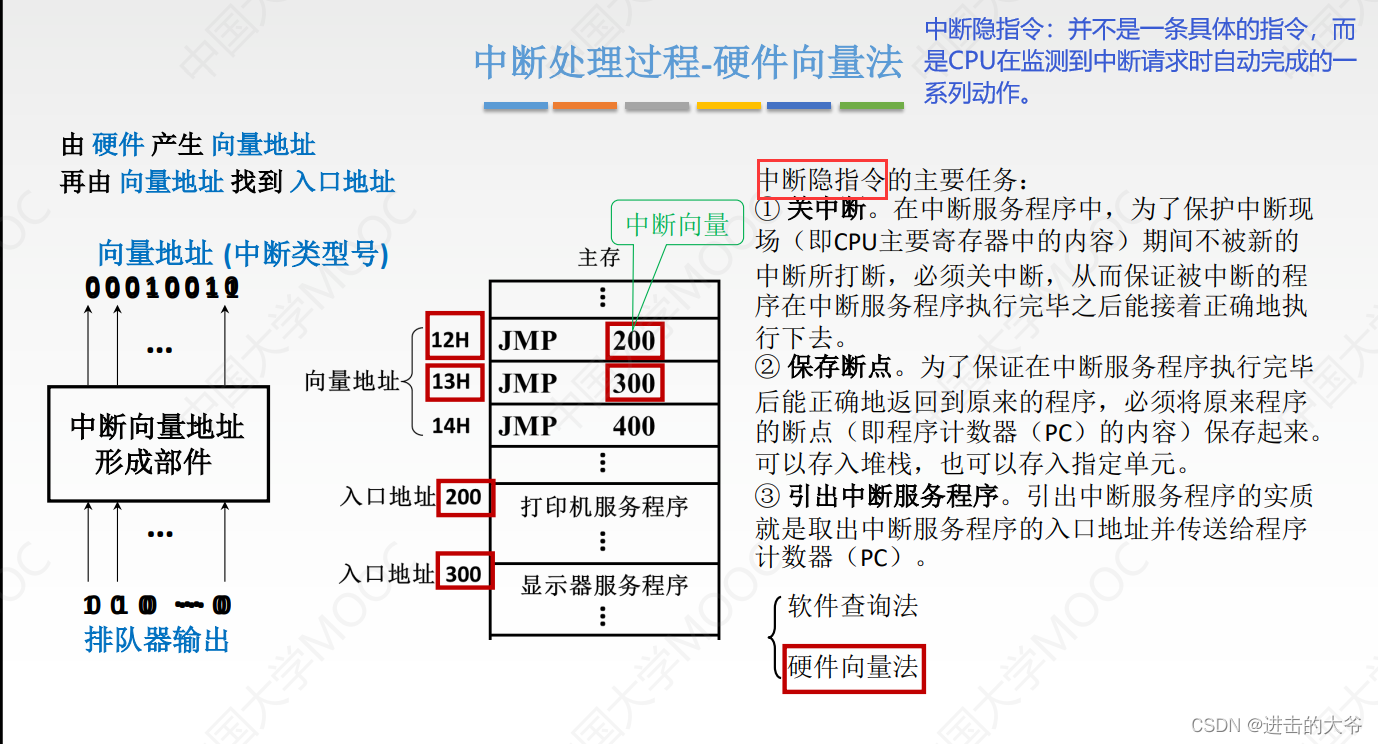

3.中断向量方法可提高中断源的识别速度

4.中断向量地址是内存中存放中断向量的地址,也就是中断服务程序入口地址的地址,也就是说中断向量其实是中断服务程序入口地址

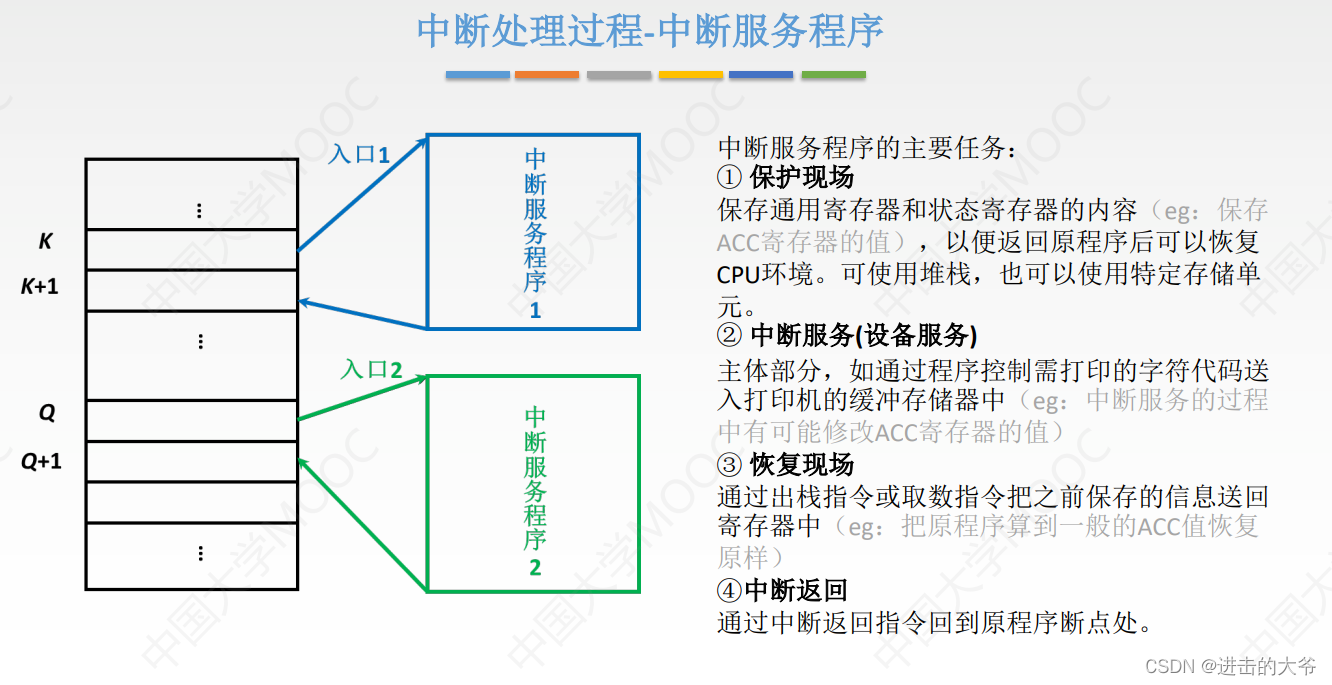

5.中断服务程序最后的指令是中断返回指令,不是无条件转移指令。不同的地方在于,不仅要修改PC值,还要恢复现场

6.中断响应的优先级不是由中断屏蔽字决定的,在中断响应阶段之前,CPU根据中断屏蔽字将所有未被屏蔽的中断请求送到硬件电路(或中断查询程序)进行中断响应判优

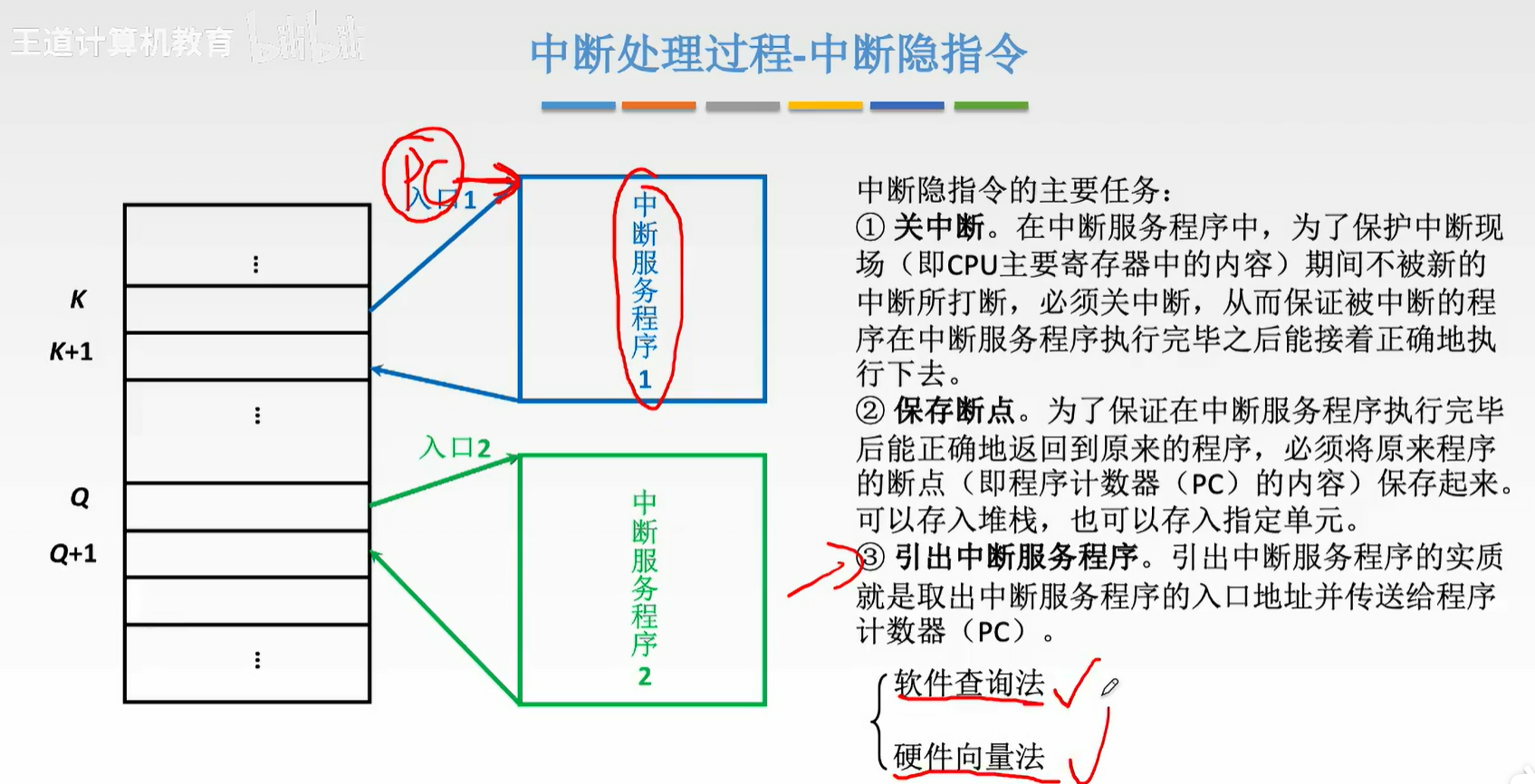

7.在中断响应周期,由中断隐指令将允许中断触发器置0,表示关中断

8.进入中断响应阶段时,CPU一定处于开中断状态(进入响应阶段,说明有请求并且CPU也响应了,那说明还可以收到请求,那说明就是开中断状态)

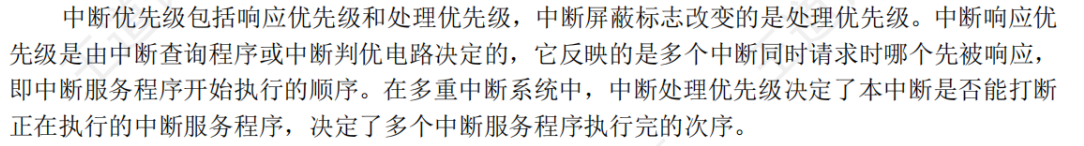

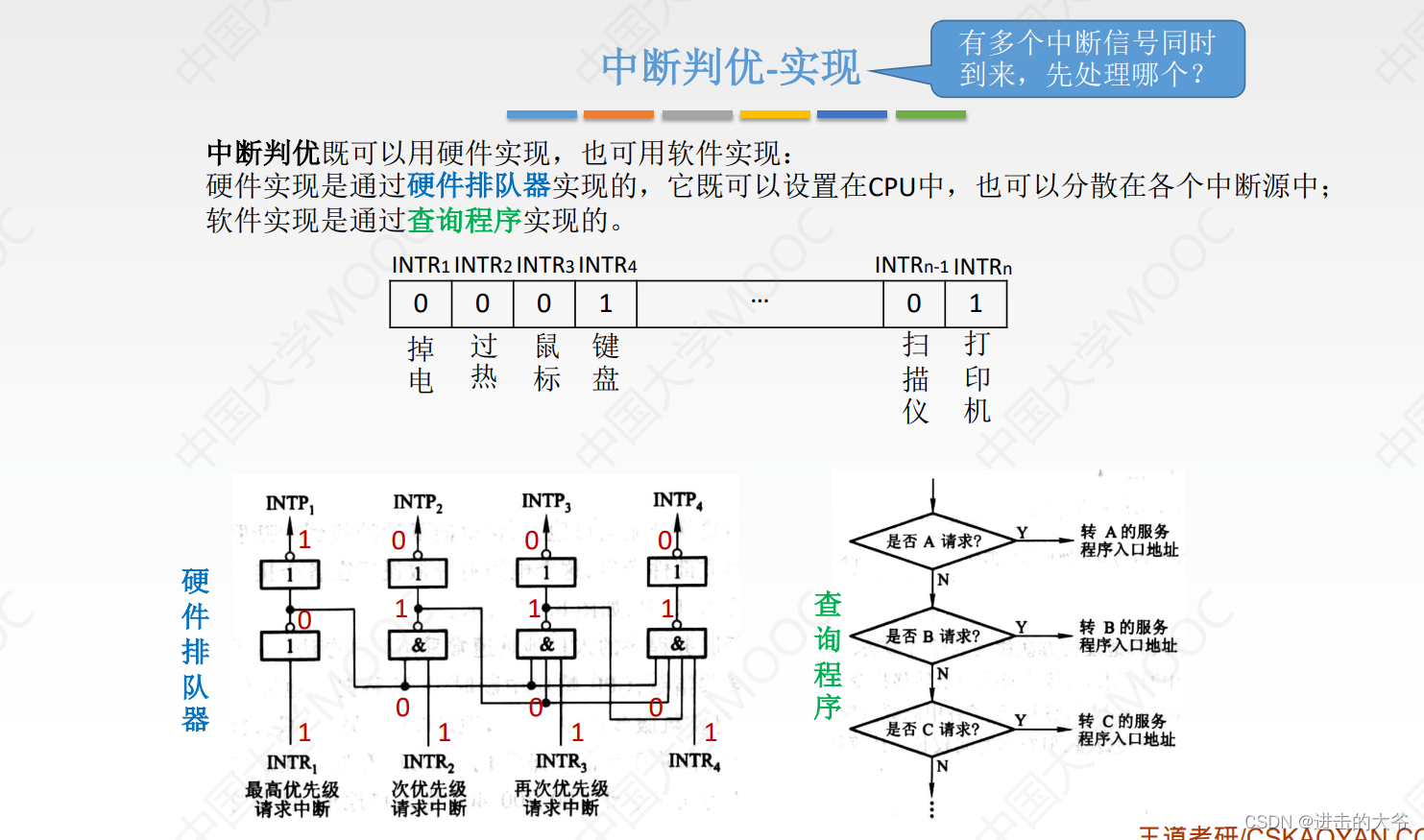

9.中断优先级包括响应优先级和处理优先级,响应优先级由硬件线路或者查询程序的查询顺序确定,不可动态改变,处理优先级由中断屏蔽字确定,可灵活改变

中断的基本概念

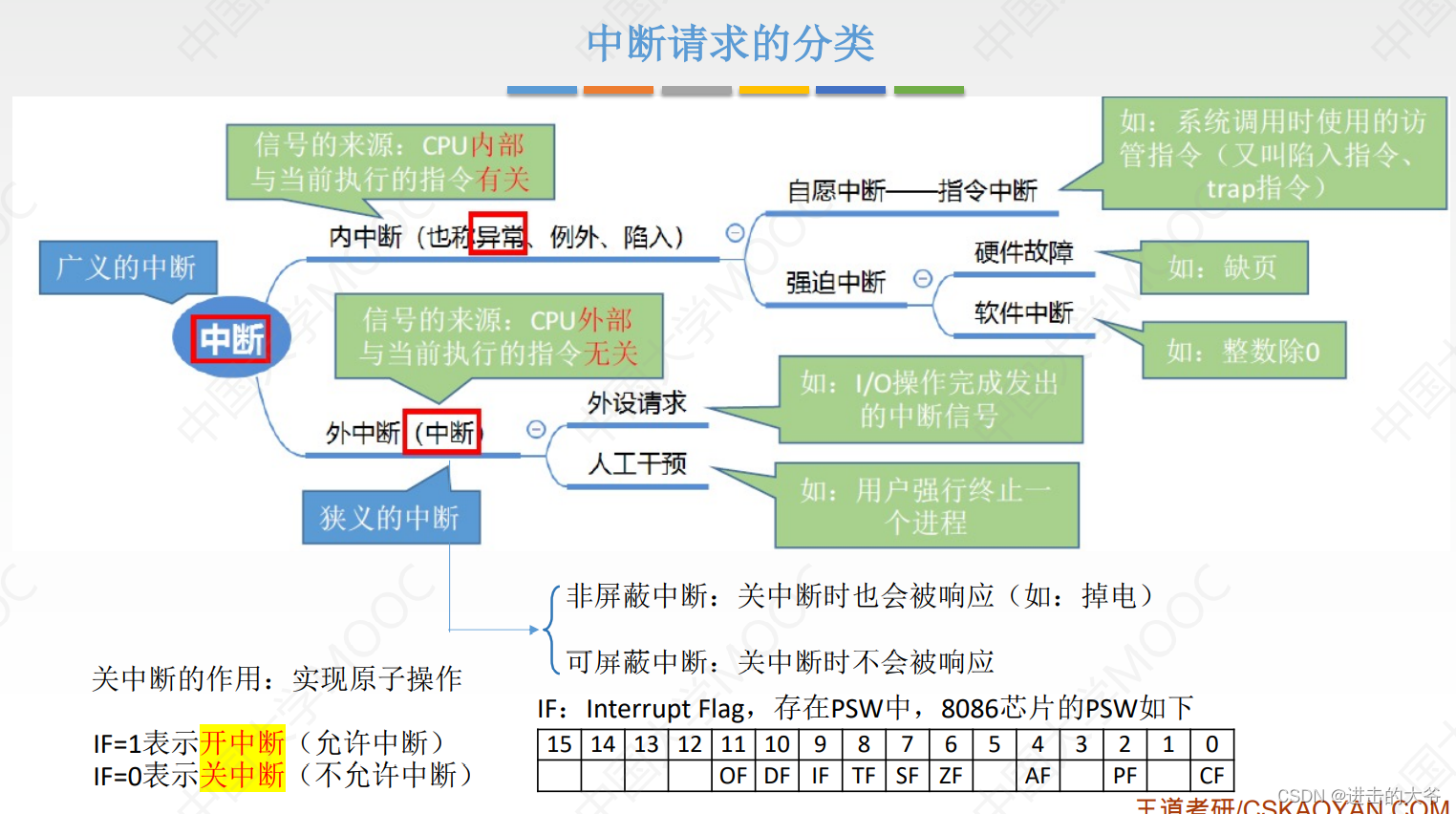

中断请求的分类

中断请求标记

中断判优实现

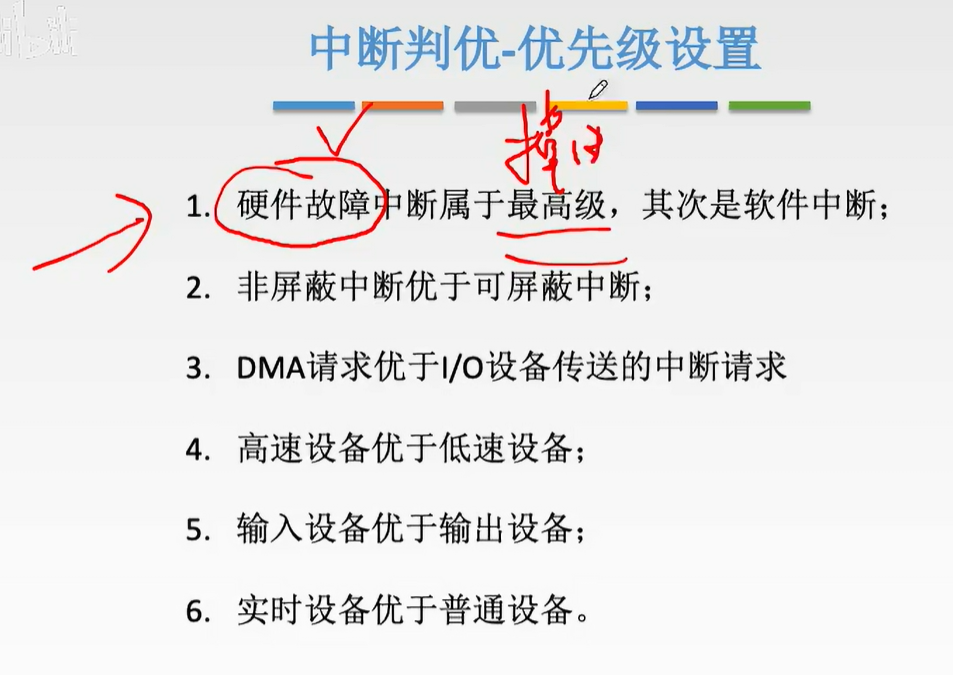

中断判优-优先级设置

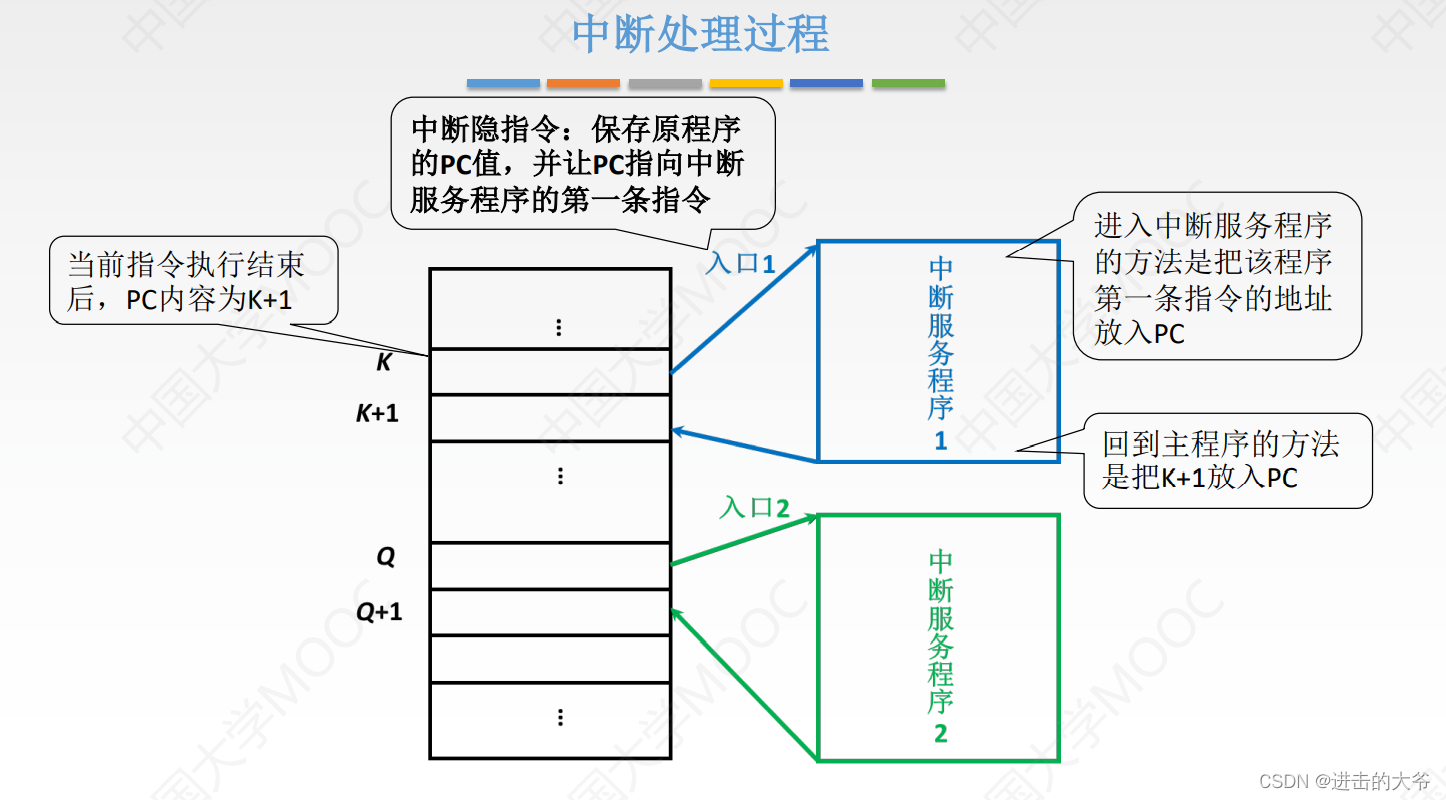

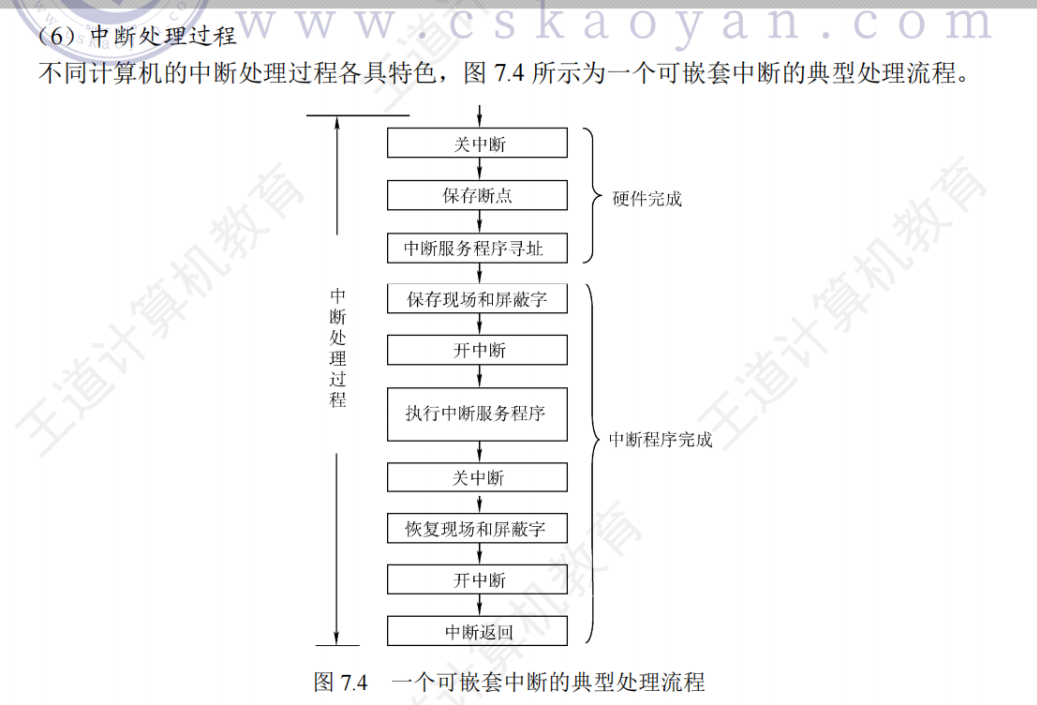

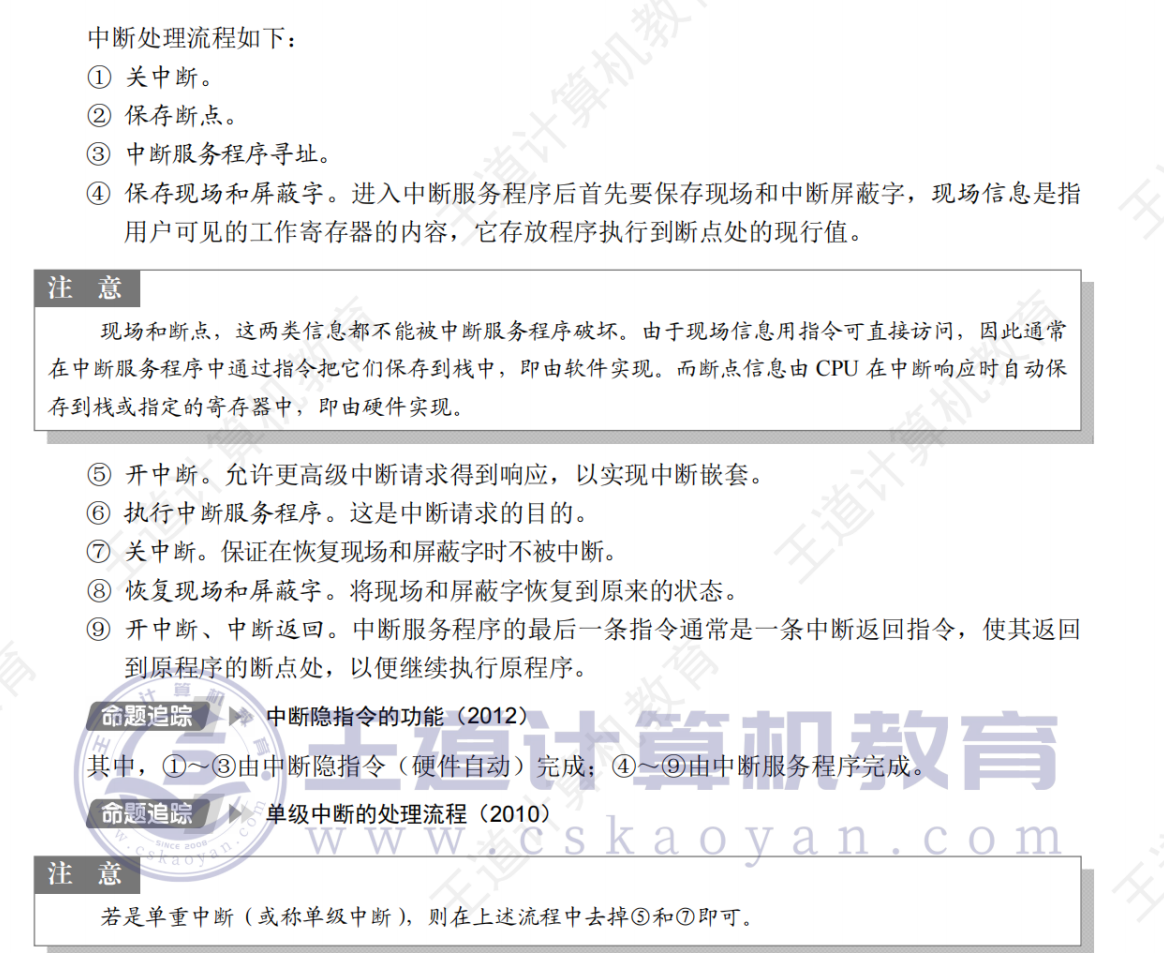

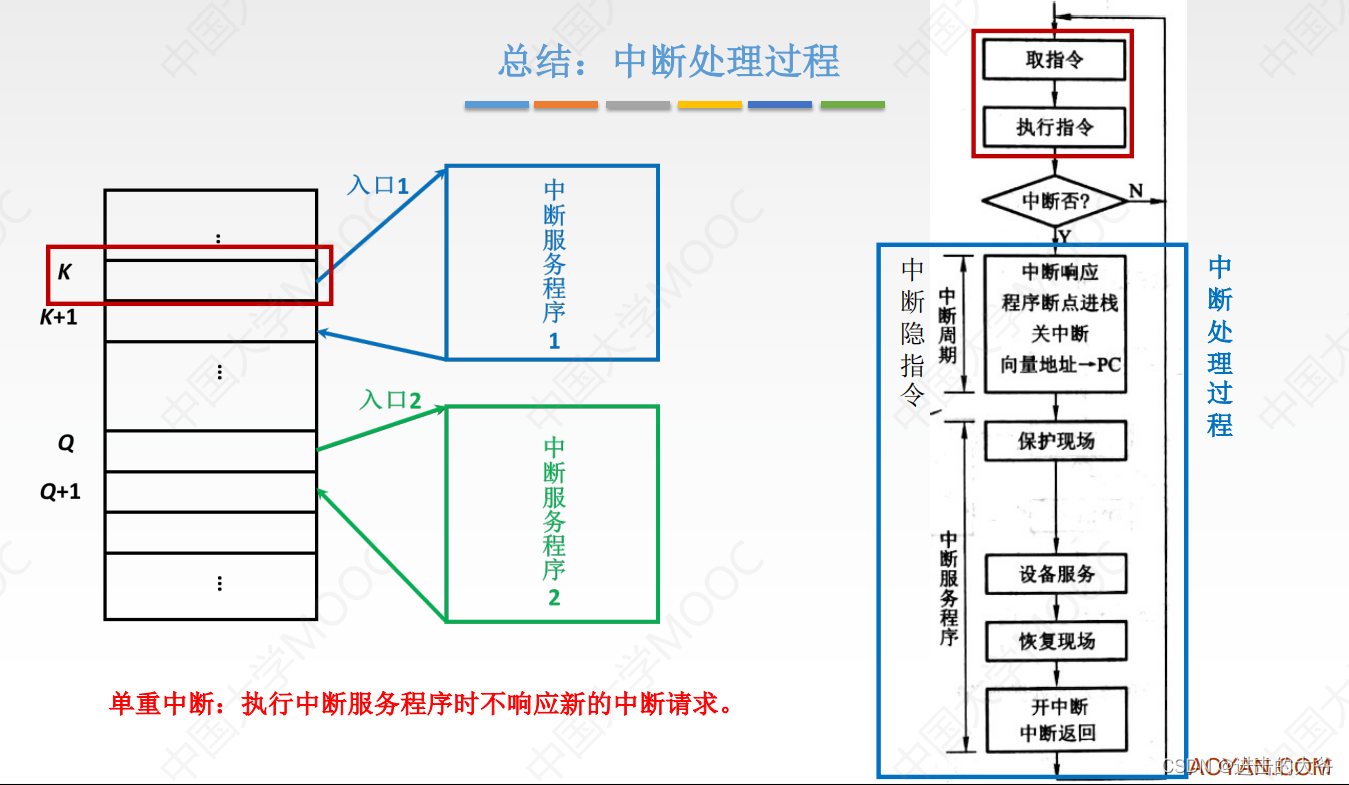

中断处理过程

其实就是排队器选择一个中断后,把结果输入到中断向量地址形成部件,然后映射成向量地址

根据向量地址,我们就可以找到入口地址了

1.中断响应阶段(硬件自动完成)

- 中断请求

- 操作:中断源(外设/定时器/异常)通过物理引脚(如INTR)或内部逻辑发送请求信号,并保持信号直至响应

- 硬件支持:中断控制器(如APIC)管理多源请求的优先级

- 中断响应

- 操作:CPU在当前指令的最后一个时钟周期扫描中断引脚。若中断使能(IF=1)且请求有效,发送应答信号(INTA)

- 关键限制:长指令(如X86 REP MOVS)需执行完毕才响应

- 关闭中断

- 操作:硬件自动清除标志寄存器(EFLAGS)的IF位,屏蔽后续可屏蔽中断,防止现场保护时被抢占

- 例外:不可屏蔽中断(NMI)仍可触发

- 保护断点

- 操作:CPU自动将程序计数器(PC/EIP) 和程序状态字(PSW/EFLAGS) 压入内核栈

- 意义:确保中断返回后能继续执行原指令流。

- 中断源识别

- 操作:通过中断向量号(如0x80为系统调用)查询中断描述符表(IDT),定位中断服务程序入口地址

- 多源处理:共享中断(如PCI设备)需软件二次查询中断控制器状态

2. 中断处理阶段(操作系统/驱动主导)

- 保护现场

- 操作:中断服务程序(ISR)开头用PUSH指令保存通用寄存器(EAX/EBX等)内容到栈中,防止主程序状态被破坏

- 编程责任:由开发者编写保存代码,非硬件自动完成。

- 执行中断服务程序(ISP)

- 上半部(Top Half):

- 立即处理关键操作:读取外设数据寄存器、清除中断标志

- 特点:不可阻塞、不可嵌套(关中断状态下执行)。

- 下半部(Bottom Half):

- 延迟处理耗时操作:网络包处理、磁盘I/O调度

- 实现机制:

softirq:高优先级,多CPU并行执行tasklet:单CPU串行执行- workqueue:可睡眠的线程上下文

- 上半部(Top Half):

- 恢复现场

- 操作:ISP末尾用POP指令从栈中恢复寄存器原值,与保护现场成对出现

3. 中断返回阶段

- 恢复断点

- 操作:执行IRET指令时,硬件自动从栈中弹出PC和PSW值,装载回寄存器

- 原子性:恢复操作不可分割,防止状态不一致。

- 开中断

- 操作:IRET指令隐式恢复标志寄存器(含IF位),重新允许响应中断

- 返回原程序

- 操作:CPU从断点地址继续执行原指令流,中断处理结束

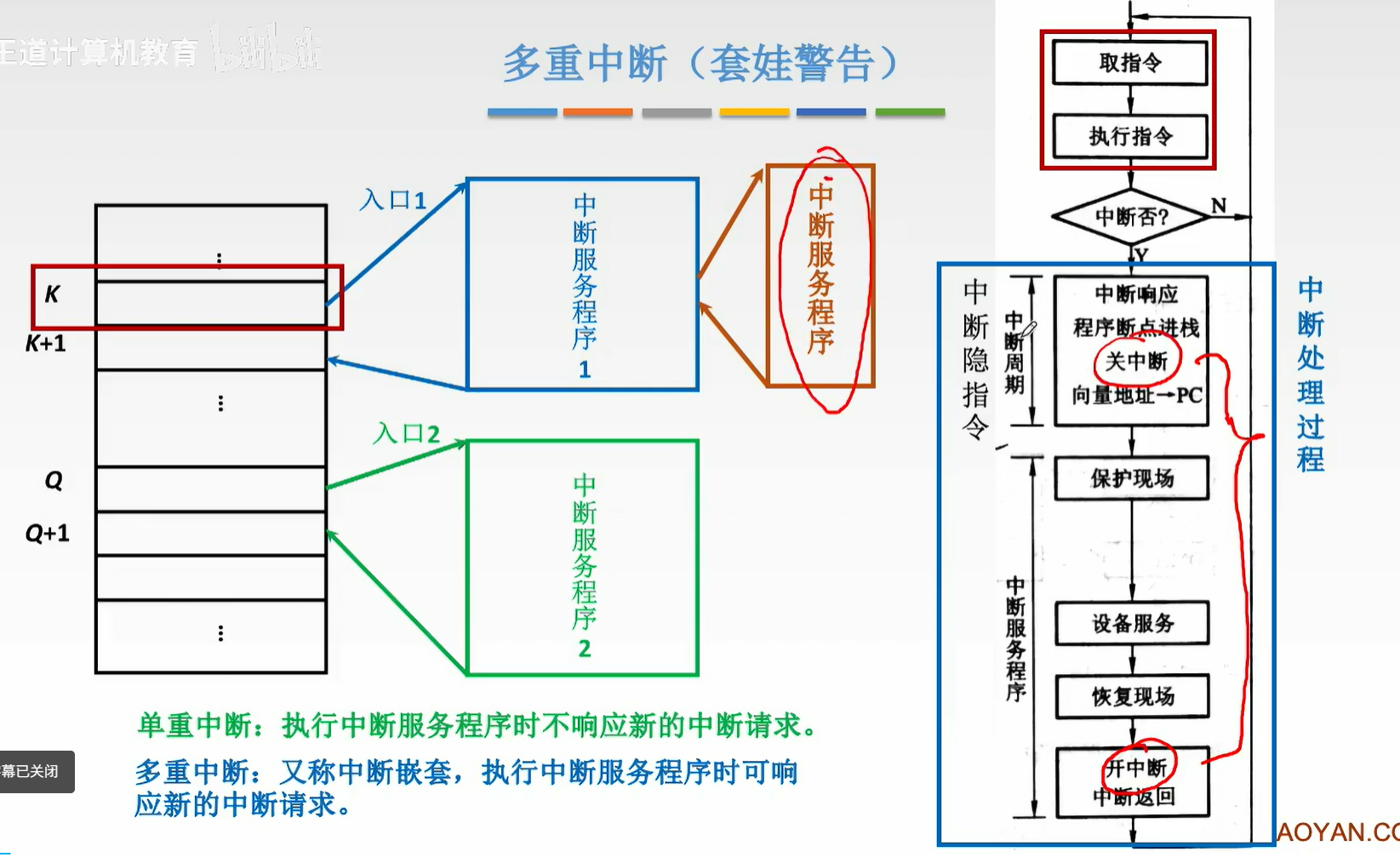

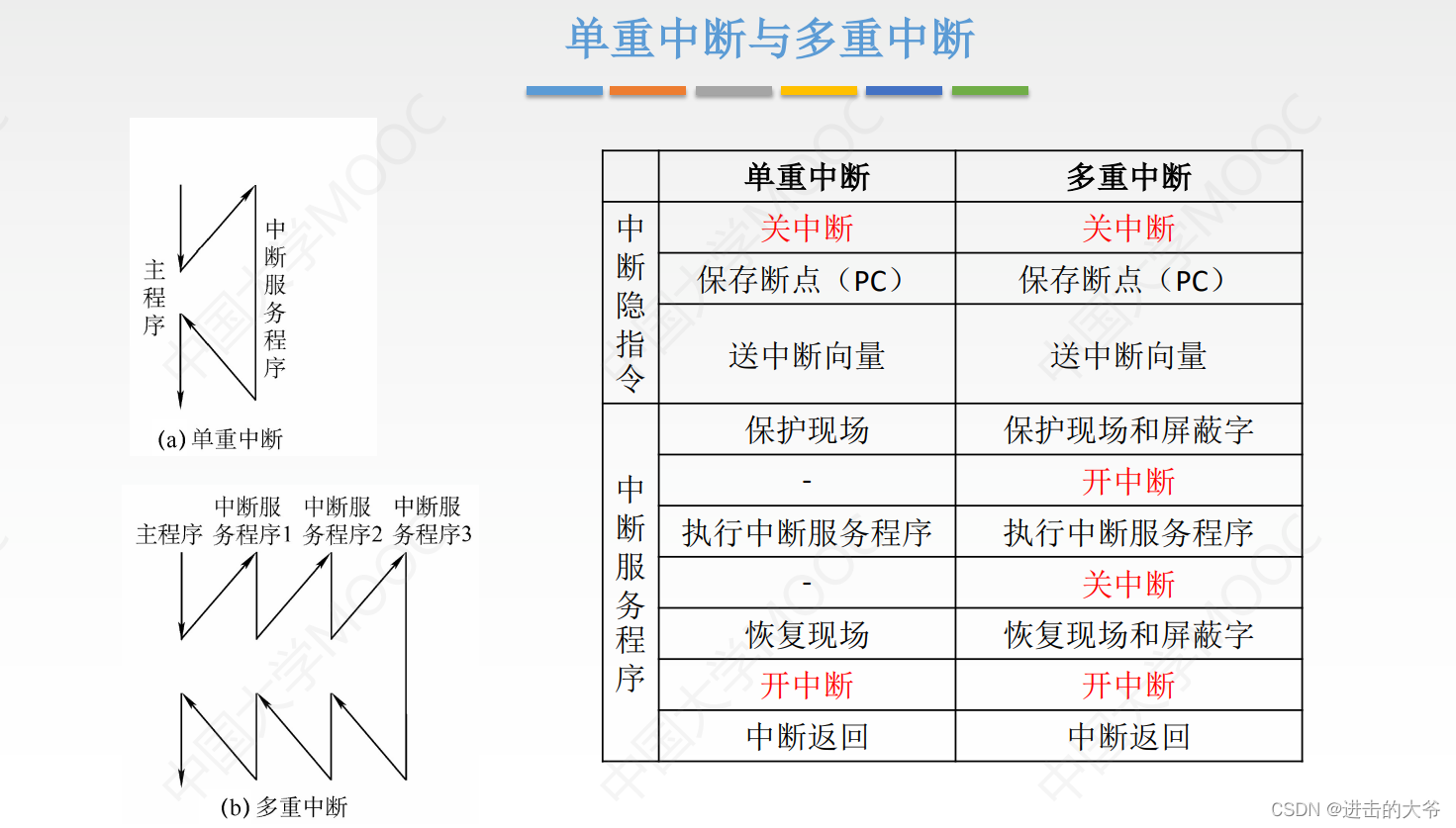

3. 多重中断

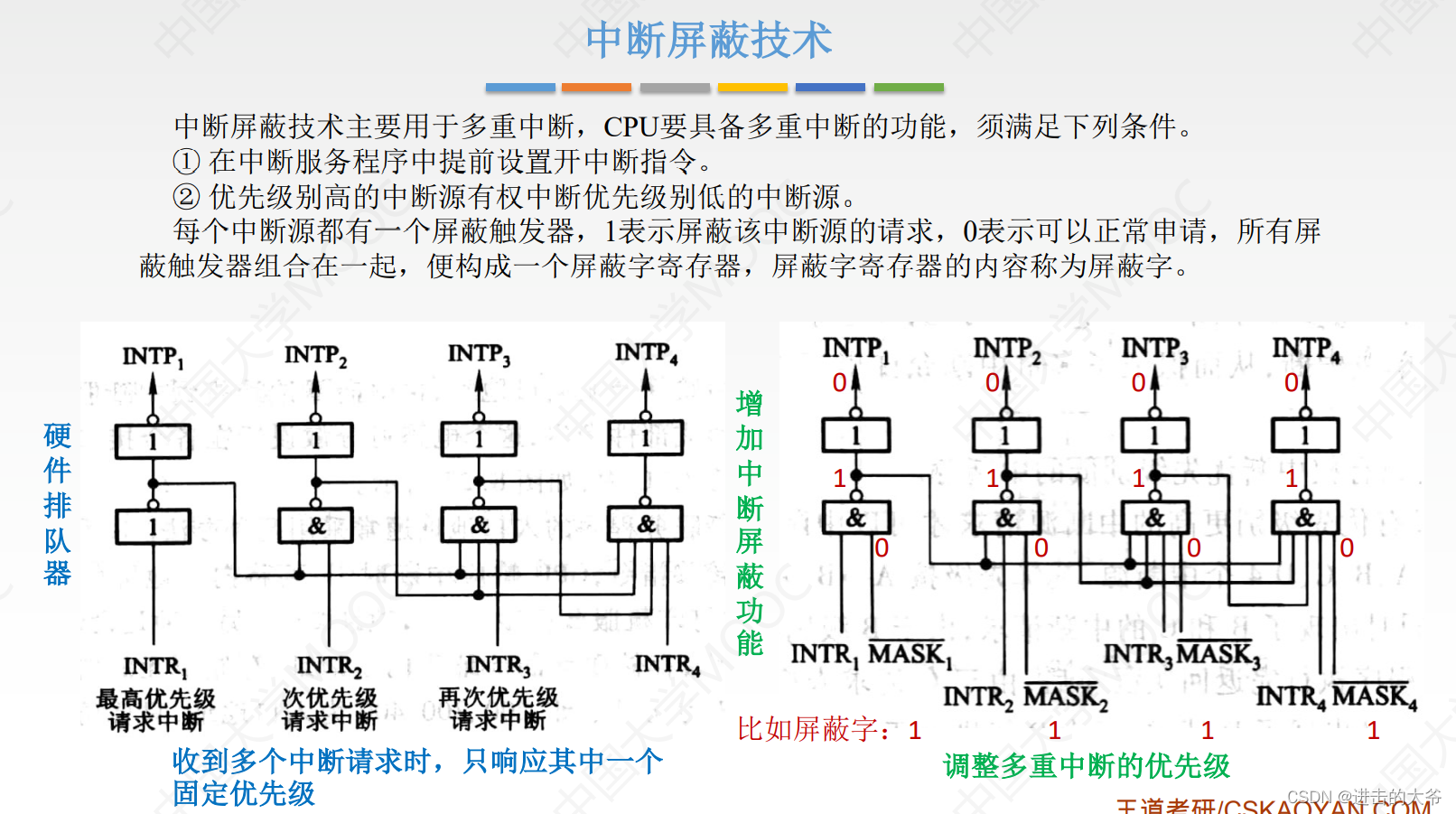

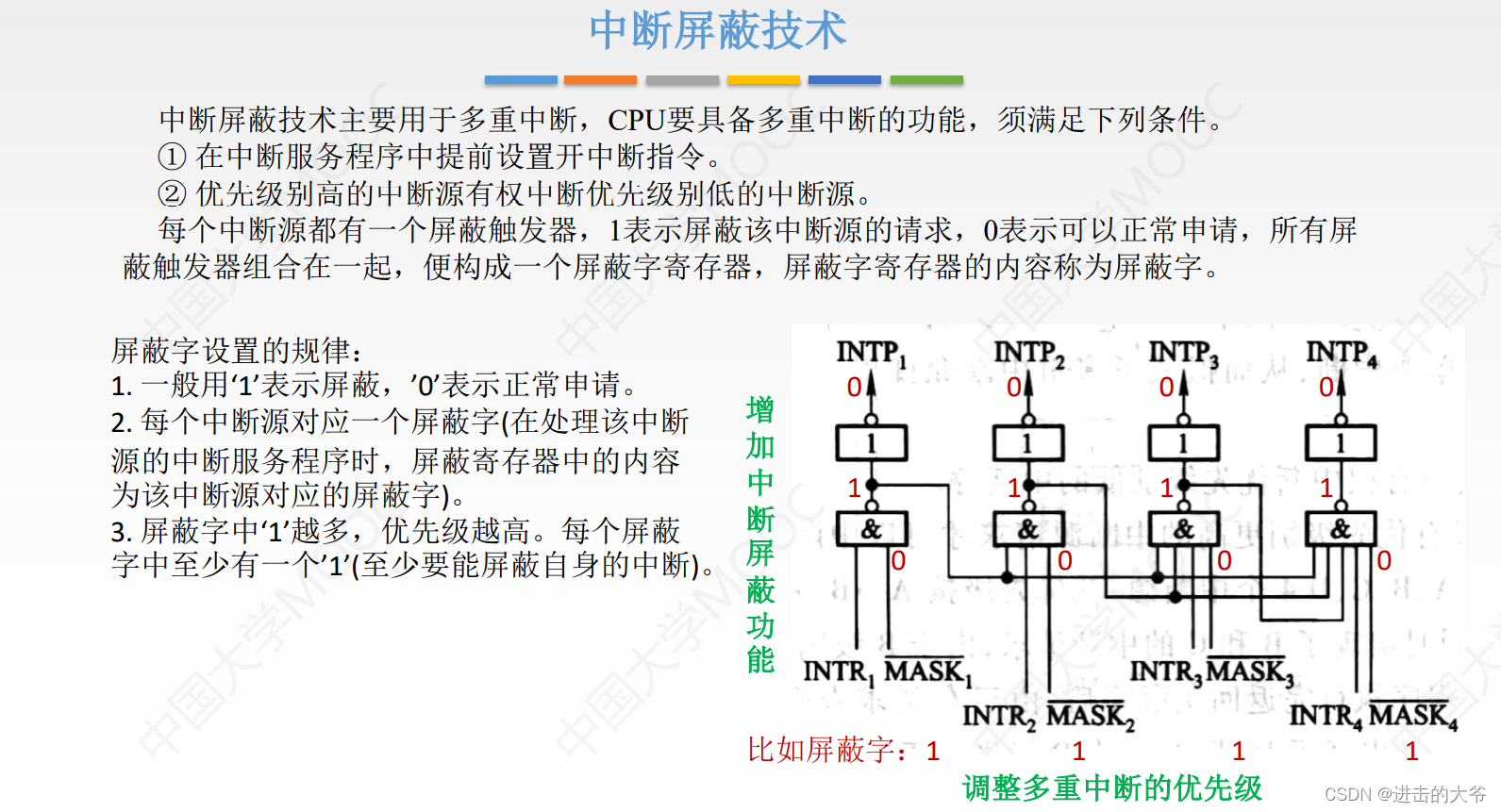

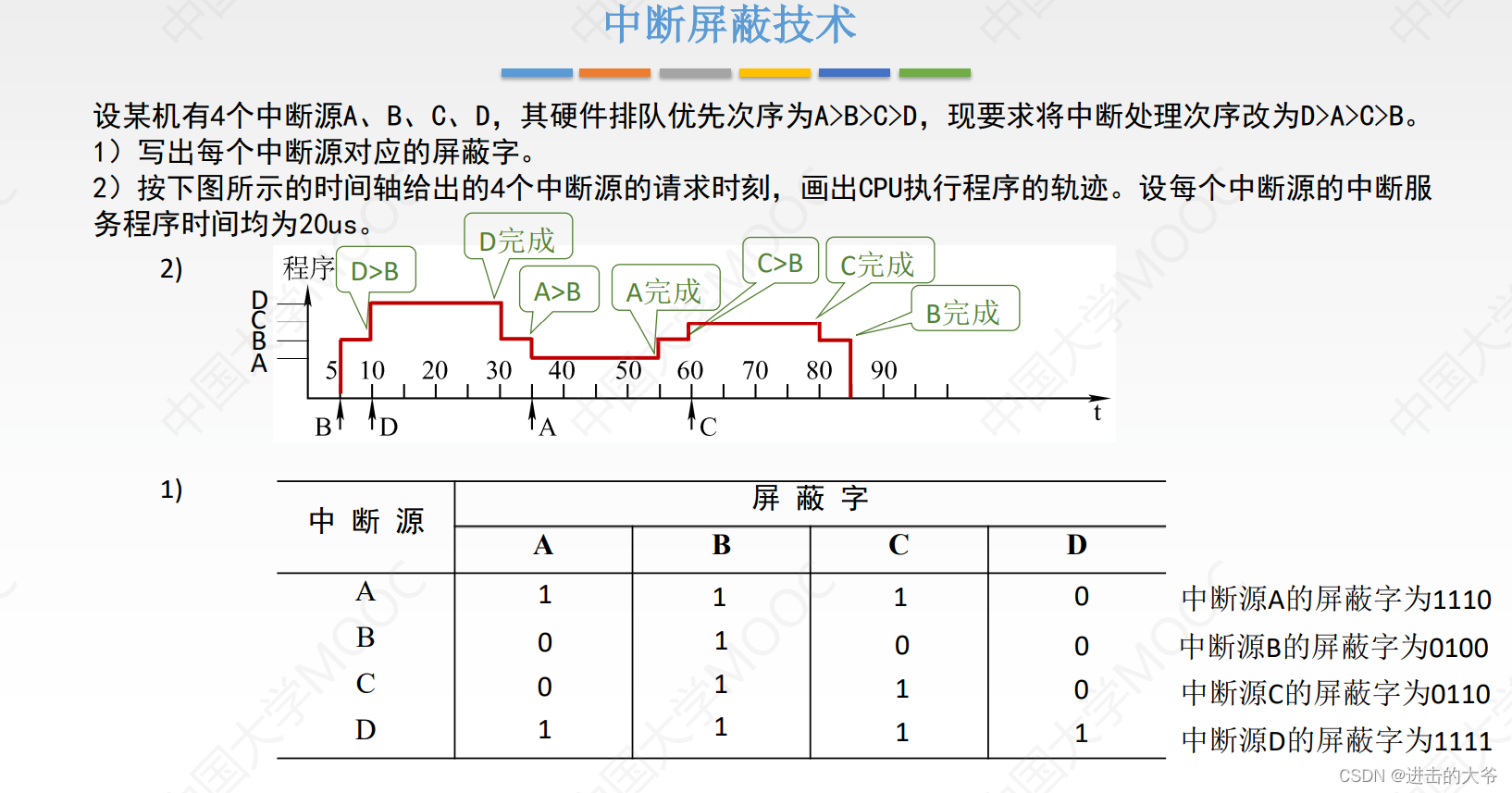

中断屏蔽技术

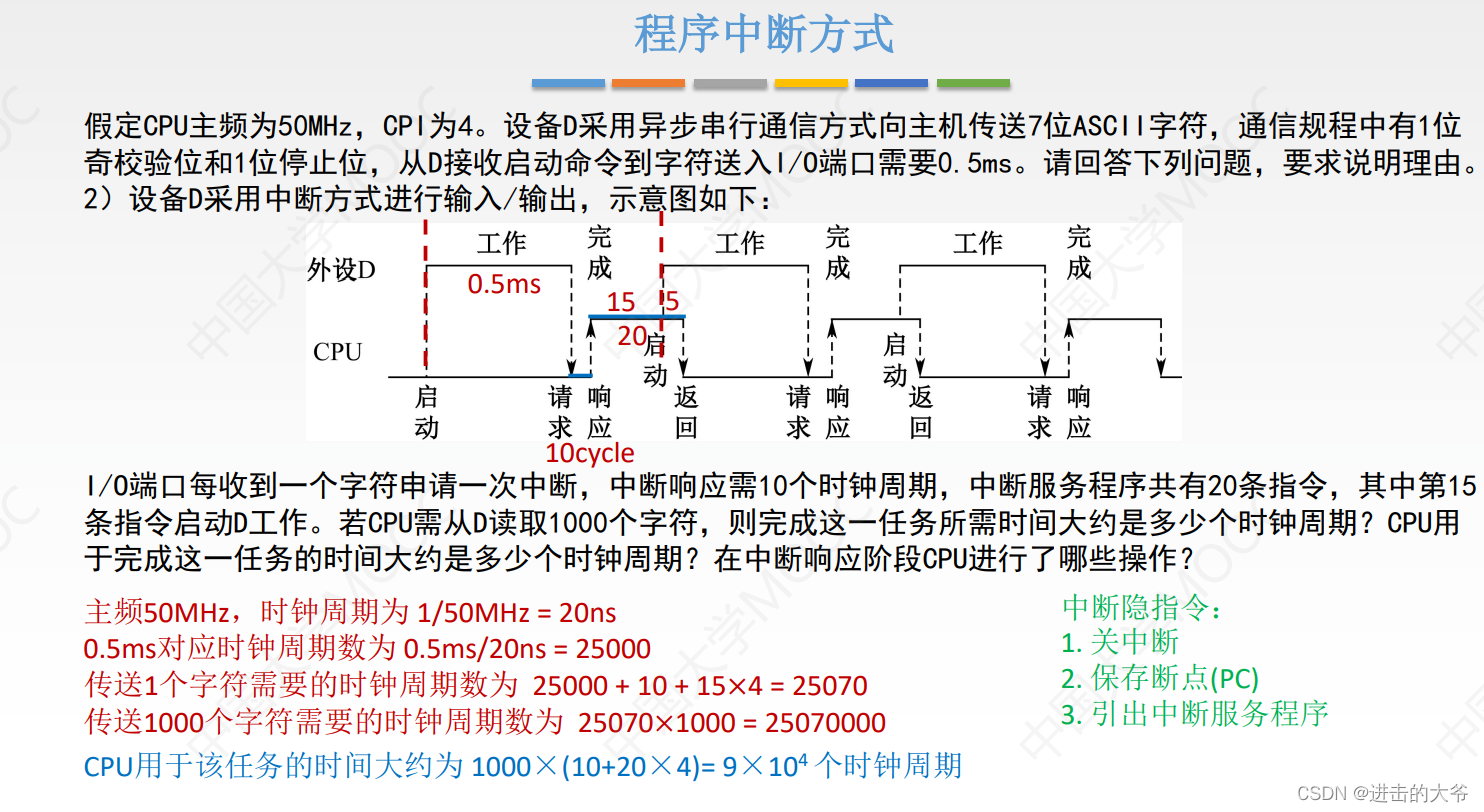

4. 程序中断方式

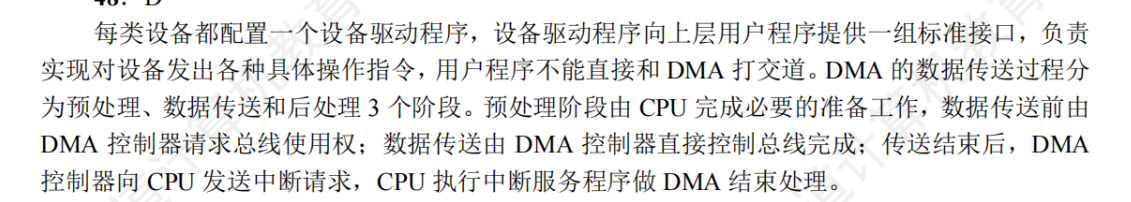

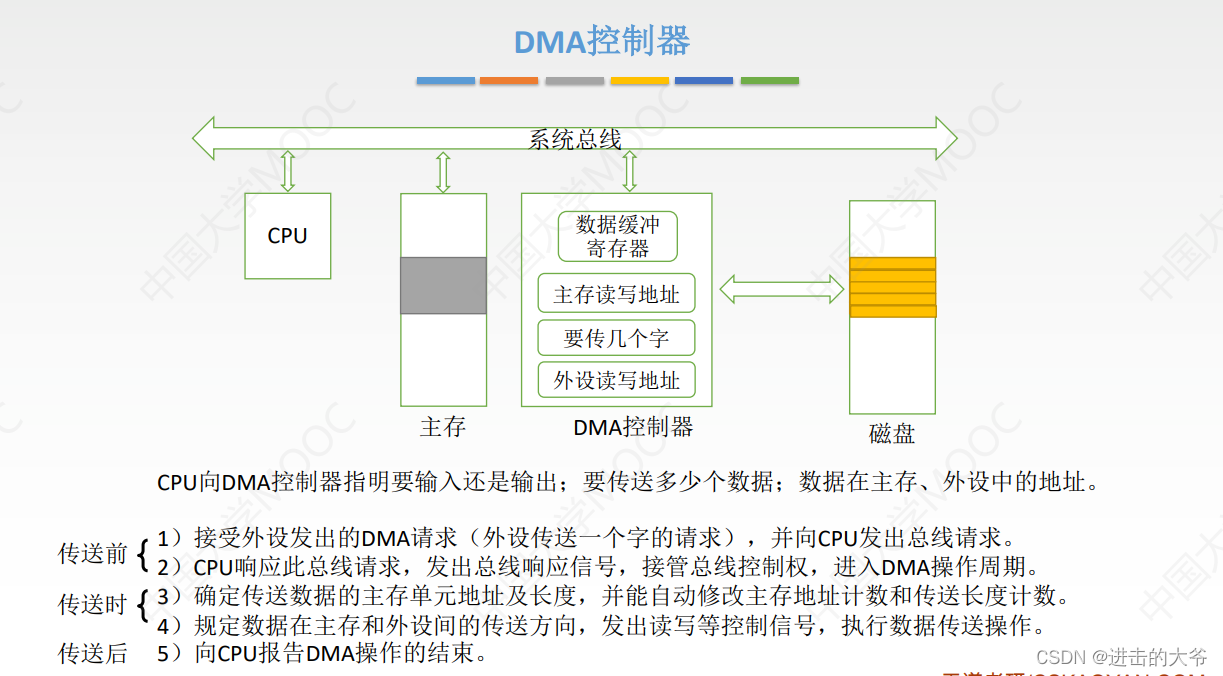

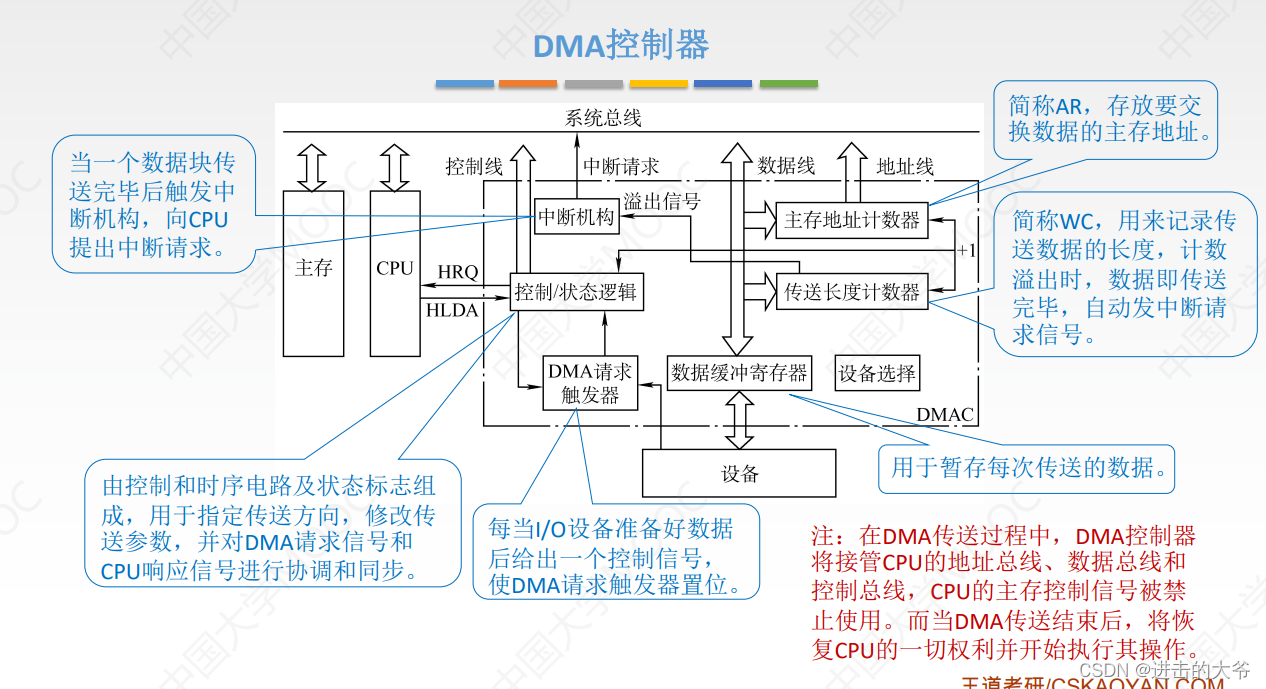

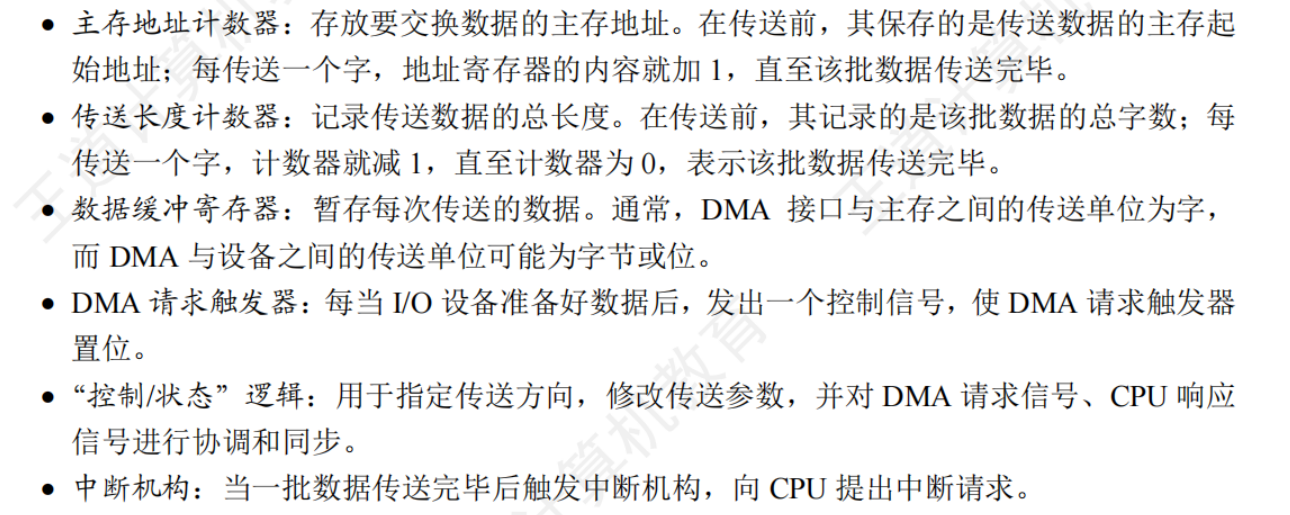

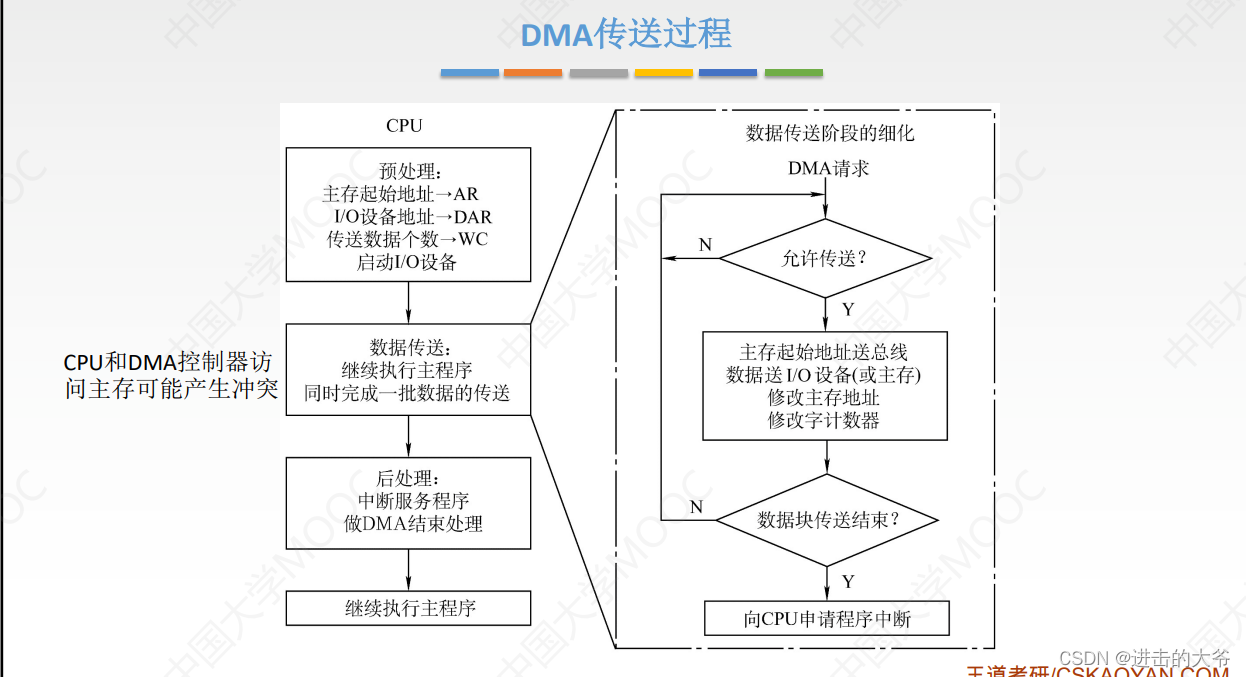

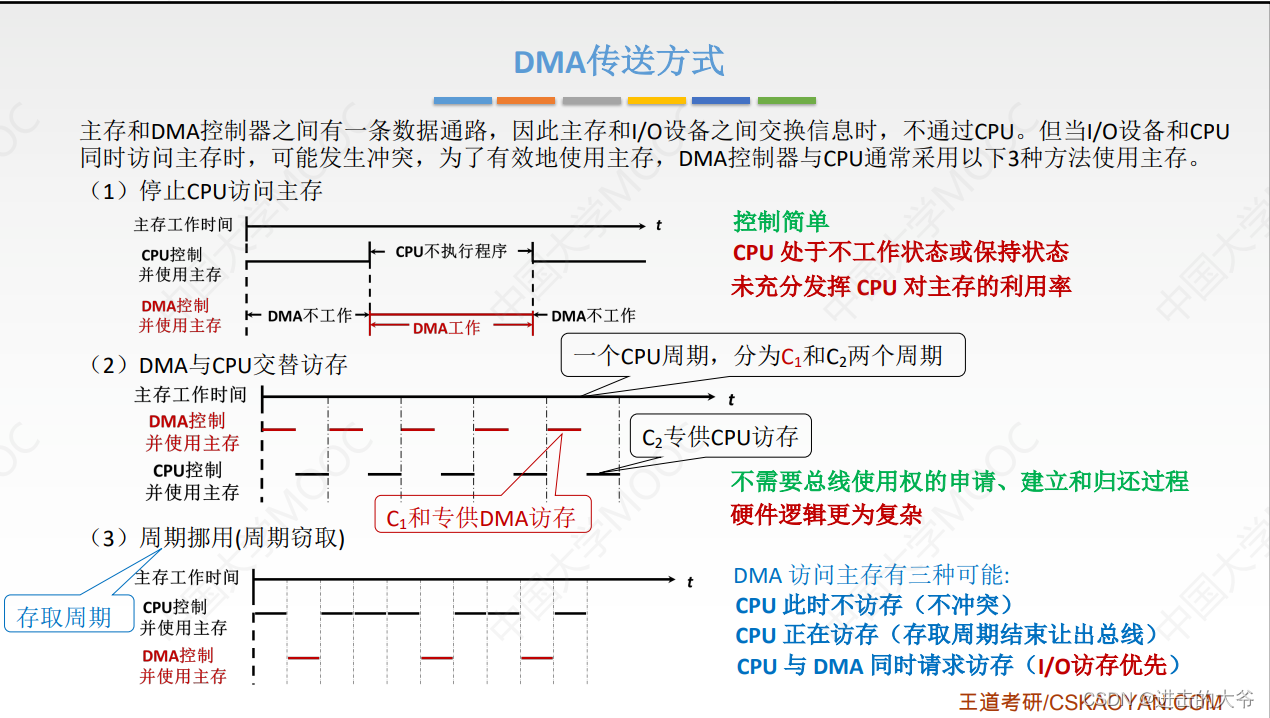

5. DMA方式

CPU会在每个存取周期(总线周期)结束后检查是否有DMA请求,而不是一条指令执行过程的末尾

只有具有DMA接口的设备才能产生DMA请求。否则即使是当前设备是高速设备或者需要与主机批量交换数据,也不能产生DMA请求

程序中断方式每次传输一次数据就得中断一次。

而DMA方式(并且没有DMA总线的情况下)每传输一次数据只需要占用一下系统总线(就是中间空下的那一个存取周期),若CPU此时没有访存操作,即不需要用到系统总线的操作,那么CPU可以执行其他程序,如果CPU有访存操作,即需要用到系统总线的操作,那么会等到DMA控制器用完以后,CPU再用,那就是中间的那个空下的存取周期

如果是三总线结构,即有DMA总线时,都不需要占用系统总线,只需要考虑和CPU是否会同时读写主存的问题,就是后面提到的三种策略

向CPU报告是发出一个中断信号

、

v