技术干货:高速PCB设计避坑指南-从阻抗突变到EMC超标的系统化破解

当PCIe Gen4信号因过孔阻抗突变导致眼图闭合,当DDR4数据组因参考平面切换引发时序紊乱,当EMC辐射因电源谐振超标——这些问题是否正困扰你的高速设计?

本文直击三大核心痛点:

阻抗连续性问题,如HDMI 2.1接口过孔阻抗补偿方案(反焊盘直径≥2倍过孔孔径),实测阻抗波动降至5%;

零缺陷工艺方案,如V-CUT深度控制公式(残留板厚≥0.3mm)、阻焊桥断裂预防准则(宽度≥4mil);

EMC协同设计技巧,在PDN电容矩阵布局“10×法则”与地平面缝合技术(过孔间距λ/10),辐射值直降8dB。

附高速设计和仿真案例,模板分析,助您打通从理论到量产的最后一公里,小白也能快速成为高速硬件设计高手!

问题根源与现象

在>1GHz高速电路(如DDR4/PCIe)中,阻抗不连续是导致信号反射、眼图闭合的核心原因,具体表现:

·过孔阻抗突变(典型值±15%)

·线宽变化(如BGA扇出区域线宽骤减30%)

·参考平面切换(如跨分割地平面)

典型案例如HDMI 2.1接口信号劣化,在某4K视频设备HDMI输出出现雪花噪点问题分析

·问题定位:使用矢量网络分析仪(VNA)测量发现,差分对在连接器过孔处阻抗从90Ω突降至65Ω(图1-阻抗曲线)

·根本原因:过孔反焊盘直径过小(8mil),导致电容效应增强(C≈0.3pF)

系统化解决方案

1. 过孔阻抗补偿设计

·反焊盘优化:

o反焊盘直径 ≥ 过孔直径×2(如8mil过孔需16mil反焊盘)

o阶梯式反焊盘设计(适用于背钻需求,图2-3D结构)

·差分过孔对称布局:

o相邻过孔中心距≥3倍孔径,避免电磁场耦合

2. 线宽渐变过渡设计

·BGA扇出区域:

o采用锥形线宽过渡(线宽变化斜率≤5mil/mm)

o参考IPC-2141标准,使用2D场求解器计算阻抗连续性

3. 参考平面完整性保障

·跨分割处理:

o在信号层与分割平面间添加去耦电容(0.1μF+1nF组合)

o跨分割走线长度限制:L_max ≤ 信号波长/20(如5GHz信号需L<1.5mm)

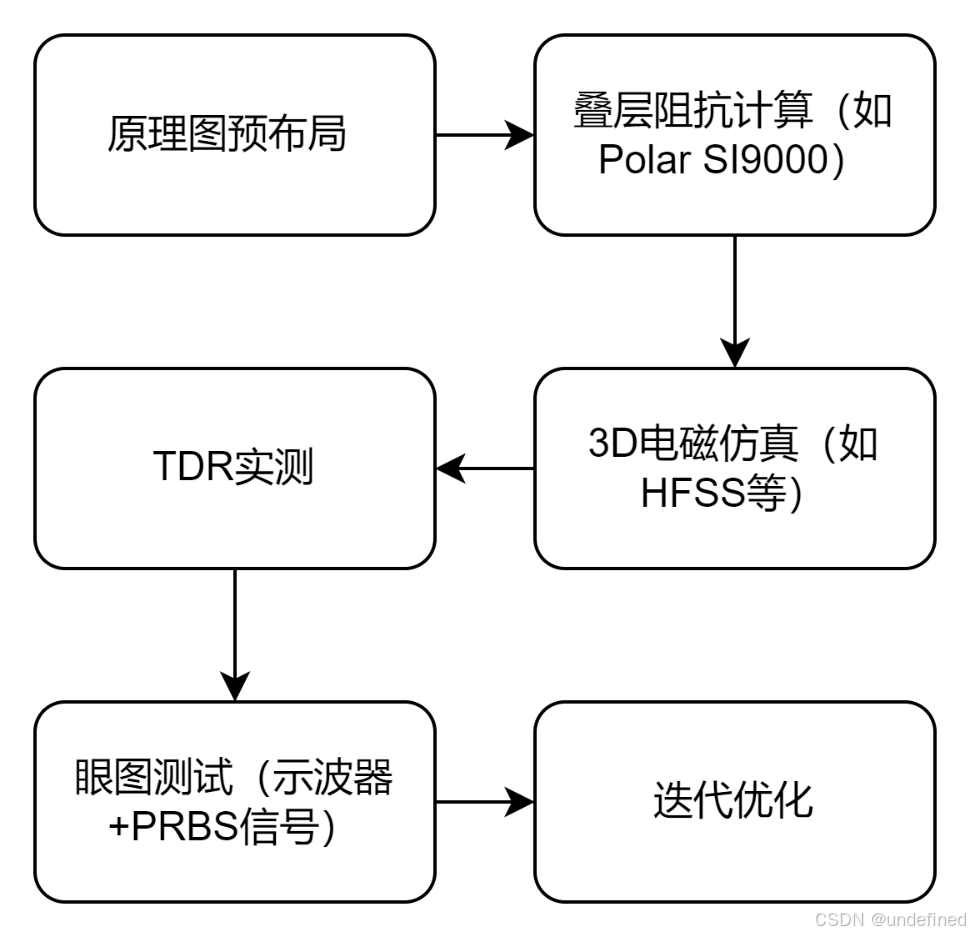

设计验证流程图

关键数据:优化后过孔阻抗波动<5%,眼图张开度提升40%

PCB制造工艺中8大隐形陷阱与零缺陷设计规范

致命陷阱清单与案例分析

深度解析:拼板设计与V-CUT工艺冲突,比如某智能手表PCB批量生产中出现30%板边断裂:

·失效分析具体原因为V-CUT深度设置错误(切入铜层70%,残留板材不足0.2mm)

·设计规范要求:

oV-CUT禁止穿越高密度布线区(如DDR区域)

o拼板邮票孔尺寸:直径1.0mm,间距2.0mm(图4-拼板示意图)

零缺陷设计Checklist

1.DFM硬性规则:

o线距/线宽≥制造商能力极限(如4/4mil)

o阻焊开窗比焊盘大4mil(防焊盘氧化)

2.文件交付规范:

o提供IPC-356网表比对文件

o标注特殊工艺要求(如沉金厚度0.05μm±10%)

案例:EMC与电源完整性协同设计方法论

典型EMC问题链分析思路

传导发射超标↔电源噪声耦合↔地弹效应

某服务器主板PCIe插槽辐射超标6dB:

·根因溯源:

o12V电源层谐振峰(200MHz)通过地平面耦合到时钟线

o地弹电压达120mV(仿真vs实测误差<8%)

三维协同优化策略

1. 电源分配网络(PDN)优化

·电容矩阵设计:

o去耦电容布局遵循"10×法则":

§0.1μF(<1mm到引脚)+10μF(<5cm区域分布)

o谐振频率计算:

fres=12πLvia⋅Cdecouplefres=2πLvia⋅Cdecouple1

(典型值:1nH过孔+10μF电容→谐振点1.6MHz)

2. 地平面分割与缝合技术

·跨分割区域处理:

o每100mil添加接地过孔(孔径8mil,间距200mil)

o使用嵌入式电容材料(ZBC2000,容值50nF/in²)

3. 辐射热点抑制

·辐射的屏蔽法:

o在高速信号线两侧布置接地铜柱阵列(间距λ/10)

o结合吸波材料(如TDK铁氧体片)降低腔体谐振

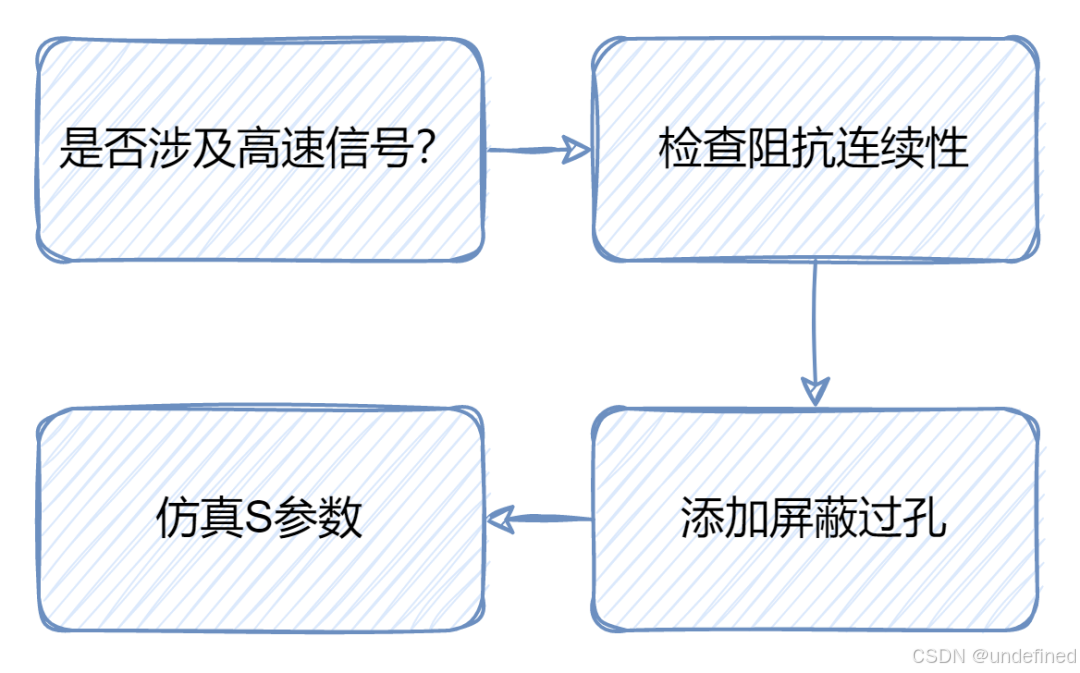

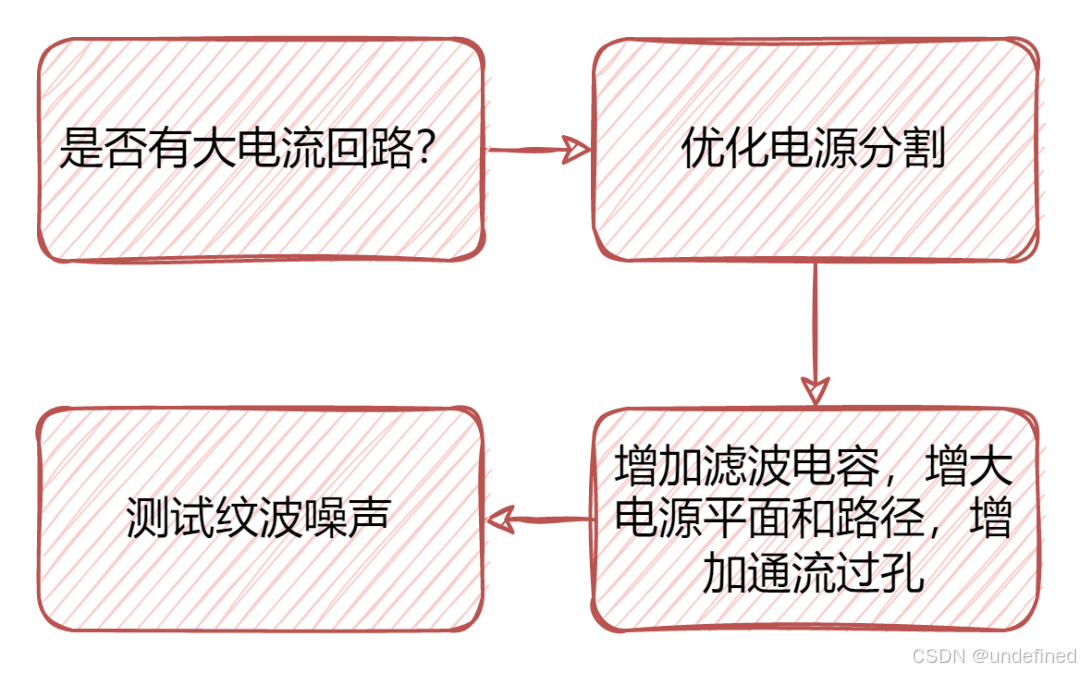

EMC设计决策树

敏感高速信号的处理方法

电源的处理方案

扩展应用建议

1.工具链组合:

o仿真:Cadence Sigrity(电源完整性)+ANSYS HFSS(3D电磁场)

oDFM检查:Valor NPI + 华秋DFM

2.实测验证:

o使用近场探头定位辐射源(如R&S ESRP)

oTDR测量分辨率需≤10ps(如Keysight DCA-X)