DSP——时钟树讲解

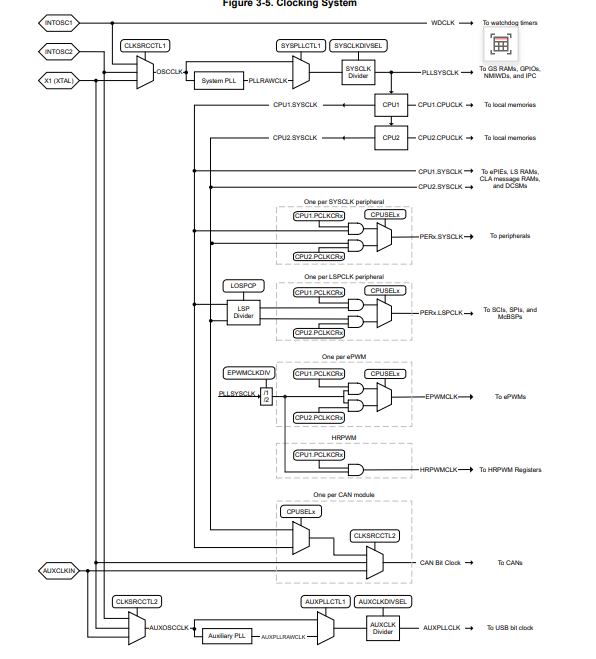

配置任何外设的第一步都要看一下时钟树,下图是DSP28377的时钟树:

由图所示DSP28377由4个时钟源,分别是INTOSC1、INTOSC2、XTAL、AUXCL

INTOSC1:0M内部系统时钟,备用时钟,检测到系统时钟缺失自动连接到备用时钟,也作为看门狗时钟使用;

INTOSC2:10M内部系统时钟,复位时默认的系统时钟,可做boot引导;

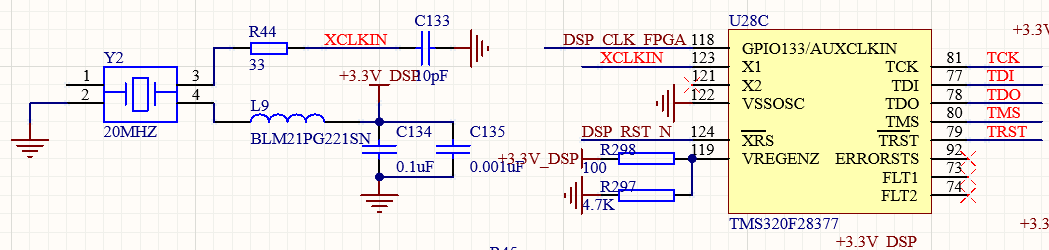

XTAL:外部时钟源,接X1、X2的外部晶振,我的这个电路时接的一个20M的外部晶振

AUXCL:辅助时钟源,可以做CAN和USB使用。

时钟树讲解

CLKSRCCTL1寄存器从INTOSC1、INTOSC2、XTAL中选择一个主时钟就是OSCCLK,OSCCLK经过System PLL输出的时钟为PLLRAWCLK,SYSPLLCTL1寄存器选择OSCCLK或PLLRAWCLK经过SYSCLKDIVSEL调整输出的就是PLLSYSCLK,28377D是双核结构,每个CPU都有自己的时钟也就是CPUCLK,每个CPU的CPUCLK都和自己的PLLSYSCLK相同,但在CPU进入空闲、待机或停止模式时对应的CPUCLK会在低功耗模式下关闭,每个CPUSYSCLK也和PLLSYSCLK一致。

InitSysPll(XTAL_OSC,IMULT_20,FMULT_0,PLLCLK_BY_2);依据手册给出的公式:

fPLLSYSCLK = fOSCCLK * (SYSPLLMULT.IMULT + SYSPLLMULT.FMULT) / SYSCLKDIVSEL.PLLSYSCLKDIV

代入:

CPU1SYSCLK = PLLSYSCLK = 20MHz(XTAL_OSC) * 20 (IMULT) * 1 (FMULT) / 2 (PLLCLK_BY_2) = 200MHz