微机原理与接口技术,期末冲刺复习资料(五)

接续上文:微机原理与接口技术,期末冲刺复习资料(四)-CSDN博客

点关注不迷路哟。你的点赞、收藏,一键三连,是我持续更新的动力哟!!!

持续关注我~~~主页,查看更多内容哟(希望你能在这里有所收获🤭)。点关注,不迷路,哈哈哈!~~~

主页:一位搞嵌入式的 genius-CSDN博客![]() https://blog.csdn.net/m0_73589512?spm=1000.2115.3001.5343

https://blog.csdn.net/m0_73589512?spm=1000.2115.3001.5343

目录

6. 输入输出和中断系统

6.1 基本概念

6.2 简单接口电路

6.3 基本输入/输出方法

6.4 中断技术

6.4.1 中断的基本概念

6.4.2 中断类型

6.4.3 中断向量表

6.4.4 8088/8086中断系统

6.5 8088内部中断与NMI中断

6.6 中断控制器 8259A

6. 输入输出和中断系统

主要内容:

-

基本概念 I/O接口和端口 端口的编址方式

-

简单接口芯片及其应用

-

基本输入输出方法

-

中断的基本概念及工作过程

6.1 基本概念

掌握:I/O接口的基本功能;端口的概念及编址方式;I/O地址译码

-

I/O系统(I/O设备、I/O接口、I/O软件):除开处理器和内存之外的部分

-

该系统的特点:

-

复杂性:设备的复杂性,随机事件

-

异步性:操作上的异步性和时间上的任意性

-

实时性:对不同设备提供及时服务

-

与设备无关性:中间环节,I/O接口

-

-

I/O接口:将I/O设备连接到系统总线上的一组逻辑电路的总称

-

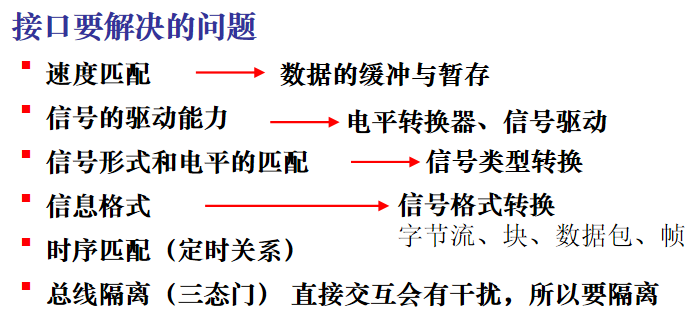

接口的功能:

-

数据缓冲和暂存

-

信号电平与类型的转换

-

增加信号的驱动能力

-

对外设进行检测、控制与管理,中断处理

-

-

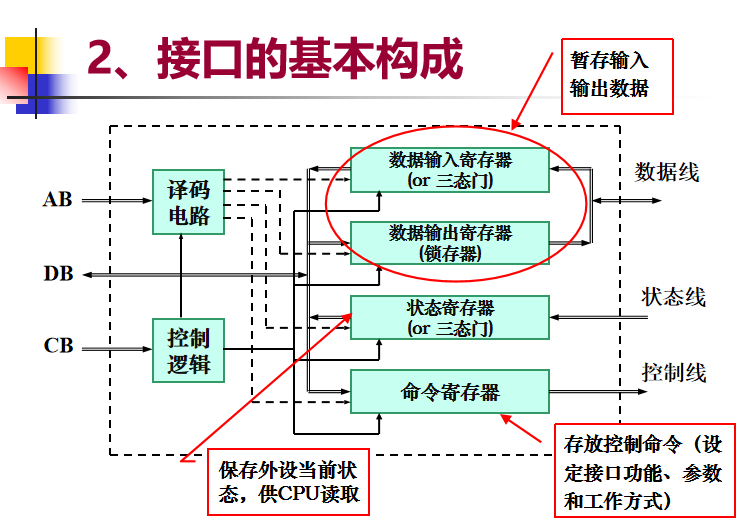

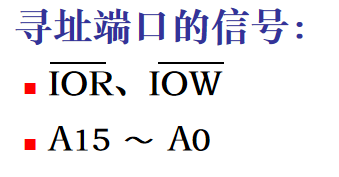

接口的基本构成:

-

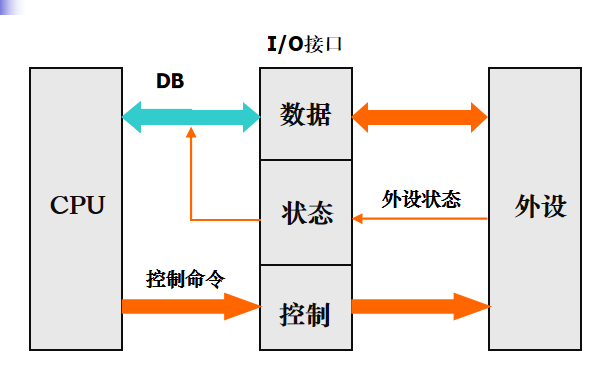

I/O端口:接口电路总用于缓存数据及控制信息的部件

分为:数据端口、状态端口、控制端口

-

I/0端口编址

每个接口中含1个或多个端口。

目的:确保CPU能够访问到每个不同的端口。

寻找端口的方法:

-

首先找到端口所在的接口电路芯片(片选)

-

在该芯片上找具体访问的端口号(片内寻址)

-

注意:

若接口中仅有一个端口,则找到芯片即找到端口 若接口中有多个端口,则找到芯片后需再找端口

-

公式:

每个端口地址=片选地址(高位地址)+片内地址

-

-

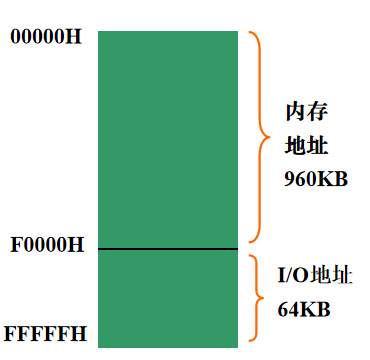

I/O端口的编址方式

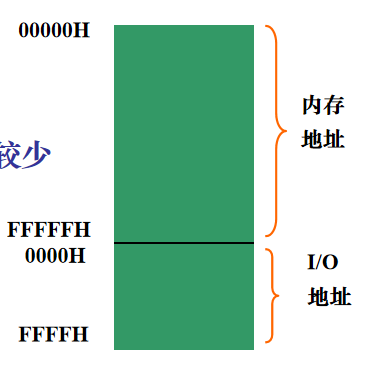

8086/8088寻址端口的能力:内存是1MB,端口有64K个

编址方式分为:

-

与内存统一编址

-

独立编址

-

-

与内存统一编址:

特点:指令及控制信号统一,内存地址资源减少

-

独立编址:

特点:内存地址资源充分利用,应用于端口指令较少

-

端口的寻址

寻址端口信号:

-

8088/8086的I/O端口编址

采用I/O独立编址方式(但地址线与存储器共用) 地址线上的地址信号用IO/#M来区分 I/O操作只使用20根地址线中的16根:A15~A0 可寻址的I/O端口数为64K(65536)个 I/O地址范围为0~FFFFH IBM PC只使用了1024个I/O地址(0~3FFH),端口地址资源就非常丰富了。

-

I/O地址的译码

目的:确定端口地址是目标端口

参加译码的信号:IOR非、IOW非

产生条件(两组信号组和产生):

OUT指令将使总线的IOW非信号有效 IN指令将使总线的IOR非信号有效,数据被读进ACC

译码的地址信号:

当接口只有一个端口时: 无片内地址,全部地址信号均为高位地址(可全部参与译码),译码输出直接选择该端口; 当接口具有多个端口时: 则16位地址线的高位参与译码(决定接口的基地址),而低位则用于确定要访问哪一个端口。

由于端口资源丰富,端口地址译码常采用部分地址译码

6.2 简单接口电路

掌握: 接口电路的分类及特点; 两类简单接口芯片的应用

-

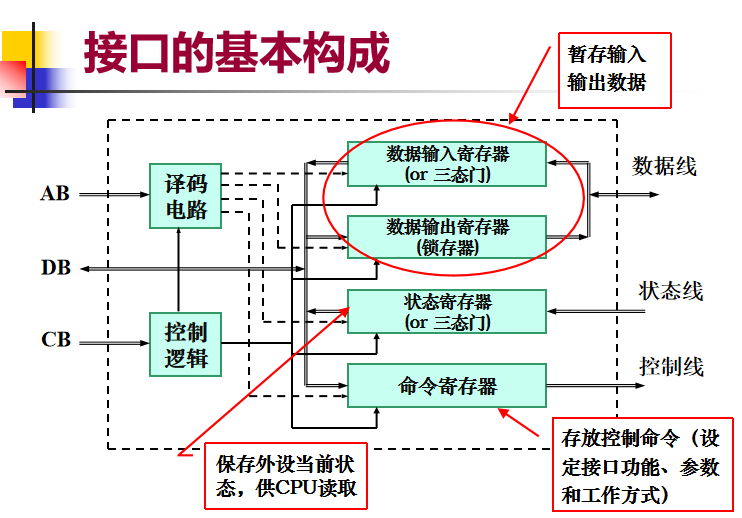

接口的基本组成:

-

数据输入/输出寄存器 (数据暂存)

-

命令寄存器 (暂存控制命令)

-

状态寄存器 (保存外设当前状态,供CPU读取)

-

-

接口的类型和特点:

-

按传输信息方向分类:输入、输出接口

-

按传输类型分类:数字接口、模拟接口

-

按传输信息方式 分类:串行、并行接口

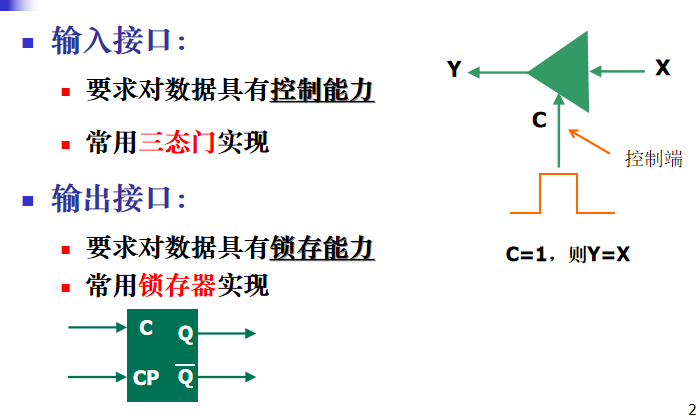

特点:

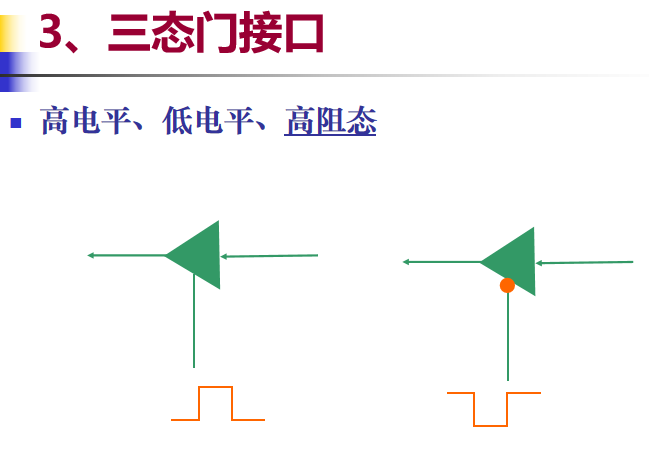

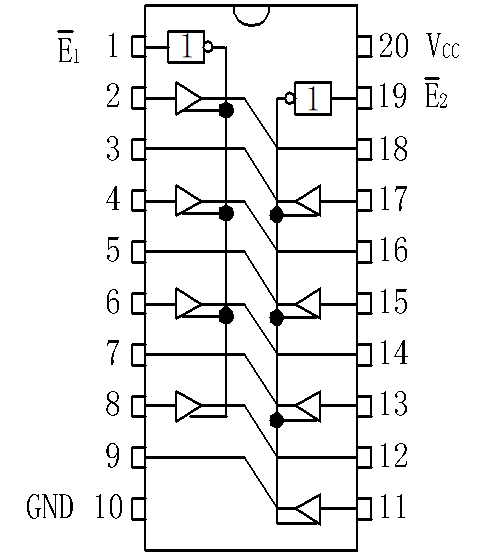

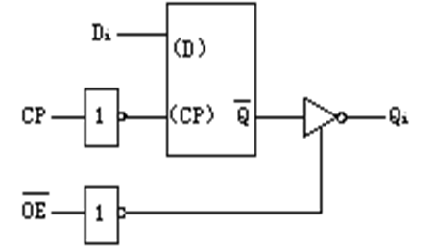

重点芯片:74LS244是典型的三态门接口芯片

特点:具有控制数据的能力,不具备数据的锁存能力

内置8个三态门集成电路芯片;在外设具有数据保持能力时用来输入接口

锁存器接口:

特点:对数据具有锁存能力

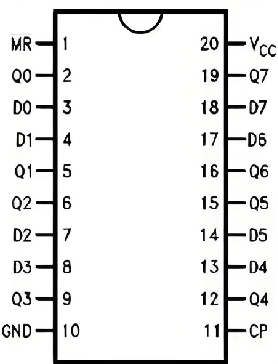

重点芯片:74LS273是典型的锁存器接口芯片

8D触发器,不具备数据控制能力,只能作为输出接口

常用锁存器芯片:

74LS373/374:含有三态的8D触发器,对数据具有控制能力,所以它既可以作为输入接口也可以作为输出接口

-

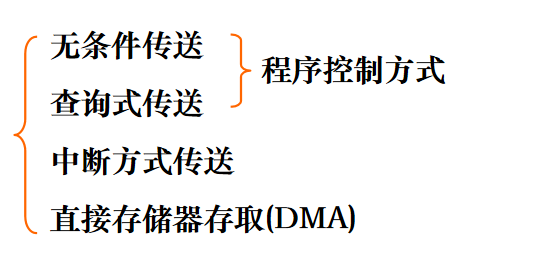

6.3 基本输入/输出方法

-

无条件传送:要求外设总是处于Ready状态;优点呢就是接口和软件简单,缺点就是只能适用于简单的东西,应用范围窄

-

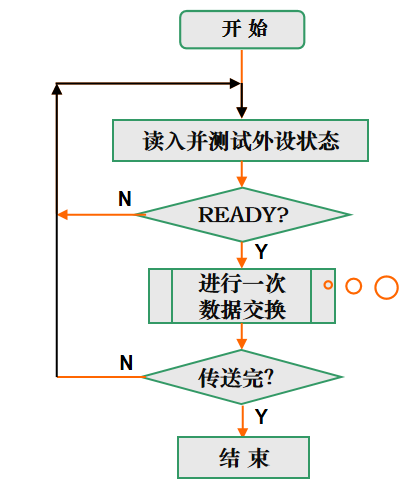

查询式传送:只有条件满足时才能进行数据传送;而且每满足一次条件只能传送一次数据

适用于:外设并不总是准备好,而且对于传送速率和效率要求不高。

条件:外设应提供设备状态信息;接口应具备状态端口

优点:就是软硬件比较简单;缺点就是CPU效率低下,实时性较差,速度慢

-

中断方式传送:特点就是外部设备实时性好,CPU效率高缺点就是:程序编制相对较为复杂,适合于中速的外部设备。

-

以上三种I/O方式的共性就是:信息的传送都需要通过CPU:地址信号、控制信号等

-

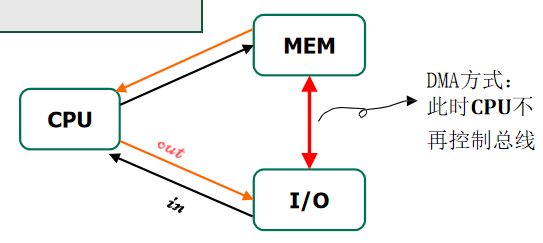

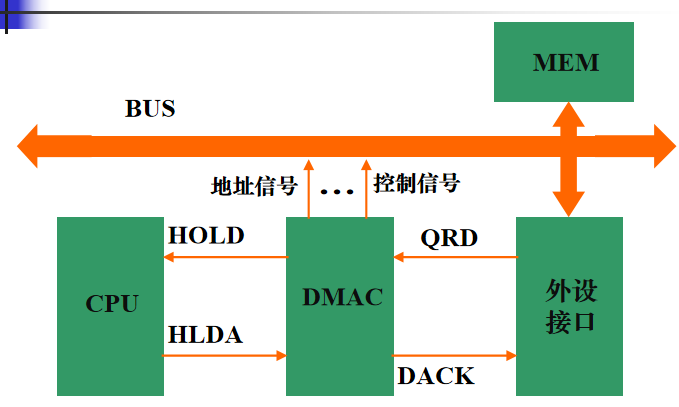

DMA控制方式:

特点:外设和存储器直接进行数据交换,不需要CPU当媒介了;总线由DMA控制器(DMAC)进行控制,内存、外设的地址和读写控制信号均由DMAC提供

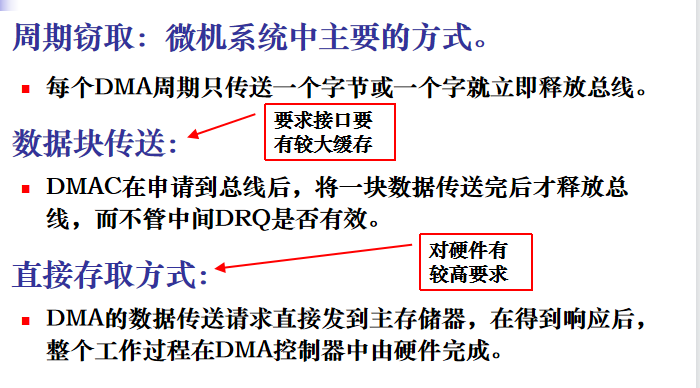

DMA工作方式:

注意: 数据传输由DMA硬件来控制,数据直接在内存和外设之间交换,可以达到很高的传输速率。 控制复杂,硬件成本相对较高。

-

4种基本I/0控制方式总结

无条件传送: 简单,适用范围小,仅适用于“随时准备好”的低速外设 查询工作方式 简单,适用于具备“状态信息”的多个低速外设 CPU效率低,控制实时性差 中断方式 适用于中速外设 相对于查询方式,CPU效率较高,控制实时性较好 DMA方式: 数据传输由DMA硬件来控制,数据直接在内存和外设之间交换,可 以达到很高的传输速率。 控制复杂,硬件成本相对较高。

6.4 中断技术

掌握:

-

中断的基本概念

-

中断响应的一般过程

-

中断向量表及其初始化

-

8088/8086中断系统

6.4.1 中断的基本概念

中断就是,CPU在执行一个任务时,诶突然有老板(中断源)叫他去做另外一个任务(中断服务子程序),然后CPU就跑了,把那个任务完成后又回来继续接着做原来的任务。

引入中断的原因:

提高对外设请求的响应实时性 实现对特殊事件的实时响应 提高数据传输率 提高了CPU的利用率 避免了CPU不断检测外设状态的过程

6.4.2 中断类型

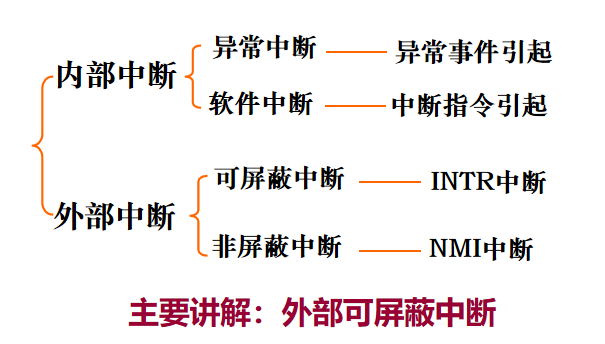

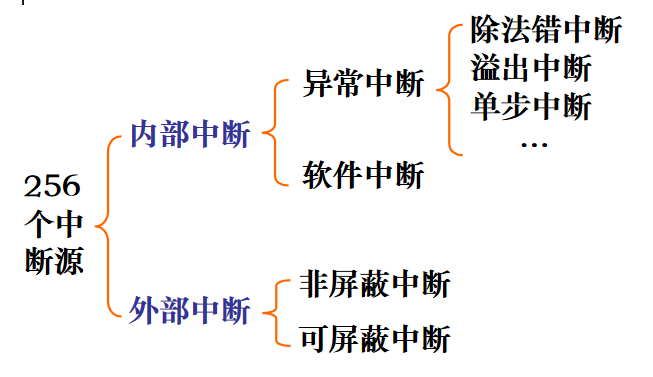

根据中断请求的来源分为:

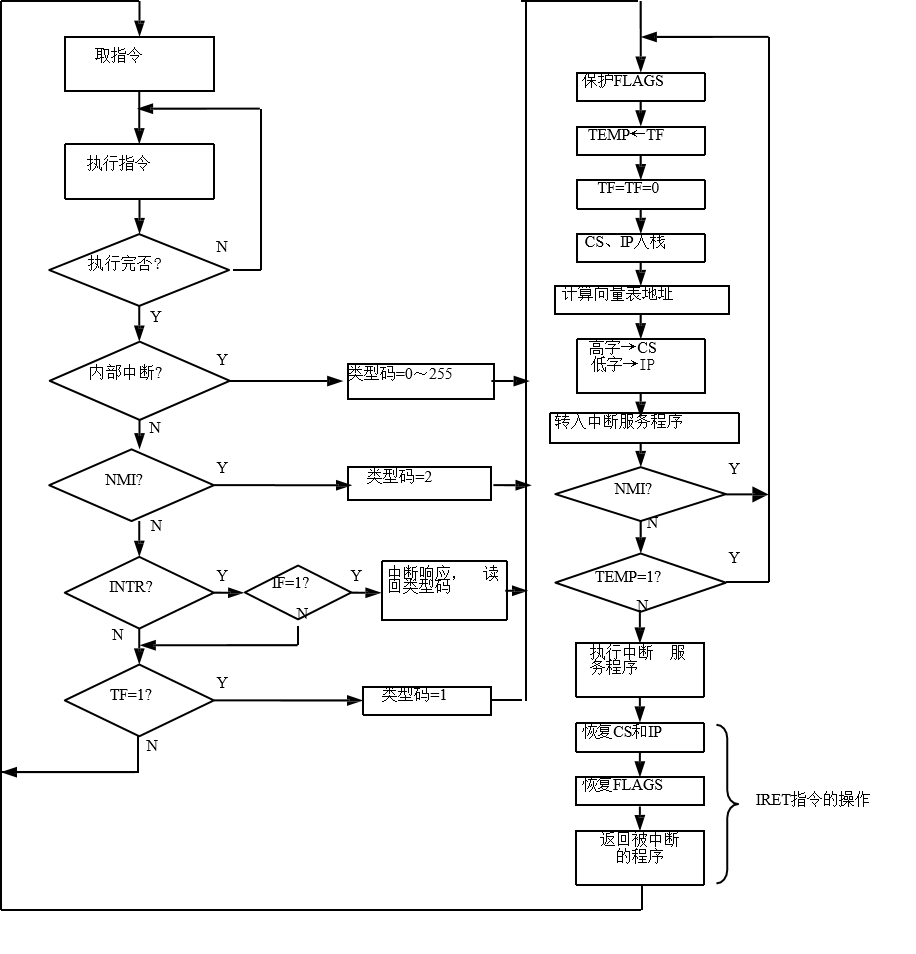

外部可屏蔽中断的响应过程为:

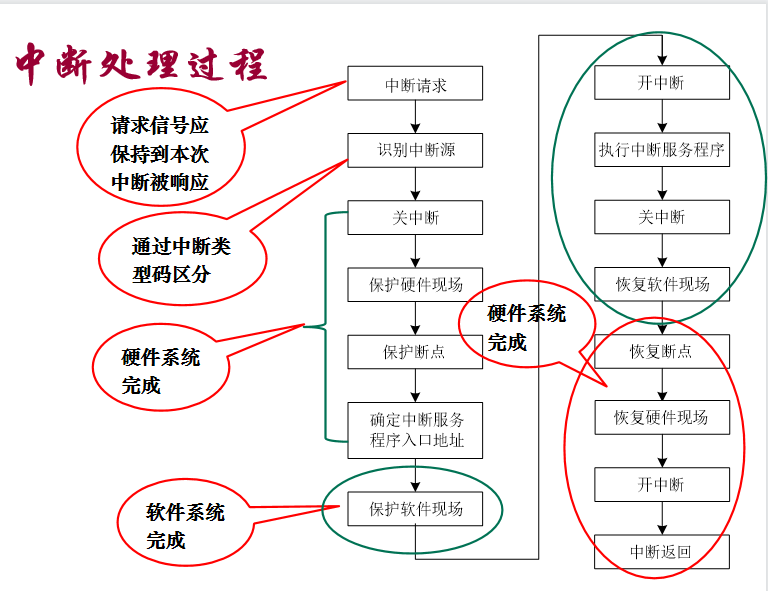

(1)中断请求 (2)中断源识别及中断判优 (3)中断响应 (4)中断处理(服务) (5)中断返回

-

中断请求:NMI、INTR(外可屏蔽中断请求信号);该信号不能过宽也不能过窄,要保持到被处理为止,CPU响应中断口,中断请求信号应及时撤销

-

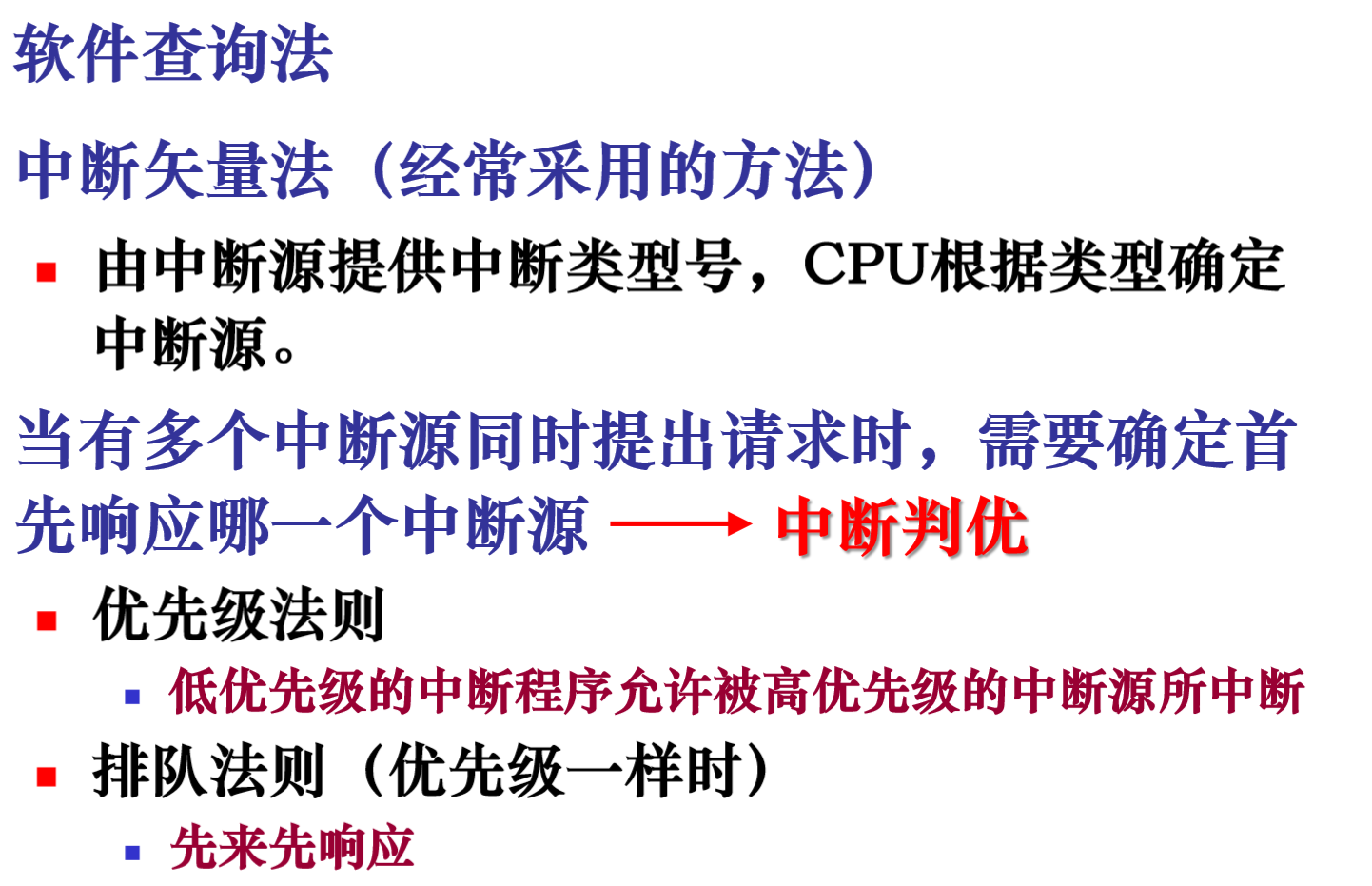

中断源识别:

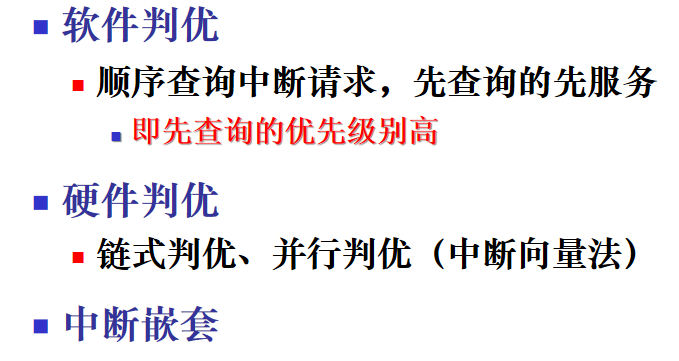

中断判优:

-

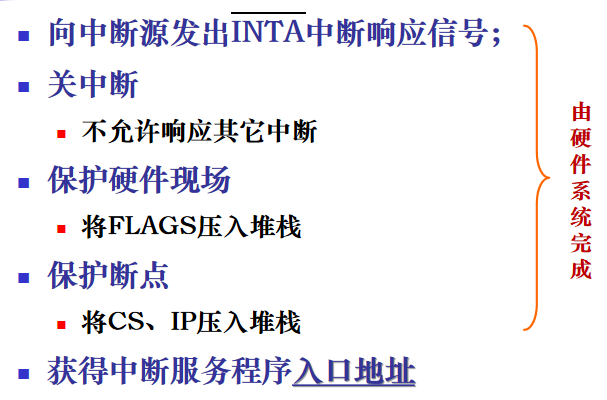

中断响应:

-

中断处理:

执行中断服务子程序 中断服务子程序的特点: 都为“远过程” 用IRET指令返回

-

中断返回

执行IRET指令,使IP、CS和FLAGS从堆栈弹出 和硬件现场

中断处理过程:

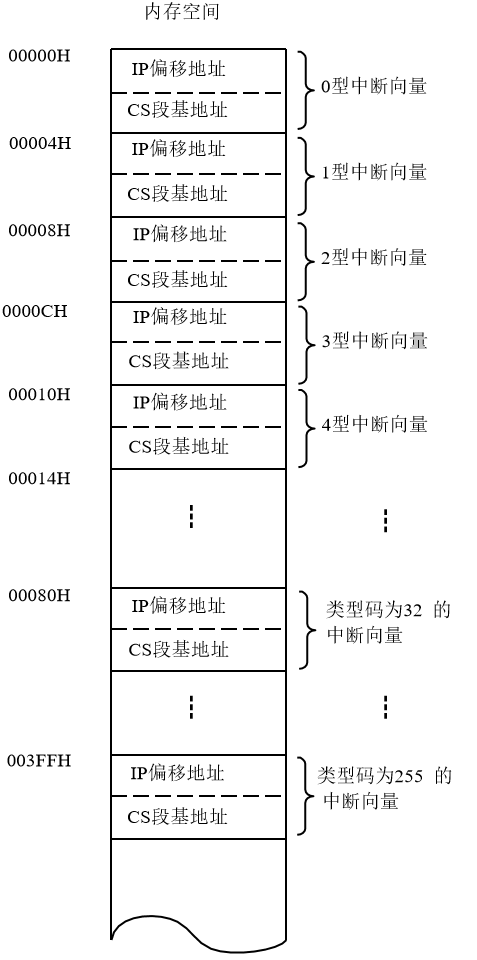

6.4.3 中断向量表

存放各类中断的中断服务程序的入口地址; 每个入口占用4 Bytes,其中: 低地址字单元中存放入口的偏移地址,高地址字单元中存放入口的段基址; 表的地址位于内存的00000H~003FFH,大 小为1KB,共256个入口。

中断向量表的初始化:

将用户自定义的中断服务程序入口地址放入向量表 注意点: 向量表所在的段地址=0 存放子程序入口的单元的偏移地址=n×4 例: 将中断向量码为48H的服务程序入口地址放入向量表

MOV AX,0000H MOV DS,AX MOV SI,0120H MOV BX,OFFSET TIMER MOV [SI],BX MOV BX,SEG TIMER MOV [SI+2],BX

6.4.4 8088/8086中断系统

6.5 8088内部中断与NMI中断

特点:

8088/8086 中断响应和处理流程

注意:

反应中断响应总体优先级: 内部中断 高于 外部非屏蔽中断 高于 外部可屏蔽中断

6.6 中断控制器 8259A

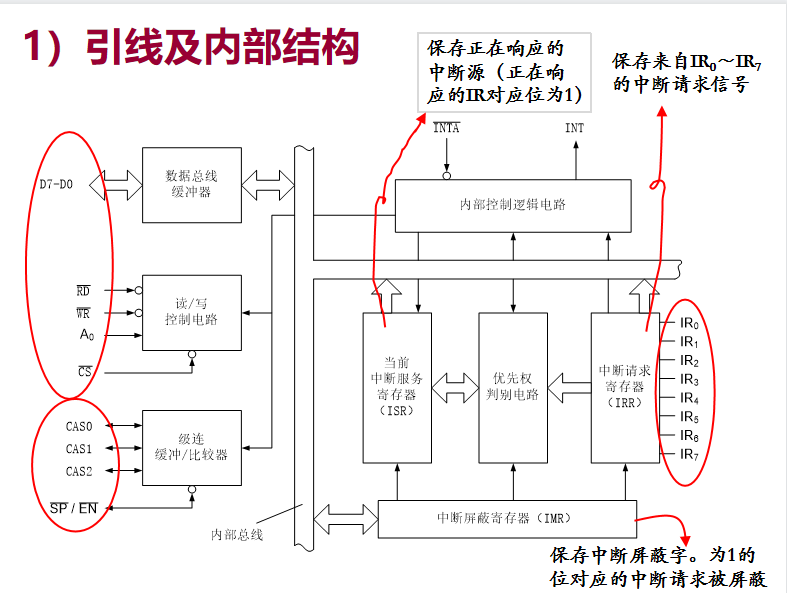

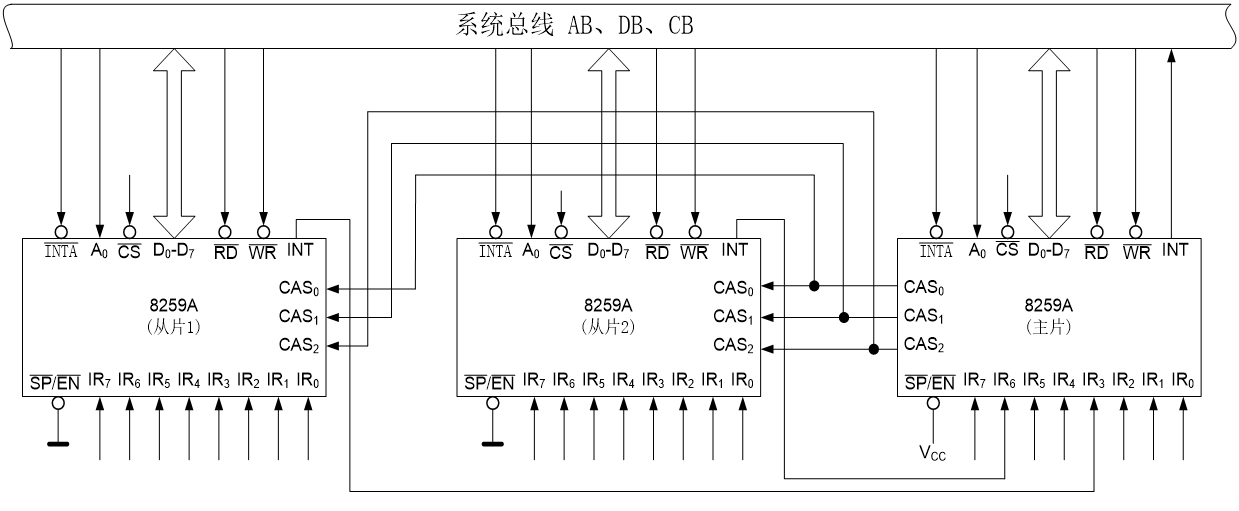

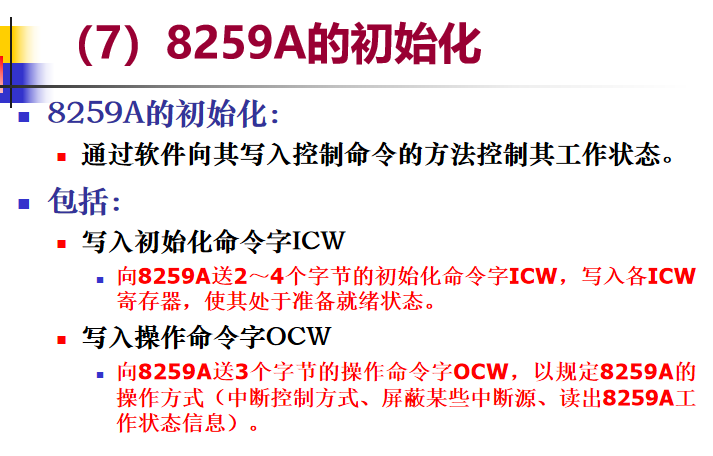

可编程中断控制器,用于可屏蔽中断管理。 单片8259A可管理8个外边中断源,通过级联,最多可以管理64个外部中断源。 了解: 主要引线及内部结构 工作过程 工作方式

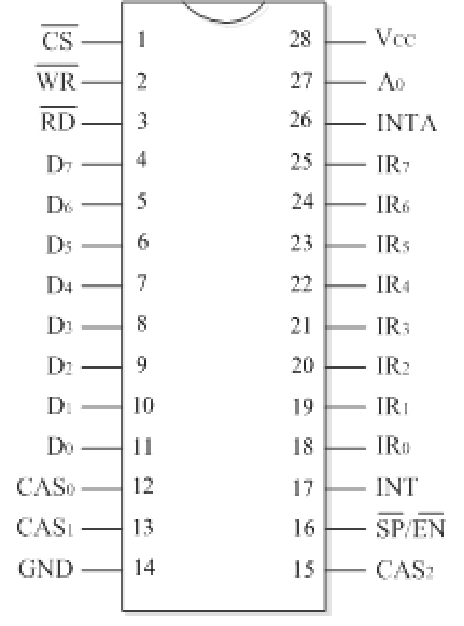

引线及内部结构

D0-D7:数据信号 #WR:写允许 #RD:读允许 #CS:片选信号 A0:内部寄存器的选择信号与#CS、#WR、#RD信号相配合,对不同的内部寄存器进行读写. INT:中断请求; #INTA:中断响应 CAS0~CAS2:级联控制 #SP/#EN:双功能控制 IR0---IR7:中断请求输入

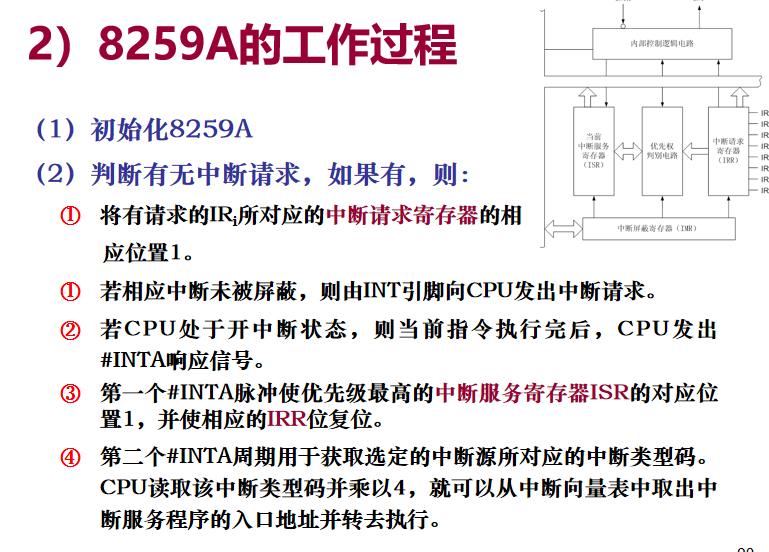

8259A的工作过程

8259A的工作方式

-

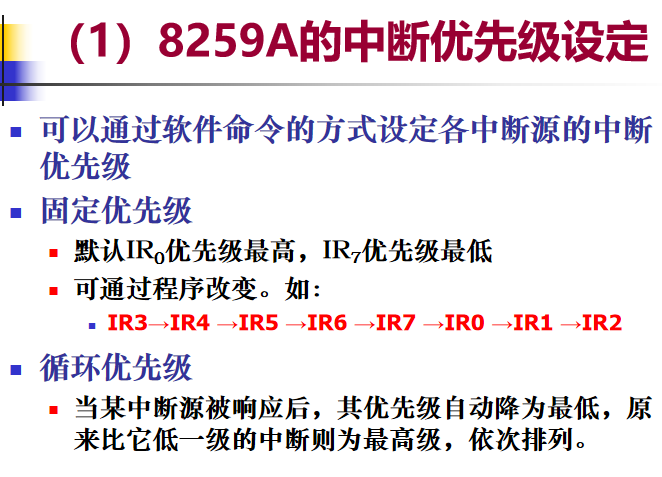

中断优先级----固定优先级,循环优先级

-

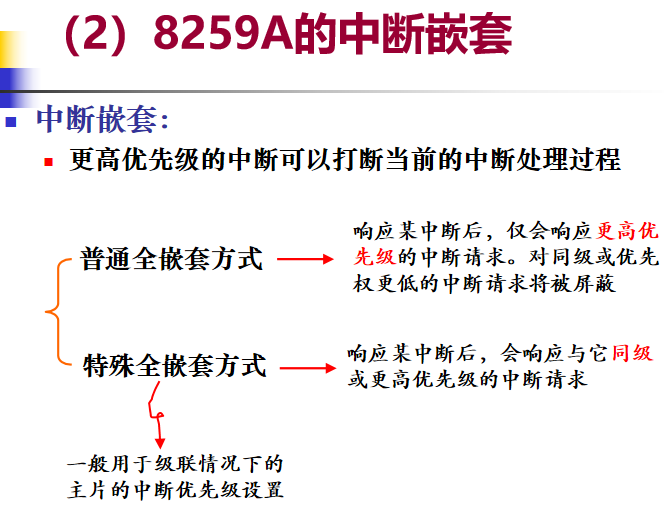

中断嵌套方式

-

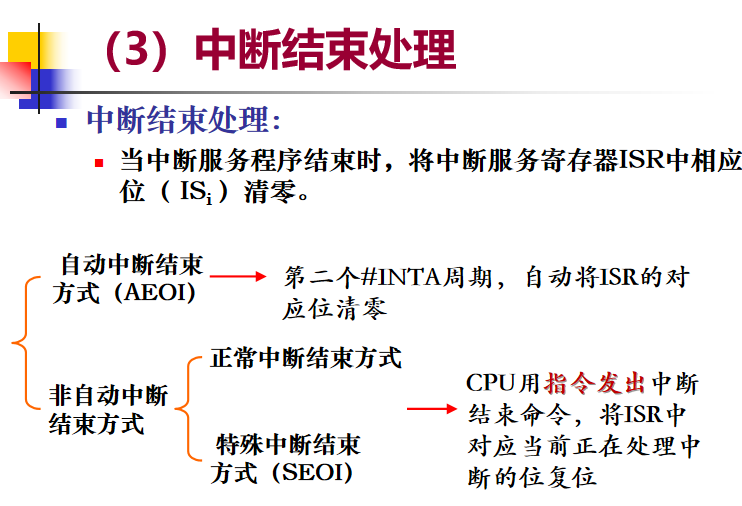

中断结束处理

-

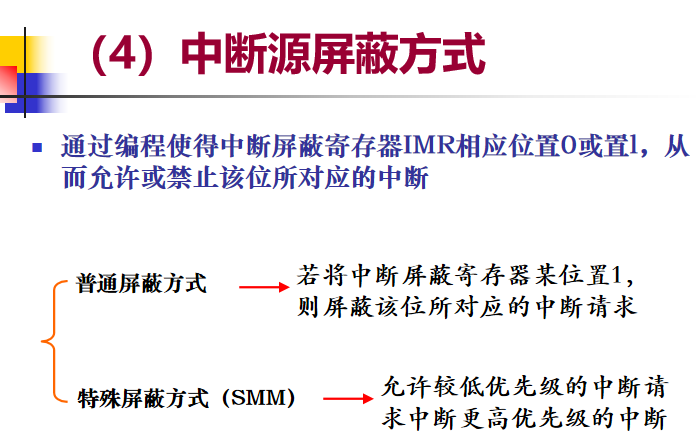

中断源屏蔽方式

-

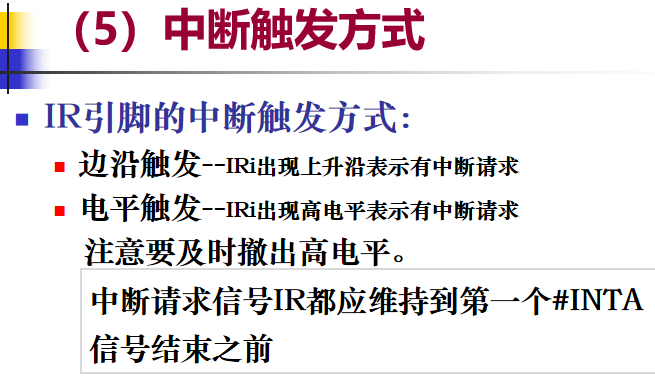

中断触发方式

-

级联工作方式

(6) 8259A的级联

设置一片为主片,将主片的IR端接入到从片的INT端。实现最多64个中断源的中断控制。

中断程序设计的一般过程

-

确定中断类型号 应用程序可使用的中断类型号为60H~66H和68H~6FH

-

保存原中断向量 在将自己的中断程序入口地址置入中断向量表之前,应先保存该地址中原来的内容。

-

将自己的中断向量放入向量表;

-

设置中断屏蔽字(可选)。若编写的是硬件中断程序,应将所使用的硬件中断对应的8259A的中断屏蔽位开放;

-

CPU开中断;

-

恢复原中断向量。