ARM SMMUv3 STE表和CD表数据格式分析(三)

1.简介

SMMUv3的Stream Table由STE(Stream Table Entry)表和CD(Context Descriptor)表组成。STE表如果是一级表,则全部由STE组成,每个STE占用64字节,如果是二级表,则第一级表由L1STD组成,每个L1STD占用8字节,L1STD保存了STE表的基地址,第二级表由STE组成。CD表如果是一级表,则表全部由CD组成,每个CD占用64字节,如果是二级表,则第一级表由L1CD组成,每个L1CD占用8字节,保存了CD表的基地址,第二级表由CD组成。

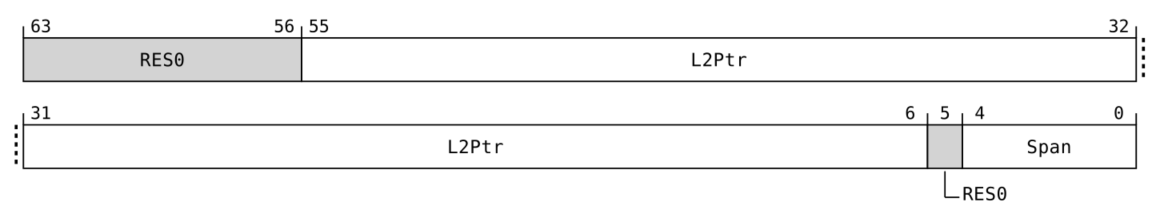

2.L1STD

当Stream table的格式为2.2-level Stream table时,第一级Stream table为L1STD,长度为8字节,保存了第二级Stream table STE的基地址。L1STD格式如下所示,L2Ptr保存STE基地址,Span为L2Ptr指向的STE数组中包含STE的数量(2^(Span-1) ),Span的取值范围为0 - SMMU_STRTAB_BASE_CFG .SPLIT + 1。

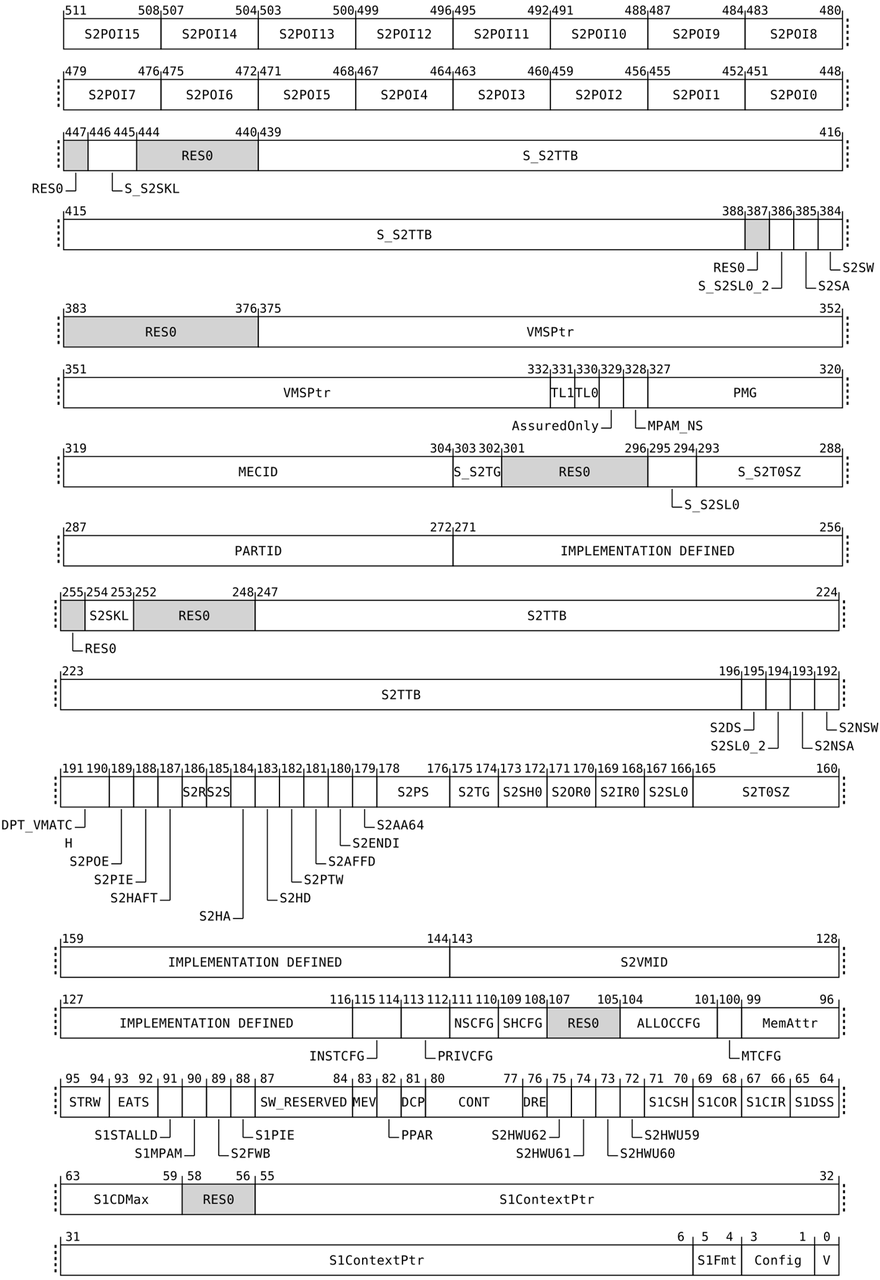

3.STE

STE中保存了地址转换权限信息、第一阶段地址转换信息和第二阶段地址转换信息,具体如下图所示,一个STE占用64字节。

STE中一些重要位域的意义如下表所示:

| 位域 | 名称 | 意义 | |||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| [0] | V | 0b0: STE内容无效,将被忽略。 0b1: STE内容有效。 | |||||||||||||||||||||||||||||||||||

| [3:1] | Config |

| |||||||||||||||||||||||||||||||||||

| [5:4] | S1Fmt | 定义第一阶段地址转换CD表的格式。 0b00: linear table,由SubstreamID[STE.S1CDMax - 1:0]索引。线性CD表按自身大小对齐,S1ContextPt[STE.S1CDMax + 5:6]为0。 0b01: 2-level table。第一级包含1-16384个L1CD的指针,最大128KB,第二级CD表大小为4KB,包含64个CDs。 如果STE.S1CDMax<=6,则只有一个L1CD的指针有效,否则使用SubstreamID[STE.S1CDMax - 1:6]索引第一级表,使用 SubstreamID[5:0]索引第二级表。 第一级表按自身大小或64字节对齐,取最大者。如果STE.S1CDMax>9,则S1ContextPt[STE.S1CDMax - 4:6]为0。 第二级表按4KB对齐,L1CD.L2Ptr[11:0]全为0。 0b10: 2-level table。第一级包含1-1024个L1CD的指针,最大8KB,第二级CD表大小为64KB,包含1024个CDs。 如果STE.S1CDMax<=10,则只有一个L1CD的指针有效,否则使用SubstreamID[STE.S1CDMax - 1:10]索引第一级表,使用 SubstreamID[9:0]索引第二级表。 第一级表按自身大小或64字节对齐,取最大者。如果STE.S1CDMax>13,则S1ContextPt[STE.S1CDMax - 8:6]为0。 第二级表按64KB对齐,L1CD.L2Ptr[15:0]全为0。 0b11: Reserved (behaves as 0b00)。 | |||||||||||||||||||||||||||||||||||

| [55:6] | S1ContextPtr | 保存用于第一阶段地址转换CD表的地址。 | |||||||||||||||||||||||||||||||||||

| [63:59] | S1CDMax | STE.S1CDMax表示CD表的最大索引位数,即STE.S1ContextPtr指向CD的数量最大为2^STE.S1CDMax。 | |||||||||||||||||||||||||||||||||||

| [65:64] | S1DSS | 当substreams使能(STE.S1CDMax != 0)时,S1DSS定义在地址转换过程中,没有找到和SubstreamID相关联的CD表时SMMU的行为 0b00: Terminate。 An abort is reported to the device and the F_STREAM_DISABLED event is recorded. 0b01: Bypass stage 1 as though STE.Config == 0b1x0。 0b10: Substream 0 is not available for use. Transactions that include a substream and select Substream 0 is terminated. An abort is reported to the device and the F_STREAM_DISABLED event is recorded. 0b11: Reserved (behaves as 0b00) | |||||||||||||||||||||||||||||||||||

| [67:66] | S1CIR | STE.S1ContextPtr memory Inner Region attribute. 0b00: Normal, non-cacheable 0b01: Normal, Write-Back cacheable, Read-Allocate 0b10: Normal, Write-Through cacheable, Read-Allocate 0b11: Normal, Write-Back cacheable, no Read-Allocate | |||||||||||||||||||||||||||||||||||

| [69:68] | S1COR | STE.S1ContextPtr memory Outer Region attribute. 0b00: Normal, non-cacheable 0b01: Normal, Write-Back cacheable, Read-Allocate 0b10: Normal, Write-Through cacheable, Read-Allocate 0b11: Normal, Write-Back cacheable, no Read-Allocate | |||||||||||||||||||||||||||||||||||

| [71:70] | S1CSH | STE.S1ContextPtr memory Shareability attribute. 0b00: Non-shareable 0b01: Reserved (behaves as 0b00 ) 0b10: Outer Shareable 0b11: Inner Shareable | |||||||||||||||||||||||||||||||||||

| [80:77] | CONT | 是一个优化缓存连续STE的提示位。 当CONT=0时,说明当前STE和相邻的STE不同,不需要额外缓存,否则认为当前STE和相邻的STE相同,系统会定义一个连续的STE块,其大小为 2^CONT个STE(CONT < SPAN),并且该块的起始StreamID必须满足 StreamID[CONT-1:0] = 0(即StreamID 的低CONT-1位全为 0),SMMU会缓存STE块,以加速访问。 | |||||||||||||||||||||||||||||||||||

| [82] | PPAR | 0b0: Auto-generated responses on PRI queue overflow do not include a PASID TLP prefix. 0b1: Auto-generated responses on PRI queue overflow include a PASID TLP prefix if permitted. | |||||||||||||||||||||||||||||||||||

| [83] | MEV | Merge Events arising from terminated transactions from this stream. 0b0: Do not merge similar fault records. 0b1: Permit similar fault records to be merged. | |||||||||||||||||||||||||||||||||||

| [88] | S1PIE | 第1阶段地址转换间接权限是否开启。SMMU_IDR3.S1PI == 0时有效,否则忽略。 0b0: 第1阶段地址转换权限来自于页表 0b1: 第1阶段地址转换权限来自于CD.PIIP和CD.PIIU,此时页表中的权限位变成PIIndex,用来索引权限 | |||||||||||||||||||||||||||||||||||

| [91] | S1STALLD | Stage 1 Stall Disable. 0b0: Allow stalling fault model for stage 1 (configured in CD). 0b1: Disallow stalls to be configured for Stage 1 (faults terminate immediately). | |||||||||||||||||||||||||||||||||||

| [99:96] | MemAttr | MTCFG=1时,MemAttr编码的内存属性将会覆盖来自DMA访问的内存属性。编码和VMSAv8-64 stage 2 MemAttr[3:0]一致(除了0b0100、0b1000、0b1100,如果是这些内存属性,行为和Device-nGnRnE一样)。 | |||||||||||||||||||||||||||||||||||

| [100] | MTCFG | 0b0: Use incoming type or Cacheability. 0b1: Replace incoming type or Cacheability with that defined by MemAttr field. | |||||||||||||||||||||||||||||||||||

| [143:128] | S2VMID | Virtual Machine Identifier. Marks TLB entries inserted because of translations located through this STE, differentiating them from translations belonging to different virtual machines. | |||||||||||||||||||||||||||||||||||

| [247:196] | S2TTB | 第二阶段地址转换页表基地址。 | |||||||||||||||||||||||||||||||||||

| [439:388] | S_S2TTB | 安全世界第二阶段地址转换页表基地址。 |

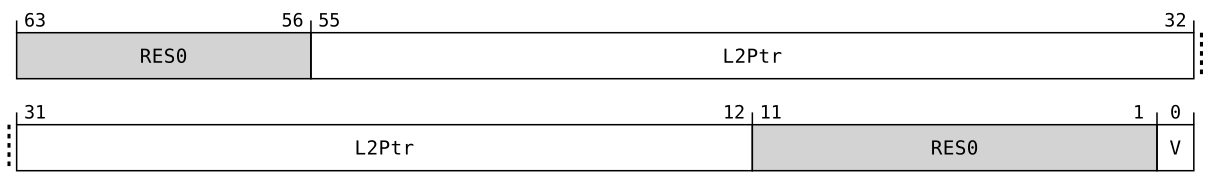

4.L1CD

若CD表采用2级表,则第一级CD表为L1CD,长度为8字节,格式如下图所示,L2Ptr指向第二级CD表的基地址。V=0表示L2Ptr无效,V=1表示L2Ptr有效。

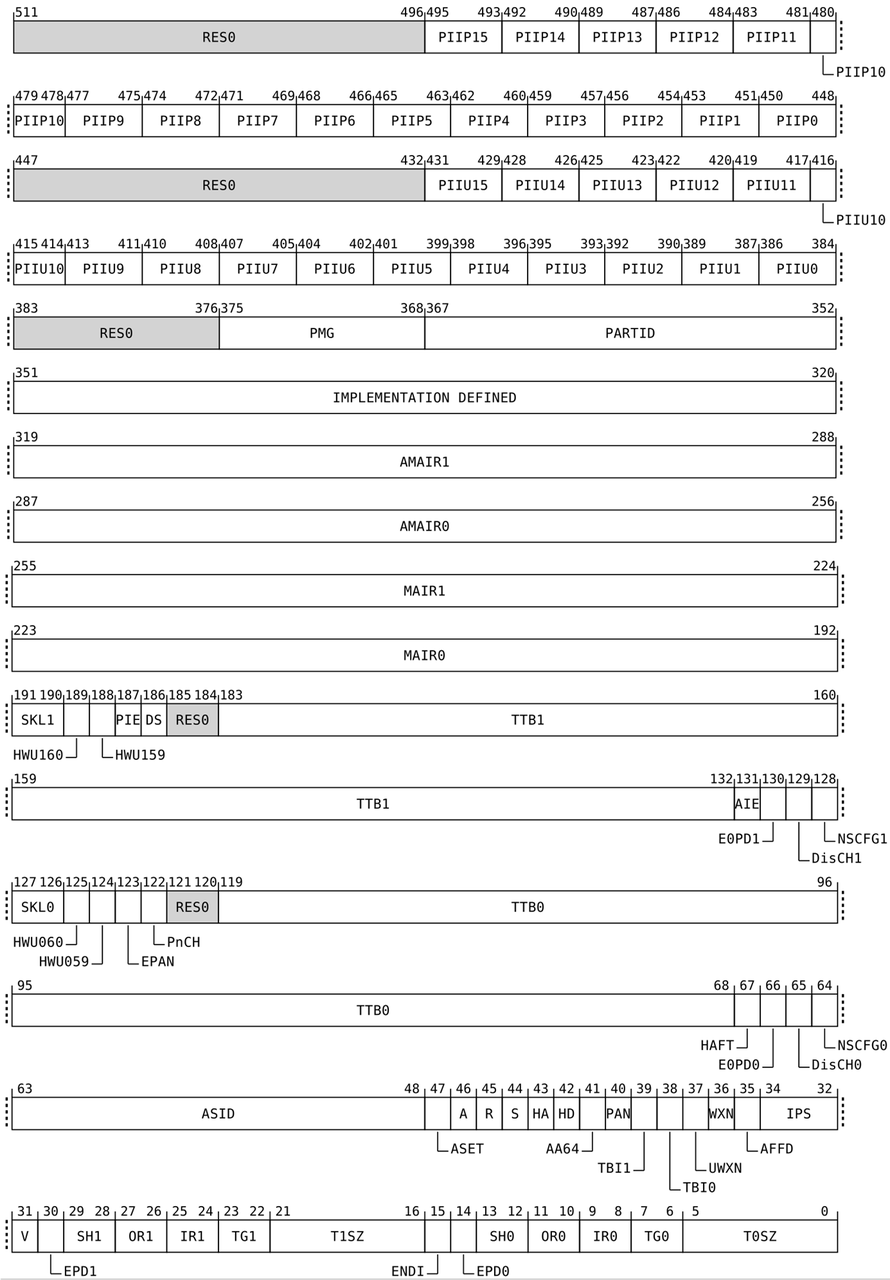

5.CD

CD中保存了第一阶段地址转换的信息,具体如下图所示,一个CD占用64字节。

CD中一些重要位域的意义如下表所示:

| 位域 | 名称 | 意义 |

|---|---|---|

| [5:0] | T0SZ | TTB0页表转换VA的地址范围,和TCR_ELx.T0SZ的定义一样,VA地址范围为2^(64-T0SZ)。 如果CD.AA64选择的是VMSAv8-64: • If SMMU_IDR3.STT == 0, the maximum valid value is 39. • If SMMU_IDR3.STT == 1, the maximum valid value is: – 48, if the corresponding CD.TGx selects a 4KB or 16KB granule. – 47, if the corresponding CD.TGx selects a 64KB granule. • 如果SMMU_IDR5.VAX设置支持52-bit VAs,并且满足下面的条件之一,则T0SZ允许的最小值为12,如果都不满足,则T0SZ允许的最小值为16。 – The corresponding CD.TGx selects a 64KB granule size. – CD.DS == 1 and the corresponding CD.TGx selects a 4KB or 16KB granule size. 如果CD.AA64选择的是VMSAv9-128(任何StreamWorld的EL2不支持VMSAv9-128): • The maximum valid value is: – 48, if CD.TGx selects a 4KB or 16KB granule. – 47, if CD.TGx selects a 64KB granule. • The minimum valid value is: – 8, if SMMU_IDR5.VAX indicates support for 56-bit VAs and StreamWorld is EL3. – 9, if SMMU_IDR5.VAX indicates support for 56-bit VAs and StreamWorld is EL1 or any-EL2-E2H. – 12, if SMMU_IDR5.VAX indicates support for 52-bit VAs. – 16, if SMMU_IDR5.VAX indicates support for 48-bit VAs. |

| [7:6] | TG0 | TTB0指向的页表大小(CD.AA64选择的是VMSAv8-64 or VMSAv9-128),且TG0选择的值必须在 SMMU_IDR5寄存器的支持列表中。 0b00: 4KB 0b01:64KB 0b10: 16KB 0b11:Reserved |

| [9:8] | IR0 | Inner region Cacheability for TTB0(指向的页表) access. 0b00: Non-cacheable 0b01: Write-back Cacheable, Read-Allocate, Write-Allocate 0b10: Write-through Cacheable, Read-Allocate 0b11: Write-back Cacheable, Read-Allocate, no Write-Allocate 在某些SMMU实现中,0b01和0b11可能有不同行为,但规范未强制要求,需参考具体设计文档 |

| [11:10] | OR0 | Outer region Cacheability for TTB0(指向的页表) access. 0b00: Non-cacheable 0b01: Write-back Cacheable, Read-Allocate, Write-Allocate 0b10: Write-through Cacheable, Read-Allocate 0b11: Write-back Cacheable, Read-Allocate, no Write-Allocate 在某些SMMU实现中,0b01和0b11可能有不同行为,但规范未强制要求,需参考具体设计文档 |

| [13:12] | SH0 | Shareability for TTB0 access. 0b00: Non-shareable 0b01: Reserved (behaves as 0b00 ) 0b10: Outer Shareable 0b11: Inner Shareable 如果CD.IR0和CD.OR0都配置为0b00,即normal Non-cacheable,此时忽略SH0配置,TTB0页表的共享属性为OSH(Outer Shareable) |

| [14] | EPD0 | TTB0 translation table walk disable. 0b0: Perform translation table walks using TTB0. 0b1: 当TLB miss时,使用TTB0进行页表遍历时会产生Translation fault,地址转换也随之停止,CD.T0SZ/CD.TG0/CD.IR0/CD.OR0/CD.SH0/CD.TTB0 are IGNORED . |

| [15] | ENDI | Translation table endianness. 0b0: Little Endian 0b1: Big Endian |

| [21:16] | T1SZ | TTB1页表转换VA的地址范围。和TCR_ELx.T1SZ的定义一样。 |

| [23:22] | TG1 | TTB1页表大小。 0b00: Reserved 0b01: 16KB 0b10: 4KB 0b11: 64KB |

| [25:24] | IR1 | TTB1页表Inner region Cacheability。编码和CD.IR0一致。 |

| [27:26] | OR1 | TTB1页表Outer region Cacheability。编码和CD.OR0一致。 |

| [29:28] | SH1 | TTB1页表的Shareability。编码和CD.SH0一致。 |

| [30] | EPD1 | TTB1 translation table walk disable。编码和CD.EPD0一致。 |

| [31] | V | CD是否有效。 |

| [34:32] | IPS | IPA地址宽度。 0b000: 32 bits 0b001: 36 bits 0b010: 40 bits 0b011: 42 bits 0b100: 44 bits 0b101: 48 bits 0b110: In SMMUv3.0 implementations, this value is Reserved and behaves as 0b101. In implementations of SMMUv3.1 and later, this value selects 52 bits of IPA 0b111: In SMMUv3.0 implementations, this value is Reserved and behaves as 0b101. In implementations of SMMUv3.1 to SMMUv3.3, this value is Reserved and behaves as 0b110. In implementations of SMMUv3.4 and later, this value selects 56 bits of IPA. |

| [35] | AFFD | 当硬件(HA == 0或者不支持HTTU)不支持自动更新Access Flag,AFFD控制是否产生Access Flag Fault。页表初次创建时AF=0,若CPU第一次访问AF时会触发异常,然后软件将AF设置为1,若页表长时间不使用,可以将AF设置为0。TLB不会缓存AF=0的页表。AF标志的主要作用是优化TLB缓存页表。若支持硬件自动更新AF,则不会产生中断,无需软件参与。 0b0: An Access flag fault occurs (behavior controlled by ARS bits) 0b1: An Access flag fault never occurs. The TTD.AF bit is considered to be always 1. |

| [36] | WXN | TTB0和TTB1的页表属性为可写,如果使用读指令访问时是否产生权限异常。 0b0: Instruction read is allowed as normal 0b1: Instruction read to writable page raises a Permission fault |

| [37] | UWXN | TTB0和TTB1的页表属性为可写,特权等级为用户,如果使用读指令访问时是否产生权限异常。 0b0: Instruction read is allowed as normal 0b1: Instruction read from user-writable page raises a stage 1 Permission Fault |

| [38] | TBI0 | 是否忽略TTB0的VA[63:56]高字节地址。 |

| [39] | TBI1 | 是否忽略TTB1的VA[63:56]高字节地址。 |

| [41] | AA64 | TTB0和TTB1的页表格式。 0b0: 使用VMSAv8-32 LPAE descriptor formats,当SMMU_IDR0.TTF[0] == 1有效 0b0: 使用VMSAv9-128 descriptor formats,当SMMU_IDR5.D128 == 1有效 0b1: 使用VMSAv8-64 descriptor formats |

| [42] | HD | 硬件是否自动更新CD.TTB0和CD.TTB1页表的Dirty flags。 |

| [43] | HA | 硬件是否自动更新CD.TTB0和CD.TTB1页表的Access flags。 |

| [44] | S | Stage 1 fault behavior. See section 5.5 Fault configuration (A, R, S bits) for a description of fault configuration. |

| [45] | R | Stage 1 fault behavior. See section 5.5 Fault configuration (A, R, S bits) for a description of fault configuration. |

| [46] | A | Stage 1 fault behavior. See section 5.5 Fault configuration (A, R, S bits) for a description of fault configuration. |

| [47] | ASET | 设置ASID的类型。 0b0: 共享的ASID。ASID以及由CD.TTB0和CD.TTB1描述的地址空间,与PE上的某个进程共享。所有匹配的广播无效消息(broadcast invalidation messages)将使该上下文生成的TLB条目失效(在硬件支持且全局启用的情况下),从而保持SMMU和PE的地址空间同步。支持SVA的情况。 0b1: 不共享的ASID。SMMU地址空间和CPU地址空间不同,各自维护自己的TLB。不支持SVA的情况。 |

| [63:48] | ASID | Address Space Identifier. |

| [67] | HAFT | Enable hardware update of Access flag in Table descriptors. SMMU_IDR0.HTTU=0b11才有效。 |

| [119:68] | TTB0 | 虚拟地址高位为0时使用的页表。 In SMMUv3.1 and later, if CD.AA64 selects VMSAv9-128, then bits[119:68] represent the address of the TT0 base, bits[55:4]. Otherwise: • In SMMUv3.1 and later: – Bits[115:68] represent the address of the TT0 base, bits[51:4]. – Bits[119:116] are RES 0. • In SMMUv3.0: – Bits[111:68] represent the address of the TT0 base, bits[47:4]. – Bits[119:112] are RES 0 |

| [183:132] | TTB1 | 虚拟地址高位为1时使用的页表。 In SMMUv3.1 and later, if CD.AA64 selects VMSAv9-128, then bits[183:132] represent the address of the TT1 base, bits[55:4]. Otherwise: • In SMMUv3.1 and later: – Bits[179:132] represent the address of the TT1 base, bits[51:4]. – Bits[183:180] are RES 0. • In SMMUv3.0: – Bits[175:132] represent the address of the TT1 base, bits[47:4]. – Bits[183:176] are RES 0. |

| [223:192] | MAIR0 | 内存属性寄存器,和MAIR1组成一个64位寄存器。8bit表示一个内存属性,总共可表示8种不同的内存属性,可由页表中的AttrIndx[2:0]进行索引。CPU也有同名寄存器。 |

| [255:224] | MAIR1 | 内存属性寄存器,和MAIR0组成一个64位寄存器。8bit表示一个内存属性,总共可表示8种不同的内存属性,可由页表中的AttrIndx[2:0]进行索引。CPU也有同名寄存器。 |

| [287:256] | AMAIR0 | Auxiliary Memory Attribute Indirection Register 0, bits[31:0]。CPU也有同名寄存器。 |

| [319:288] | AMAIR1 | Auxiliary Memory Attribute Indirection Register 1, bits[31:0]。CPU也有同名寄存器。 |

当SMMUv3支持Hardware Translation Table Update (HTTU),此时硬件会自动更新AArch64页表中的Access flag(AF)和Dirty state,以提高性能,实际芯片中是否支持,由实现决定。软件通过SMMU_IDR0.HTTU获取HTTU的支持信息,具体如下表所示。

| HTTU值 | 意义 | 应用场景 |

|---|---|---|

| 0b00 | 无标志更新支持。SMMU不会自动更新页表项的Accessed Flag或Dirty state。 | 需要软件(如 OS/Hypervisor)手动管理脏页和访问跟踪,性能较低。 |

| 0b01 | 仅支持访问标志Accessed Flag更新。SMMU在访问页表项时自动设置Accessed Flag,但不处理Dirty state。 | 适用于只需跟踪内存访问(如页面换出优化),但脏页仍需软件处理。 |

| 0b10 | 支持Accessed Flag和Dirty state更新。SMMU自动设置Accessed Flag和Dirty state。 | 最常用模式,简化虚拟化内存管理(如VM迁移、脏页跟踪)。 |

| 0b11 | 扩展支持(Accessed Flag+ Dirty state+ 表描述符的Accessed Flag)。在0b10基础上,额外支持对页表描述符本身的AF更新。 | 高级场景,如嵌套分页(Nested Paging)中跟踪各级页表的访问情况。 |

参考资料

- Arm ® System Memory Management Unit Architecture Specification version 3.