pcie 日常问答0604

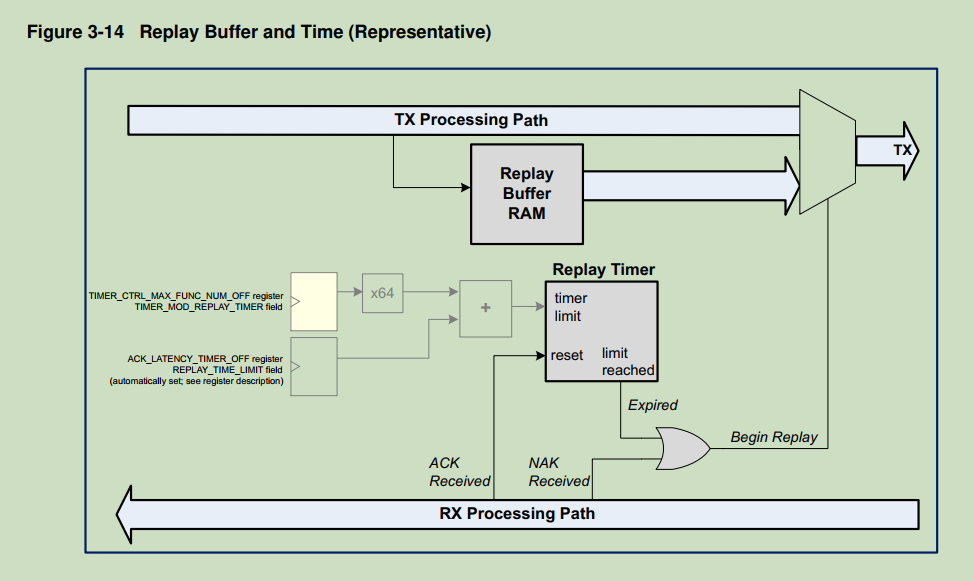

3. retry buffer有多大?

retry number 2bit;最多只能发送4次retry tlp;

Replay Buffer Sizing:

replay buffer 逻辑;大写均为定值;

4. Fcrc,Ecrc,Lcrc ,DCRC占用多少字节?分别是做什么用的?

5. 当发生断链时,tx和rx应该怎么做? tlp dllp分别做了哪些工作?

6. 为什么要做scramble?

128b/130b中为了直流平衡;8b/10b中scramble;扰码器作用消减EMI噪声,扰码器通过降数据流与一个随机序列进行异或操作,使发出去的数据流呈现伪随机特性,降低EMI噪声。减少并行路线中的串扰。扰码器和解扰器在发送和接收端分别工作。

改善直流平衡。

7. 收到uncorrectable,correctable error之后会在哪里表现出来?并且收到对应的error之后应该怎么做?

pcie RX:

- 丢弃tlp

- 产生一个带CA或者UR的completion (np request)

- pci-compatible status register中标记

- AER en之后在AER status中标注

- 产生err MSG(usp only)

- 对于格式错误的TLP,credit将根据该TLP所占用的缓冲区空间予以返还。(不消耗credit)

8. pcie 的cpl为什么会被分割?

注:一次request 返回的多个cpld包其tag ID均相同。

主要有4个原因:

1. request length 超过了max payload size ;

2. cpld中RCB(read completion boundry)限制。

3. 4KB边界限制

4. flow control限制

RCB解释

RCB:read completion boundary,表示completion 边界对齐;

S IP中默认64B;对于 Root Complex,RCB 是 64B 或 128B,取决于寄存器设置Link Control register;非RC的RCB均为128B(0x80对齐)

每个cpl必须从某个RCB对齐地址开始,也只能在RCB边界拆分。

2.3.1.1 Date return for read request

对于一个 Memory Read 请求,各个单独的 Completion 报文可以返回少于请求总数据量的部分数据,只要它们组合在一起时,最终刚好返回了请求的数据总量即可。

- 不同请求的cpl不能被组合;

- IO config read 的cpl,只能回复一个cpl

- cpl的状态寄存器仅代表当前的cpl;当cpld中状态非sc是(successful),length 字段应该被忽略

- cpld包含的字段小于等于MTU

- 一个request 可能被回复多个cpld,

- 多个cpld回复时,必须对齐RCB,且只能以RCB 大小切分。

- 一次request length 跨越了整数个RCB地址,允许拆分多个cpld;

- 规则:起始地址从request地址开始,并对齐RCB边界地址;

- 中间的地址必须以rcb为边界;

- 最后的地址也无需对齐rcb边界,需要满足request即可

- 相同tag下的cpld 必须保序(物理地址必须顺序递增)

- 如果一个 Memory Read Request 是通过 多个 Completion 包返回的,

那么每个后续 Completion 的Byte Count字段当前cpld不一定会传输这么多的内容,= 前一个 Completion 的 Byte Count (−减去) 前一个 Completion 实际返回的数据长度。 - 首个 Completion 的首个数据 DW(4 字节)中,只有在 Request 的 First Byte Enable (First BE) 中被置位的那些字节是有效的。

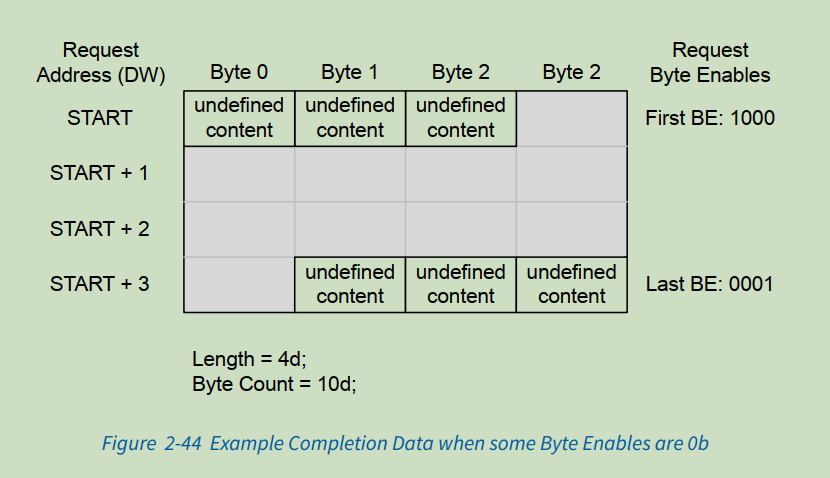

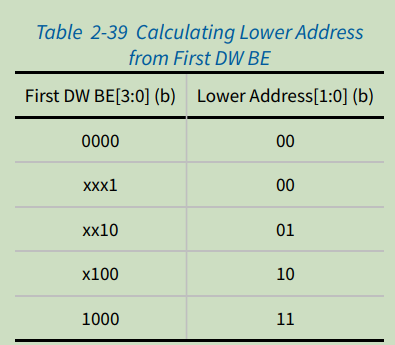

FBE,LBE 规则。

这里简单解释一下;request中的length DW为单位;例如9个length;就是最大可以传36个B字节。

类似于窄带传输(axi),LBE和FBE用来划分第一个DW和最后一个DW中的有效Byte数,如 FBE=c; 那么真实的就是34个B数据;但是数据都是按照DW对齐的,所以就用lower address 来表示数据的起始地址。reqeust中地址如果为0x10000那么FBE=c的lower地址10;那么真是传输地址就是从0x10002开始传输。

切分包的优点:

1. 避免链路阻塞;2.增加传输效率

2.3.2 Completion Handling Rules

Unexpected Completion:收到的ID完全对不上。

9.pcie orderd 规则深层次下的逻辑是什么?该处在rtl是怎么实现?

10.啥叫个生产消费模型,生产了什么?被谁消费了?

11. IDL 和EIOS 有什么区别?

编辑 idl token需要进入scramble 进行扰码;idl 表示物理链路上实际发送的就是00h的码流。

12.8b/10b 128b/130b 编码中PAD K码是干什么用的?

8b/10b编码中,PAD(K23.7)是一种填充符(padding character)。不传递有效数据,长用于填充作用。在polling阶段所有lane均会发送该字段。举例:在gen1,gen2速率下;在if an END or EDB Symbol is placed in a Lane K,但是紧接着K+1没有stp/sdp;之后必须填充pad symbol。

PAD码作用:Used in Framing and Link Width and Lane ordering negotiations。

Ltssm 在Detect 阶段发送link num和lane num用PAD码进行填充(rx detect阶段)。

发射器在退出 Electrical Idle 状态、并开始发送 TS1 序列之前,必须等待其发送端的共模电压稳定下来。(也就是rx detect结束之后)

发射器在进入该状态后,必须在 192 ns 内以 Transmit Margin 字段默认的电压等级开始发出训练码型。此传输电压电平将一直保持,直到进入 Polling.Compliance 或 Recovery.RcvrLock 状态为止。

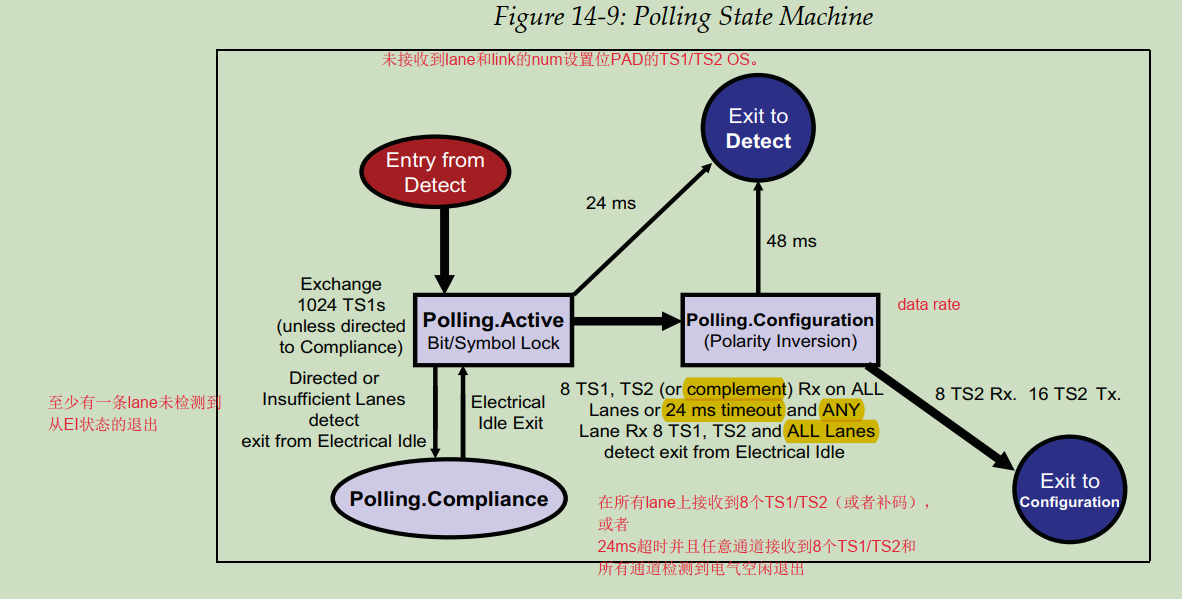

下一个状态时polling.configuration:(满足以下条件)

1. 发送了至少1024个TS1 序列;

2. 收到连续8个 tranning sequence 满足以下任意条件:

a,TS1 lane ,link num都用pad 码填充,且compliance bit为0;

b,TS1,loopback bit 1,ink num都用pad 码填充

c, TS2 (ts1发送之后才开始发送ts2)lane,link num 都为pad 填充

polling.configuration:

1. 开始发送TS2,序列,lane ,link num均PAD填充。

2. 当收到一个TS2 order set之后发送16个TS2 order set。

下一个状态configuration:

1. 在任意有效lane上收到8个连续的TS2 序列,lane,link num均为PAD填充。

下一个状态: polling.compliance:

1. link control2 register 中enter compliance bit在进入polling.active 之前为1;即可进入compliance;

2. 24ms超时:a)所有的lane 在进入polling.active之后没有全部退出EIOS状态。b)detected lane收到连续8个TS1,link & lane num PAD,compliance receive bit为1(symbol5),且loopback bit为0.

那么设备应推断:对端设备进入了 Compliance 模式(可能速率为更高的 Gen),自己应做出对应处理,如进入 Compliance 状态或保持兼容行为。

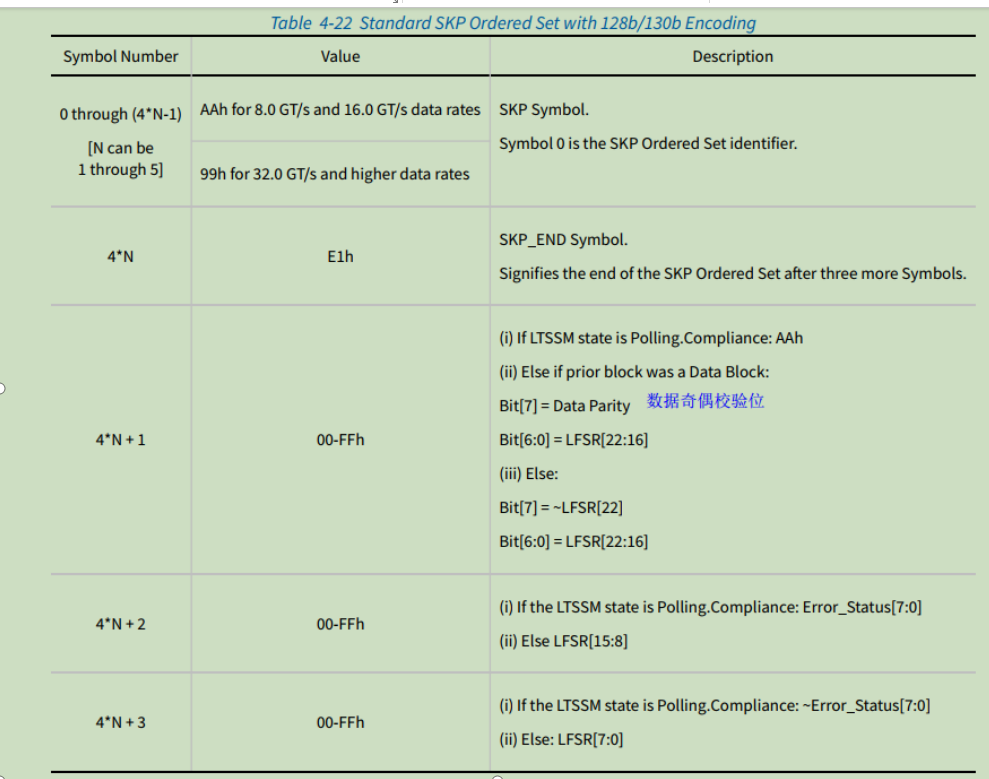

13. SKP 码奇偶校验位作用

128b/130b中有两类SKP; stanadrd SKP和control SKP;当以8.0 GT/s速率运行时,仅使用标准SKP有序集。 当以16.0 GT/s或更高速率运行时,标准和控制SKP有序集均会被使用。 当传输SKP有序集时,所有通道必须传输相同格式的SKP有序集——要么所有通道传输标准SKP有序集, 要么所有通道传输控制SKP有序集。(不能动态切换)

编辑

standard SKP 8Gbps 下parity(奇偶校验)规则:

• 当传输SDS有序集时,奇偶校验位被初始化。

• 在加扰完成后,随着数据块有效载荷的每一位传输,奇偶校验位随之更新。

• 紧跟在数据块后传输的标准SKP有序集中的数据奇偶校验位被设置为当前奇偶校验值。

• 标准SKP有序集传输完毕后,奇偶校验位会重新初始化。

当数据速率为 16.0 GT/s 或更高 时,标准 SKP Ordered Set(Standard SKP) 和 控制 SKP Ordered Set(Control SKP) 的 数据奇偶校验位(Data Parity bit) 是指:

该 Lane 上所有 数据块(Data Block) 的负载部分(payload)在加扰(scrambling)之后,按位计算的偶校验(even parity)。

并且每个 Lane 独立计算其奇偶校验

14. pcie link number 和lane number 区别

lane number金手指上实际的物理通道。

link number:一般为多端口设备,比如一个pcie rc可能支持多个pcie link(下游端口)

15. 接收端电器检测

在detect.active 阶段进行;

8.4.5.7 receiver detect;

接收器检测时集成在发送端的;

主要是判断是否纯在一个等效的直流阻抗负载(40~60Ω),符合zrx-dc参数。

推荐的Rx detection 操作流程

1. tx 电压必须稳定,确保信号不会有杂波抖动;

2. 然后对D+,D-差分线施加电压变化,这个电压需要满足Vtx-rcv-detect 参数需求(注施加一个共模电压)差模电压的值不会发生改变,这个操作来检测负载阻抗;如果检测到高阻抗,Zrx-hig-imp-dc-pos; Zrx-high-imp-dc-neg说明远端未连接。

a. 如果是开路(对端高阻)那么电压上身的速率就快,

b. 如果对端存在,导致电压变化很慢;

需要在D+,D-都检测,有一根线检测失败就认为失败;

原理:通过施加一个已知的电压跳变,然后在一定时间内检测电压变化速率,从而判断是否有接收端。

16, ts1 和ts2 使用时机,rtl中如何区分?