Chapter 10 Inductive DC–DC Converters

Chapter 10 Inductive DC–DC Converters

Design of Power Management Integrated Circuits - Bernhard Wicht

电感型DC-DC用电感做功率转换, 因为有开关, 也被称为开关型DC-DC. 电感型DC-DC相比LDO, 效率更高, 但是不那么"干净". 相比于电容型DC-DC (switched capacitor converter), 电感DC-DC理论能实现在任意转换比都效率高, 关键在于pulse-width modulation (PWM). 在轻载下会用pulse-frequency modulation (PFM) 来提高效率. 感谢电感的存在, converter不仅能实现降压, 也能实现升压.

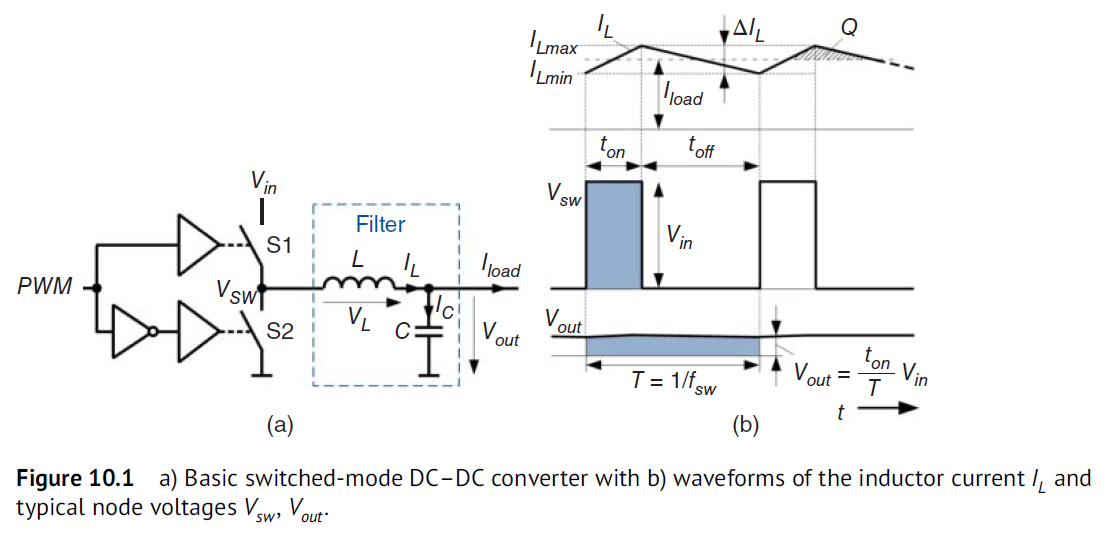

10.1 The Fundamental Buck Converter

buck converter结构如下图所示. S1和S2为complementary switch, 产生Vsw的PWM方波. LC tank的作用: 1) 把Vsw做 Low-pass filter. 2) 当上管S1关闭时, buffer energy to supply the load. DC-DC效率可达90%以上.

10.1.1 Inductor Current

电感电压

当S1开启和S2开启时, 电感电压, di/dt为

10.1.2 On-/Off-Times

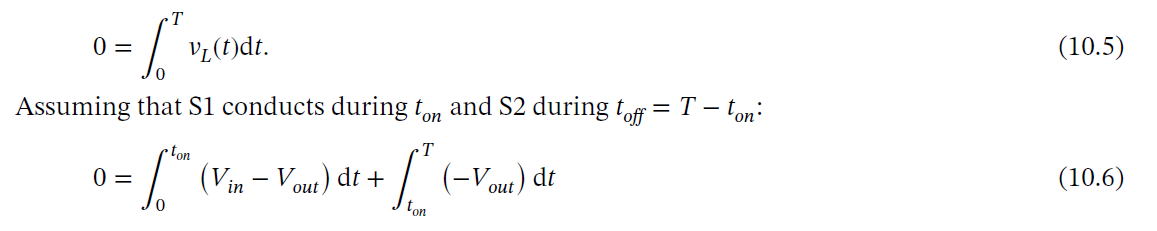

10.1.3 Volt-Second Balance

在稳态时, 电感电压在周期内积分为零.

因此可得

10.1.4 Voltage Conversion Ratio

由Eqn. (10.7), 我们可得converter 电压转换比 由 duty cycle D决定.

10.1.5 Current Ripple

电感电流峰峰值

电感电流ripple, ΔIL一般设计为Iload 的40% (i.e., ±20% with respect to Iload).

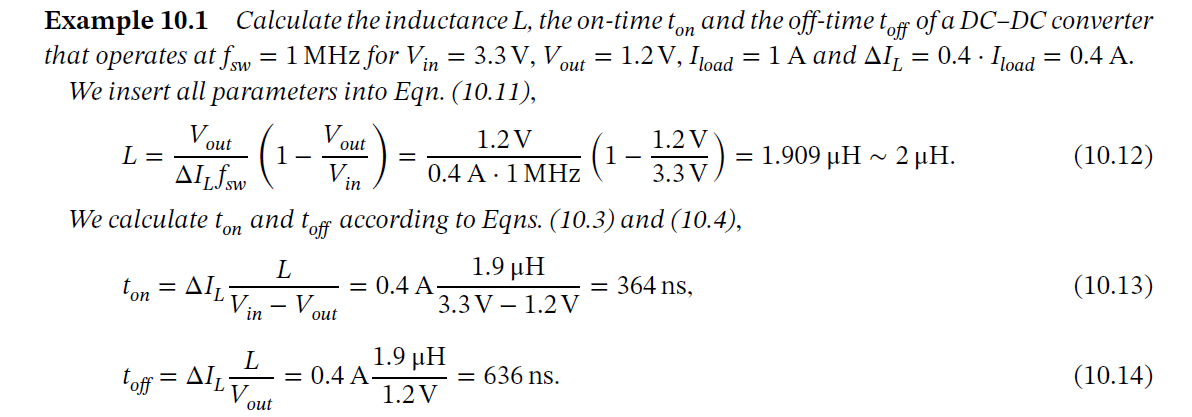

10.1.6 Inductor Sizing

对于给定电感电流ripple, 可通过增加频率, 减少电感尺寸.

10.1.7 Output Voltage Ripple

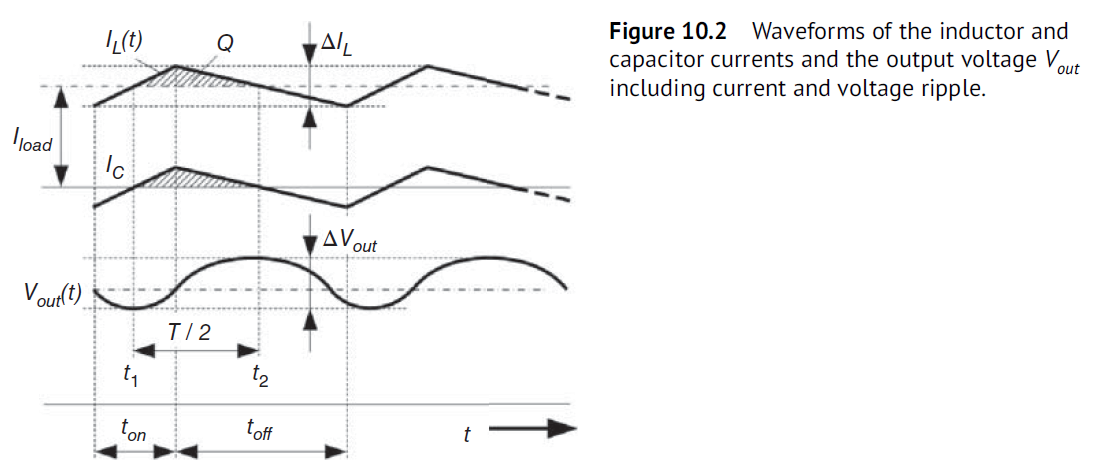

电容电流IC = IL − Iload, 因此Ic为三角波, 积分电容电流可得输出电容上的电荷

voltage ripple 峰峰值 ΔVout为

电感电流ripple ΔI, C越大, ΔVout越小.

另外输出电容的 equivalent series resistance (ESR)和inductance components (ESL) 也会贡献纹波. ESR上的电压为三角波, ESL电压表示电容电流的变化, 为方波.

10.1.8 Capacitor Sizing

给定ΔVout 和 ΔI, 输出电容最小值为

10.1.9 Switches

功率管采用half-bridge. 考虑寄生ringing, 集成功率器件至少选择20%以上VIN margin. 对于分离器件, Vdsmax需达到3Vin.

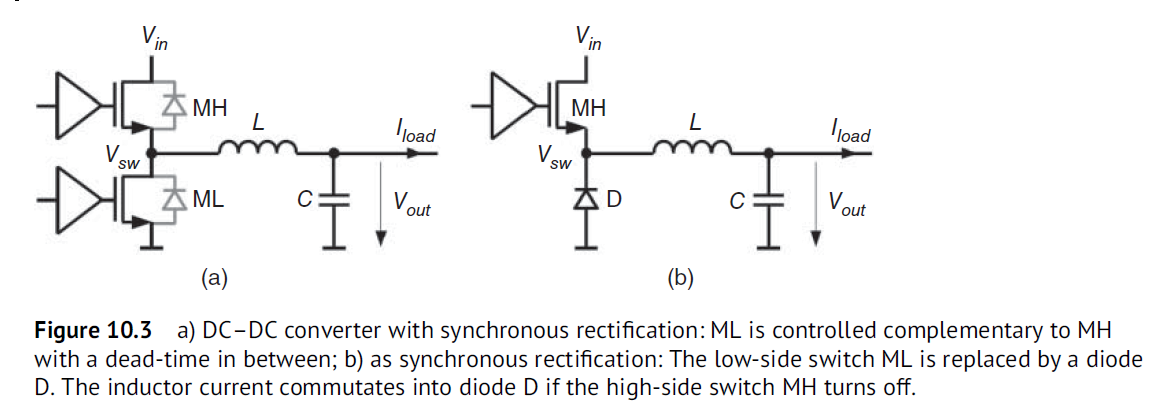

对于集成功率管, 需要合理设计Vdrv, W/L尺寸来minimize static和dynamic loss (详见Section 2.7). 半桥驱动需要deadtime (Section 2.8). deadtime时Iload通过下管的body diode, 需要小心寄生BJT (Section 3.3.1). 一些DC-DC采用分离的肖特基管并联下管, 由于肖特基管VF ~ 0.3V, 可防止body diode导通, 免受寄生BJT的影响.

10.1.10 Asynchronous Rectification

很多DC-DC用diode替换下管, 这样省去了下管, 驱动和dead-time control. 上管关闭, diode开始导通, 被称为asynchronous DC–DC converter. 带下管的称为synchronous converter. asynchronous DC–DC converter的power loss更高, 因为iLoad在toff时完全流过diode, 其loss为

Vout越低, D越小, Loss越大.

10.2 Losses and Power Conversion Efficiency

效率DC-DC的是关键指标

在Section 2.7, 详细讨论了power stage的loss, 包括conduction loss Pcond, switching loss Psw 和 gate charge loss Pgate. tr为transition time

在轻载时, gate charge loss占主要. 随着负载增加, conduction loss和switching loss逐渐增加. Section 2.7介绍了优化管子的 Rdson和Qgate. fsw, Vin, Soft switching techniques like resonant conversion and dead-time control, described in Section 2.9都可以减小loss.

10.3 Closing the Loop

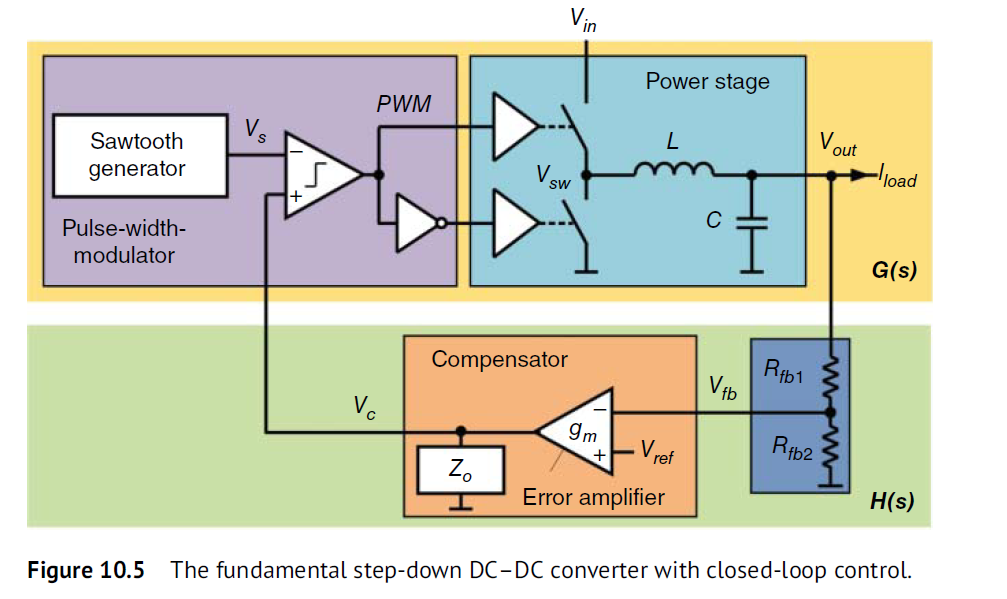

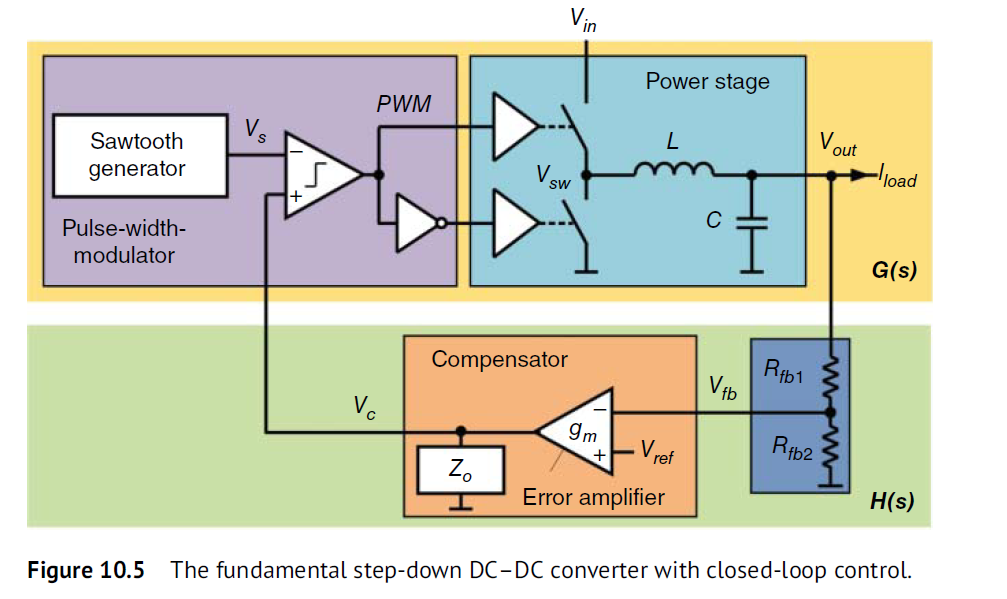

为了精准regulate输出电压, 需要添加控制环路. 如下图所示

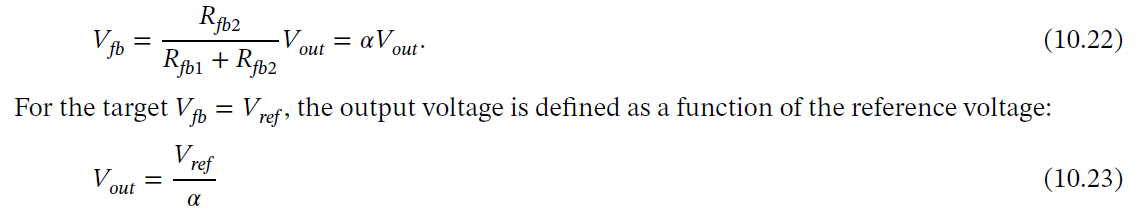

resistor divider分压Vout产生Vfb

Error Amplifier的输出Vc测量Vfb和Vref的误差. 需要补偿网络确保环路稳定.

Vc送入Pulse-width modulator, 产生占空比为D = ton/T的方波驱动功率管, 输出Vout. 电压模, 电流模, constant on-time和off time的控制会在下面讨论.

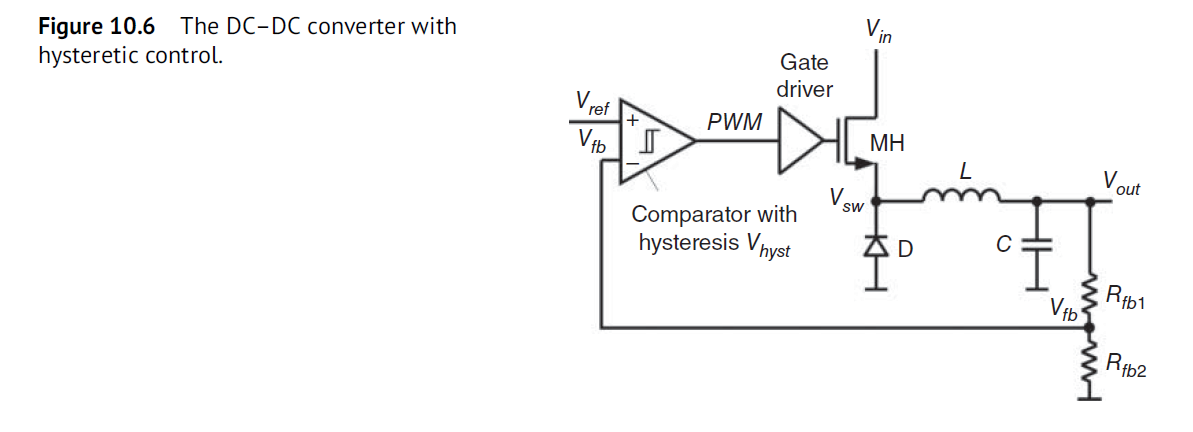

10.4 Hysteretic Control

迟滞控制是最直接的控制方式. 当Vout> Vtpu = Vref + Vhyst∕2, 上管关闭. 当Vout < Vtpl = Vref - Vhyst∕2, 上管开启.

为了减少输出ripple, 典型的hysteresis 值为20–100mV. hysteretic control没有固定频率, fsw取决于hysteresis, iLoad, L,C等参数.

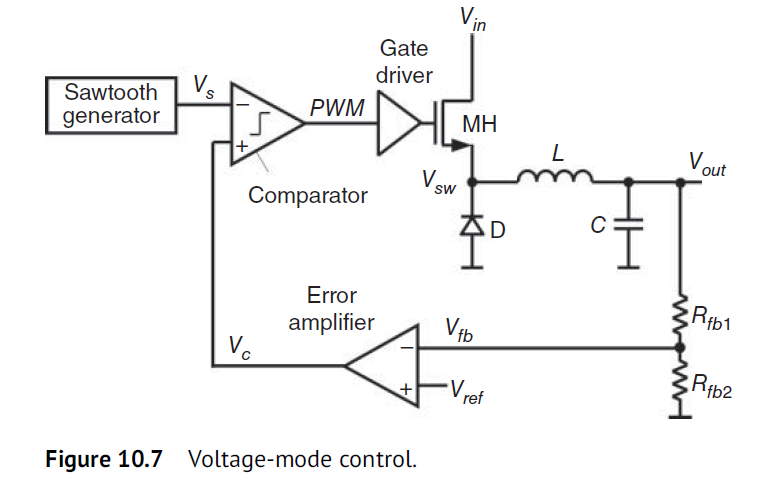

10.5 Voltage-Mode Control (VMC)

下图展示了电压模控制环路,

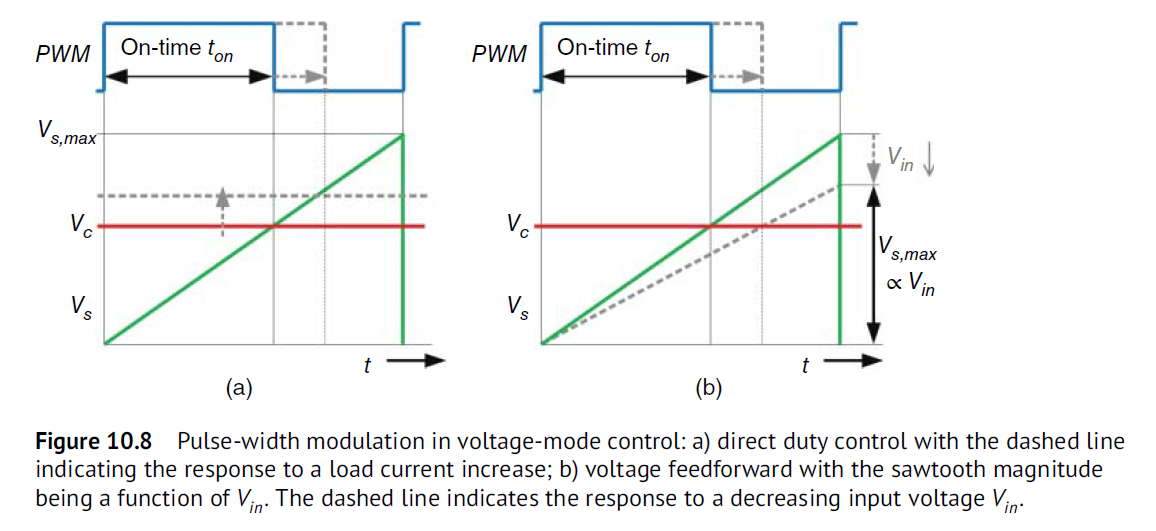

10.5.1 Direct Duty Control

如图Fig 10.8(a)所示, sawtooth的幅值为Vs,max, EA输出Vc可视为稳定信号, 因为加入LC和电容补偿. 每个新的switching周期, 即CLK上升沿来临, PWM变高, 即上管导通. Vs上升碰到Vc时, PWM变零, 上管关闭. duty cycle占空比D为

当负载变大, Vout下降, 导致Vc增加, 占空比D增加, 输出Vout增加.

10.5.2 Voltage Feedforward

direct duty control的缺点是 line regulation较差, 当Vin发生变化时, 需要经过LC filter, 才能体现在duty cycle D上. 可以让三角波幅度和Vin成正比, 引入voltage feedforward, 即电压前馈. 如图Fig 10.8(b)所示

当Vin下降时, Vs,max下降, 三角波上升斜率变缓, 占空比D变大, 这样电感能送更多能量 (这时电感电流斜率也下降). 稍后我们会推导Gvd和Gvin传输函数, 也可见电压前馈的作用.

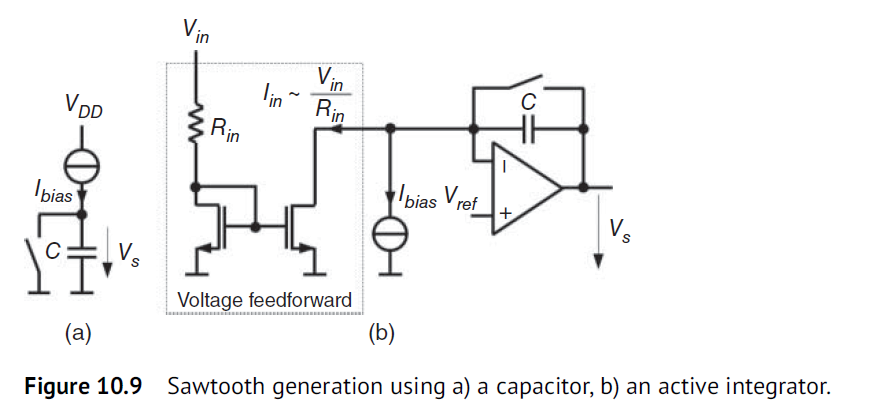

10.5.3 The Sawtooth Generator

三角波产生电路, 最简单的结构可用Fig 10.9(a), 即一个电流源给电容充电. 但由于Vs要从0V初始增加, 不一定能和EA输出Vc的共模电平能match. 可以通过在电容另外一端加入带驱动能力的基准解决 (注意source impedance). Fig 10.9(b)的active integrator是更好的方案. Vref为三角波初始值Fig 10.9(b)还能产生和输入电压Vin成正比的电流Iin = (Vin − VGS)/Rin ∼ Vin/Rin (假设 Vin ≫ VGS), 从而实现电压前馈. Ibias为DC bias电流.

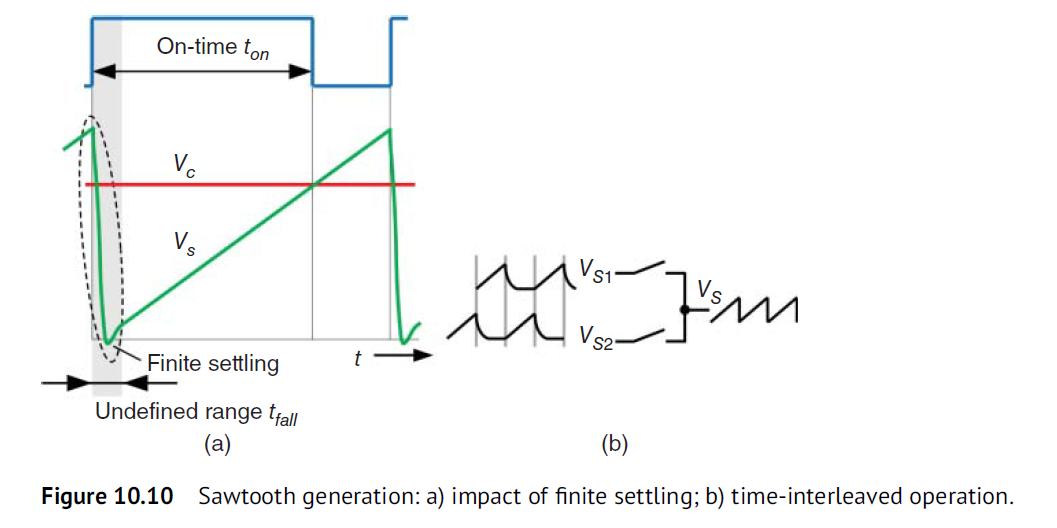

在开关on的一瞬间, 电容上电荷不能立刻被放掉, 因此限制了最小ton时间. settling time tfall 通常为10ns量级, 对于开关频率fs>>1MHz, 会影响占空比. 因此可以用两个三角波叠加产生三角波. 如图Fig 10.10所示, 或者用digital logic把两个PWM信号叠加到一起.

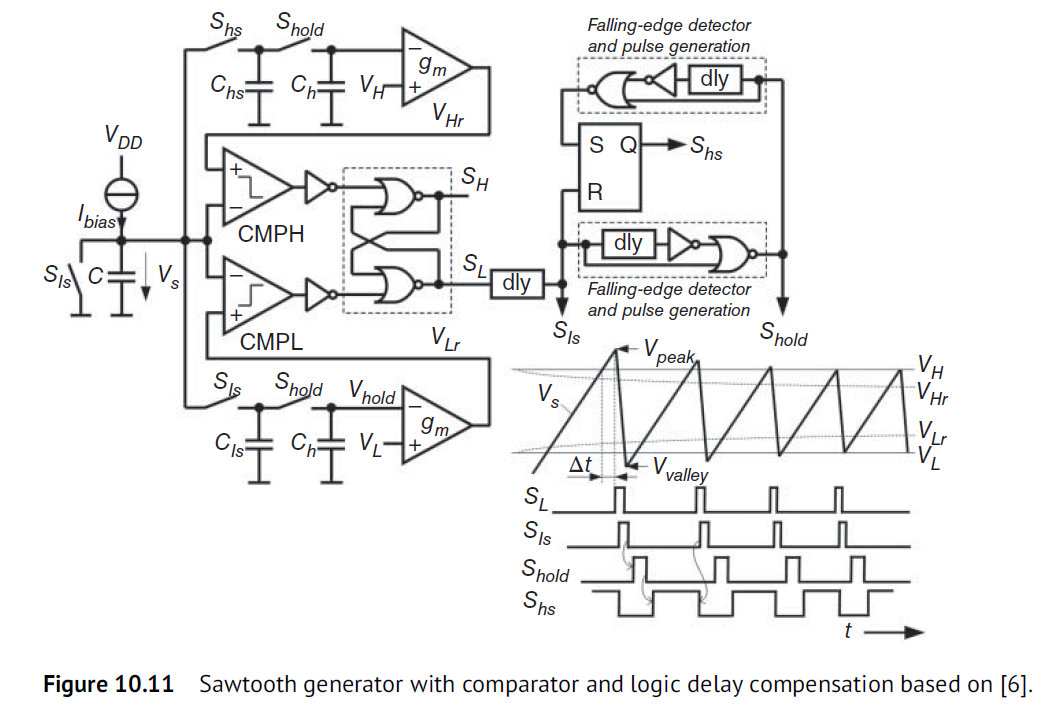

对于开关频率10MHz, 不仅是setting time, 比较器delay也会影响PWM占空比. Figure 10.11展示了补偿比较器和logic延迟的三角波产生电路. 两个gm运放形成负反馈, regulate三角波的峰峰值, VL和VH. 假设由于over discharging, Vvalley低于VL, 在VS falling时, SL=1, Sls store Vs on Cls. Sls=0 at Vvalley, 然后Shold=1, to sample Vvalley on Ch, Vhold=Vvalley和VL被gm运放放大, 因此VLr增加, 因此比较器CMPL下次翻转更快. 最终Vs valley电压=VL. 同理peak电压=VH.

详见[6] Cheng, L., Liu, Y., and Ki, W.H. (2014) A 10/30MHz fast reference-tracking buck converter with DDA-based type-III compensator. IEEE Journal of Solid-State Circuits, 49 (12), 2788–2799, doi: 10.1109/JSSC.2014.2346770.

10.5.4 The Error Amplifier

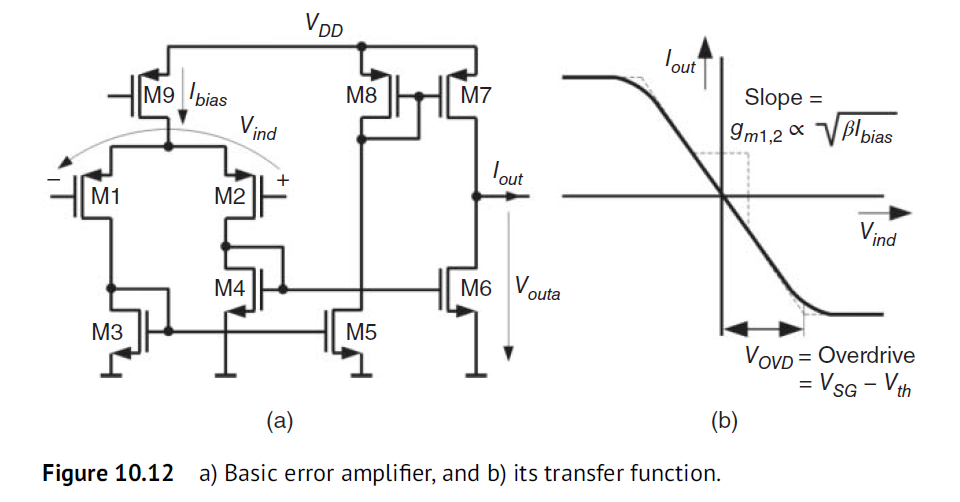

分离器件的EA设计常用op-amp, DC gain越高, error越小, 但是越难补偿. IC设计常用OTA如下图(a)所示, 因为无需输出buffer, 但需要注意resistive feedback divider对于EA补偿电路的影响. OTA的传输函数为Gm = Iout/Vind. Vind为输出电压差. GM正比于或者等于小信号跨导gm. gm由输入对管W/L和Ibias决定. 当输入电压差Vind超过输入对管overide电压(典型200mV)时, OTA可能饱和. 如下图(b)所示.

10.5.5 The Comparator

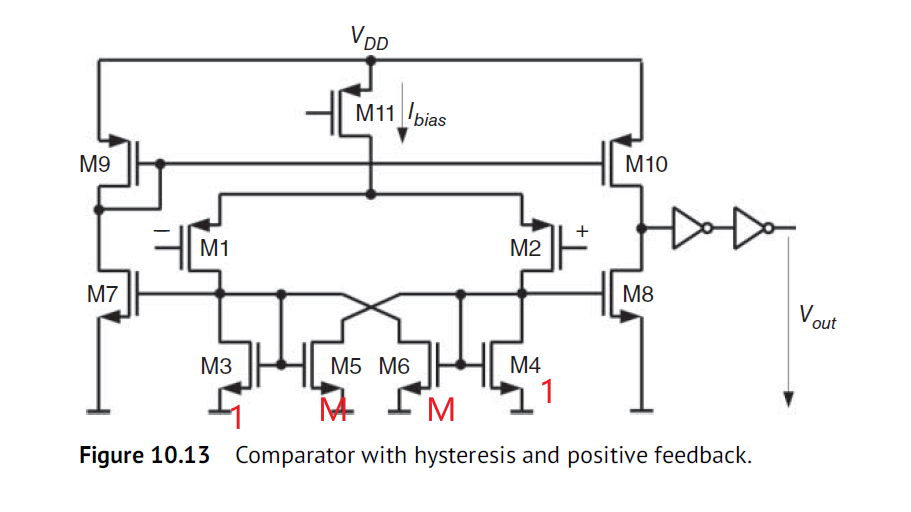

Figure 10.13 展示了典型比较器. 采用差分正反馈来实现低传输延迟和迟滞.

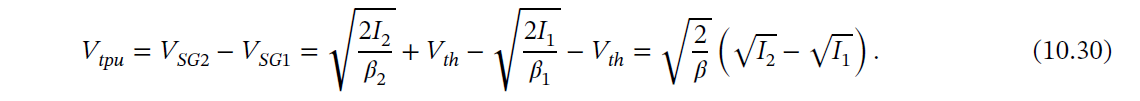

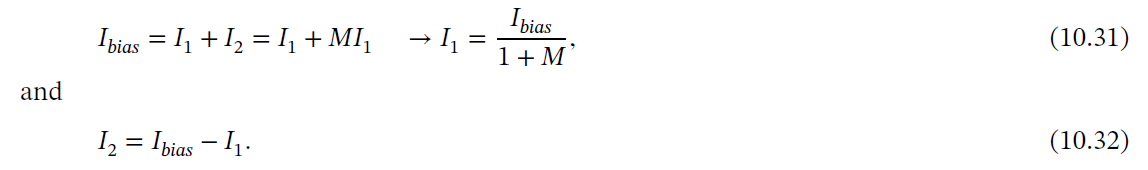

设Vind很大, M2关闭, M1 on, M1流过Ibias. M5想要sink I5 = M* I3, I3=I1. 当Vind减小时, 上翻转点upper trip point 发生在 I2=I5 = M*I1时刻,

由于对称性, 𝛽1 = 𝛽2 = 𝛽. I1和I2电流为

因此可求得Vtpu. 下翻转点lower trip point, Vtpl = −Vtpu. 因此迟滞为vhyst = Vtpu − Vtpl = 2Vtpu.

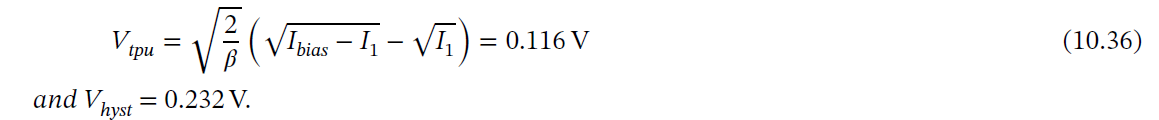

Eg 10.4. M=3, Ibias=10uA, 𝛽1 = 𝛽2 = 𝛽 = 200 μA/V2

可得

因此上翻下翻trip点

10.5.6 Closed-loop Transfer Function

DC-DC 环路由 the control-to-output (plant) transfer function G(s)和反馈传输函数H(s)组成

闭环传输函数:

Loop Gain很大时, 输出电压Vout由反馈系数𝛼决定.

10.5.7 Control-to-Output Transfer Function

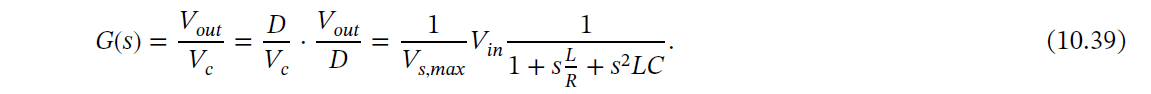

Vc到Vout的传输函数, the control-to-output (plant) transfer function G(s) 包括 PWM比较器和power stage. PWM比较器传函为D/Vc = 1/Vs,max

DC gain为Vin/Vs,max. Vs,max为三角波peak-peak值. LC在1/(2 𝜋√LC)引入双极点, phase以-40dB/dec下降

输出电容上的ESR产生零点 1/(Resr*C)

10.5.8 Line-to-Output Transfer Function

line-to-output transfer functions, 即Vin到Vout的传输函数为

line-to-output和control-to-output 都有双极点, 再加上EA controller引入积分行为, 在DC引入极点, 环路有三个极点. 因此需要至少两个零点, 通常需要三型补偿电路. Section 10.8有讨论.

10.6 Current-Mode Control (CMC)

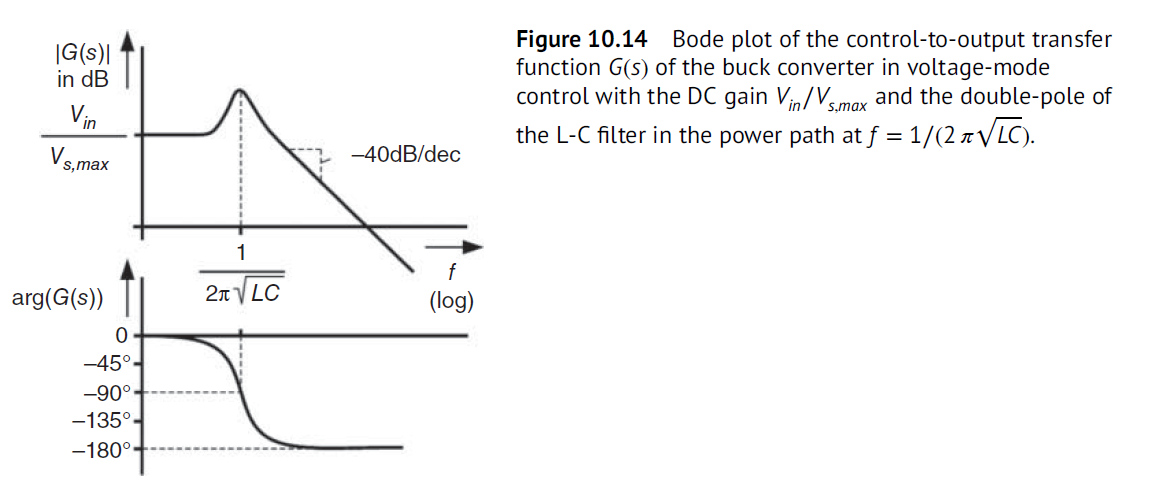

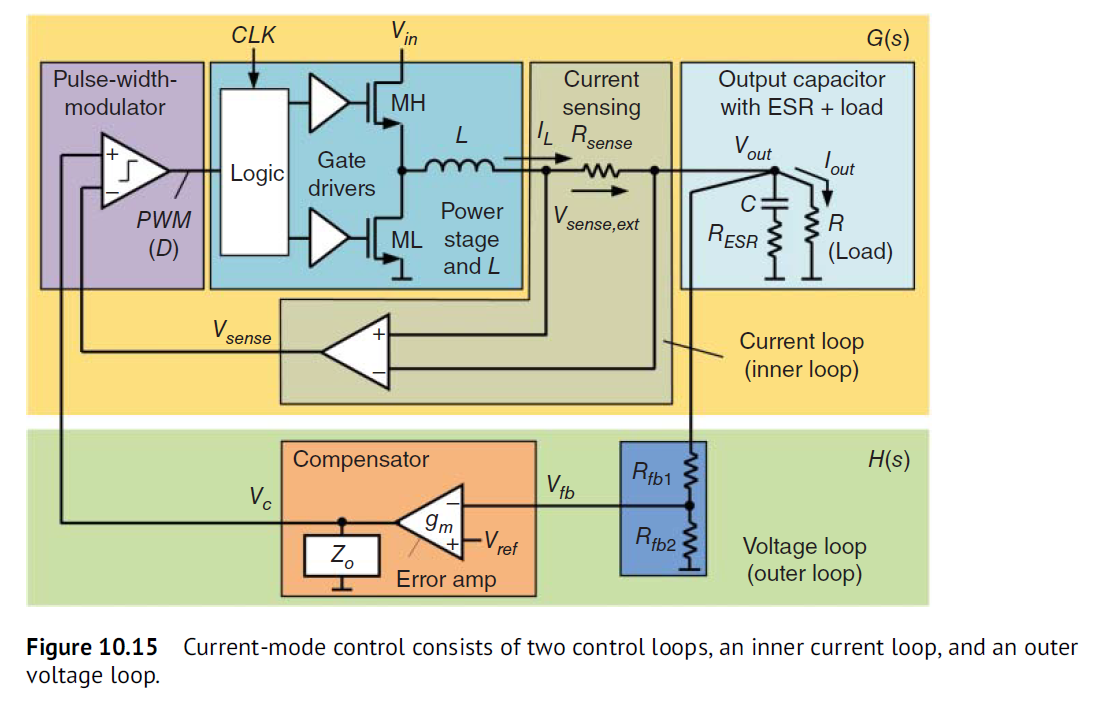

电压模是三角波Vs和Vc相比较, 形成PWM. 电流模如下图Fig 10.15所示. Vs替换成电感电流采样模块, Vsense ∝ IL, 因此传输函数Rsense = Vsense/IL. 电流采样环形成current or inner loop. 采样输出电压环路称为voltage or outer loop. 我们已经cover了 power stage, PWM比较器, current sensing (DCR or replica current).

Fig 10.16展示了重要波形. CLK上升沿来临时, PWM信号从0->1, 上管MH开启, 电感电流增加, 当Vsense电压超过error signal Vc时, 比较器将PWM 1->0, 因此上管关闭, 下管开启. Vsense开始下降. 电流模提供很好的line transient响应, 因为inner loop直接采样电感电流, 当输入电压Vin变化时, 电感电流立刻变化. 电流模另外的好处是可以通过限制Vc来限制电感电流. Vc和Vout成反比, 大负载会降低Vout, 抬高Vc. 通过限制Vc最大值, 能让Vsense和Vc碰撞点提前, 这样能限制Vsense平均值, 即电感电流, 输出电流.

10.6.1 Transfer Function of the Current Loop

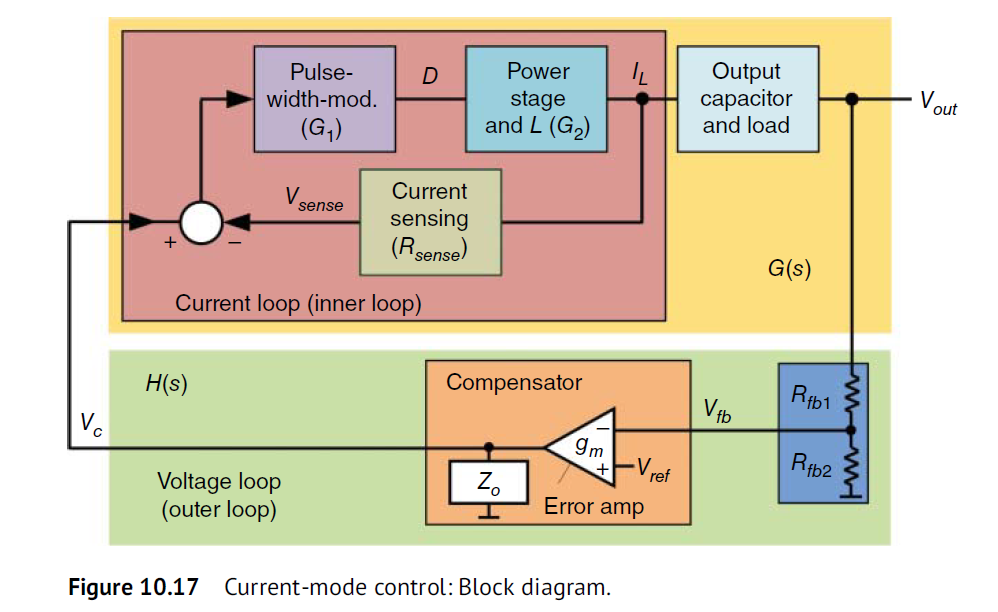

除了提高transient和限制输出电流, 电流模控制比电压模的优势在于 电流模为单极点系统. 如图Figure 10.17所示.

电流环 (inner loop)以Vc作为输入信号, 电感电流iL为输出信号.

G1和G2先不用管, Vsense和iL成正比. Rsense也限制了Vsense的headroom.

可得Vc到iL传函:

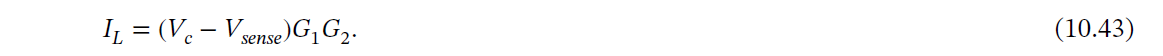

IL=Vc/Rsense. 这个式子很重要, 代表了电流环的作用. 当电流采样环路足够快时, Rsense可视为常量电阻. 因此电流模环路简化为Fig 10.18

10.6.2 Control-to-Output Transfer Function

由Fig 10.18 可知, the control-to-output transfer function G(s) 由1/Rsense和输出电容Cout/电阻Rout组成, 考虑Cout上的ESR

first-order这是一个单极点系统, 因此稳定性和频率补偿简单得多. 电流模可用type II补偿, 而电压模需要type III补偿.

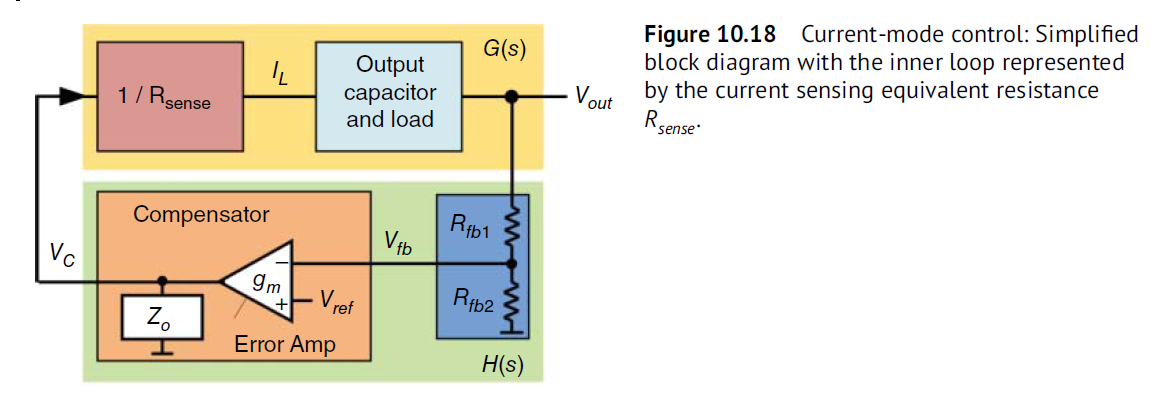

10.6.3 The Initial Spike

电感电流采样信号Vsense通常noisy, 在上管开启时, 通常有spikes. 多种因素会产生leading-edge spike: 陡峭的switching transient, 寄生电容, 寄生电感, 瞬时二极管blocking, 包括反向恢复. 在实践中, 会在上管开启时加入数字blanking, 防止被initial spike触发Vsense和Vc相碰. 典型的blanking time, tblank = 100 ns. 这个blanking time会限制DC-DC的占空比, 即最高频率. 电流模控制的DC-DC工作通常在5MHz以内, 对于带宽有限的电流采样模块(Section 6.6足够了). 根据占空比范围, 峰值电流模改成谷值电流模might提高开关频率.

10.6.4 Subharmonic Oscillations

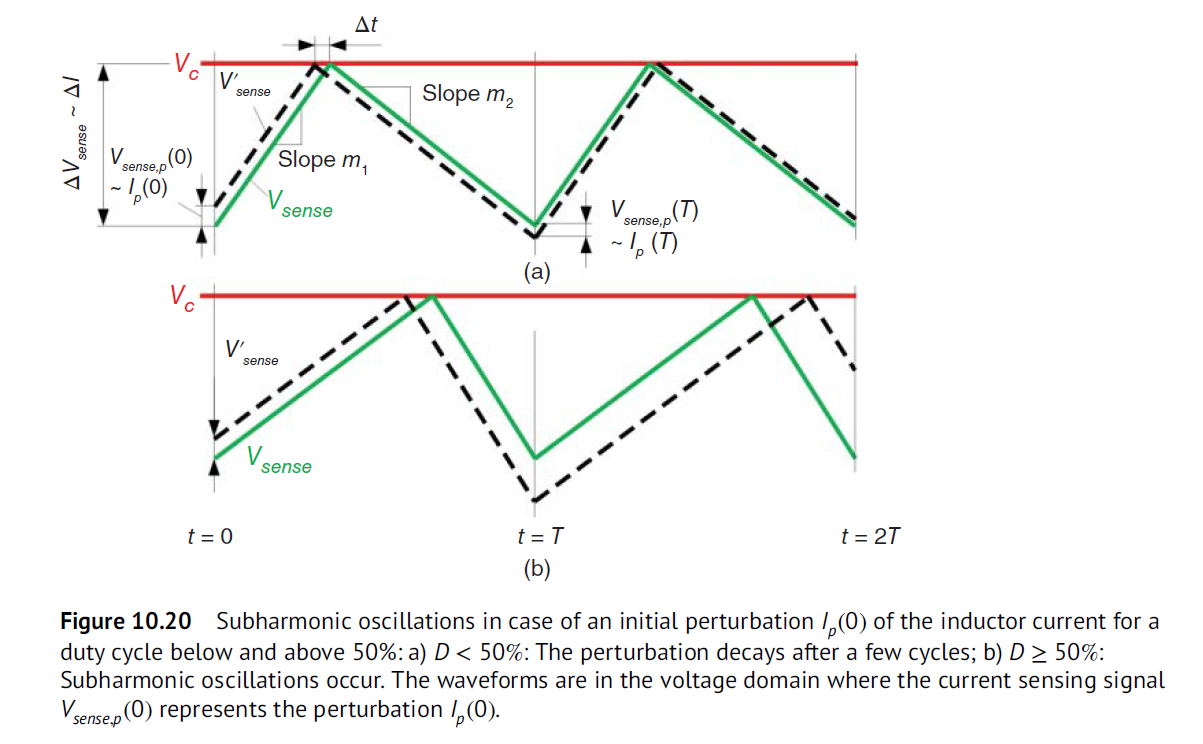

考虑电感电流有波动Ip, Vsense,p = V′sense − Vsense, 如下图所示. 当占空比D< 50%时, 扰动会逐渐减小. 当占空比D>= 50%时, 扰动会放大, 导致converter发生半周期震荡. 该现象称为次谐波震荡 (subharmonic oscillations).

ton和toff比例如下

N个周期后, 电感电流扰动为

为了让扰动decay, |Ip(T)| ≤ |Ip(0)|, 需要占空比D<0.5

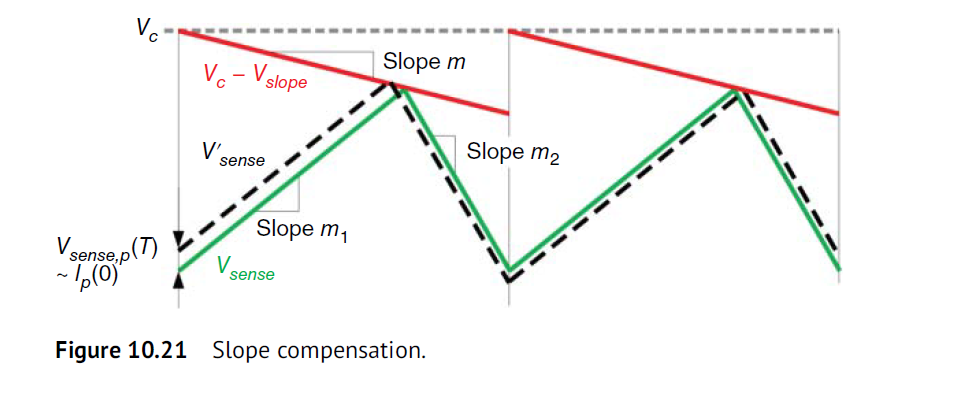

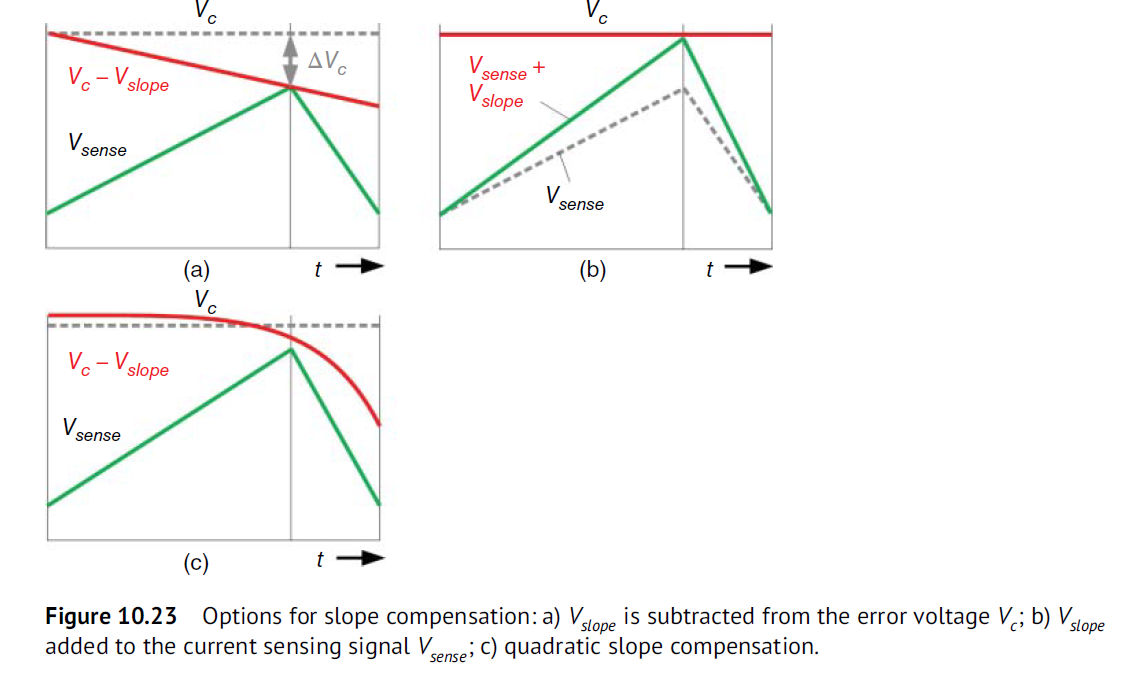

为了避免次谐波, 可用加入斜坡补偿, 如下图所示.

通过在Vc上加入负斜度m的斜坡, 这样即使占空比D>0.5, 扰动也会在几个周期内decay.

N个周期后, 扰动电流为

为了让扰动decay, 需要

考虑最恶劣情况, 100%占空比,  =0, 可得

=0, 可得

设计m为m2的一半, 或者更小, 即斜坡更狠, 这样次斜坡震荡就会被抑制.

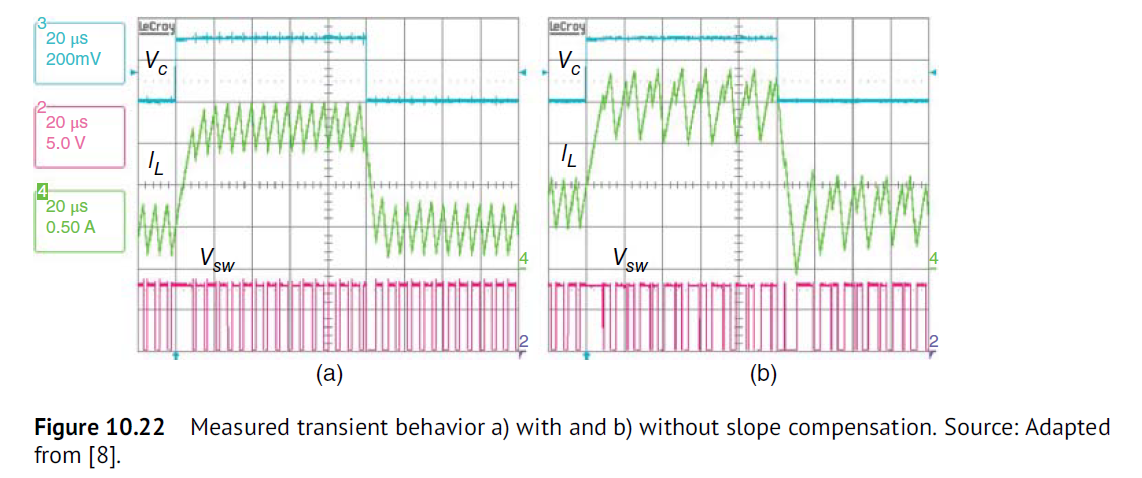

下图展示了次谐波震荡的波形

为了抑制次谐波震荡, 我们需要在Vc加入斜坡补偿, 如Fig 10.23所示, 可Vc上减去Vslope电压(a). 或者在Vsense上叠加Vslope电压 (b), 目的就是减小Vsense最大值ΔVc. 行为接近电压模控制, 导致transient响应变差. 另外Vsense和电感电流成正比, 斜坡补偿减少了Vsense最大值, 会导致load电流减小. Fig. 10.23c) 展示了quadratic (二次项)的斜坡补偿, quadratic 斜坡补偿在广泛占空比下, 允许更高的Vsense电压, 即iL更高.

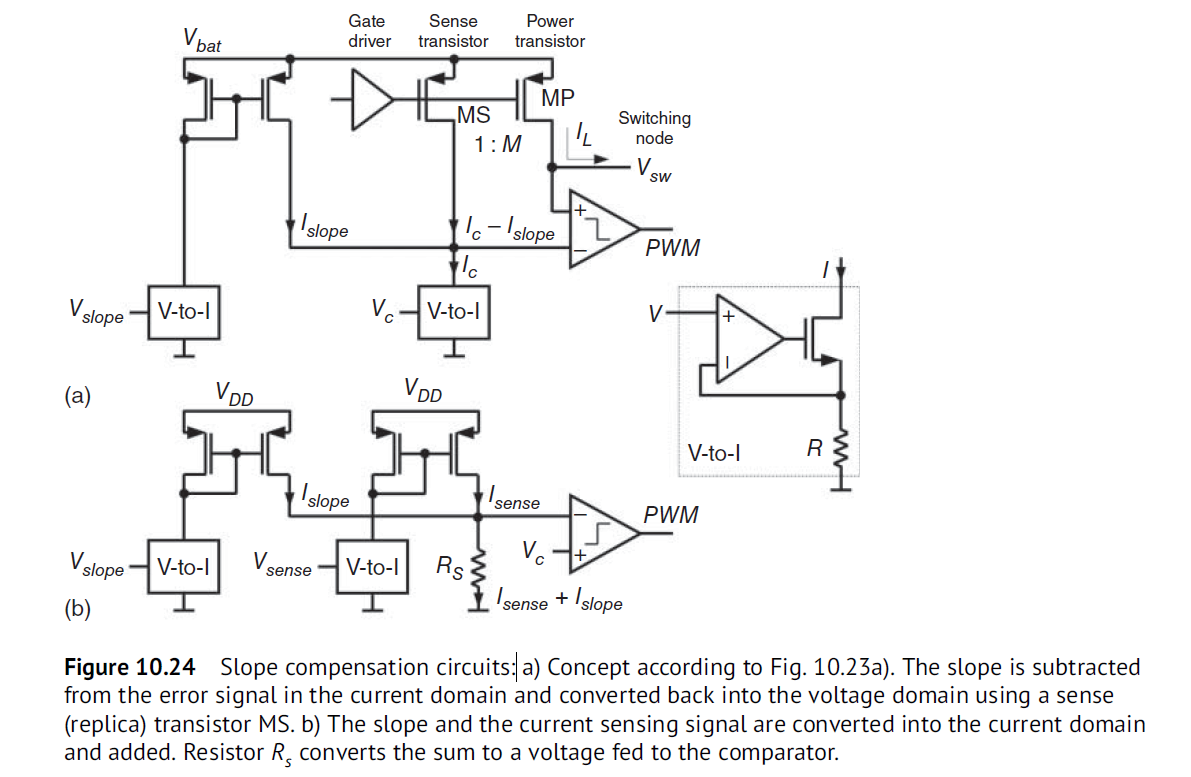

Fig. 10.23的电路实现如图Fig. 10.24. V-to-I模块将电压信号转化为电流信号. Fig 10.24(a)实现Fig 10.23(a), Vslope经V2I模块转化为Islope, 电流为Ic-Islope. replica sensing产生信号接到PWM比较器. 比较器正端VP看到的电压正比于slope-compensated error voltage即 M* Ron (Ic − Islope). Vslope可用电容+开关形成, 或者用电压模章节中介绍的active integrator. 比较器负端VN看到的电压正比于 Ron*iL. 当Vbat为高压时, 需要level shifter和保护电路. 注意PWM比较器的极性.

换成下管电流采样, 电压rating会降低, 需要保护PWM比较器的输入端. 仅采样下管电流可能不能满足buck, 但对于boost很适用了.

Fig. 10.24(b)的电路实现Fig. 10.23(b). slope信号叠加到电感电流上, Isense + Islope 通过Rs转化为电压, 再和Vc送到比较器进行比较产生PWM方波.

对于boost converter, 下管电流可做PWM产生器, Rs可换成下管开关. 为了更精准采样, 可用片外shunt电阻串联下管source和ground. 这样Isense替换为shunt, 不再需要了. Islope送入switching node.

Eg 10.6: 以Fig. 10.24b)为例设计, Rsense=1Ω.

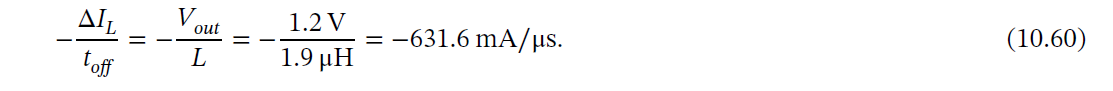

在off time电感电流下降斜率为

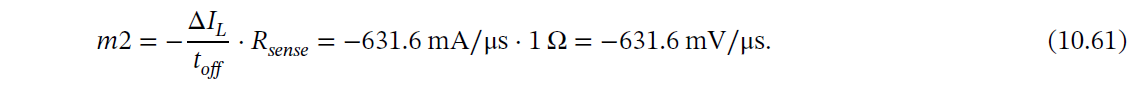

m2的电压斜率为

斜坡补偿斜率为

流出marin, 设计 m = m2/1.6 = −395mV/μs

下一步生成ramp电压Vs, 用电容+电流源Ic形成斜坡Vs. C=5pF

这里197.4mV/us应替换为395mV/μs.