飞腾D2000与FPGA结合的主板

UD VPX-404是基于高速模拟/数字采集回放、FPGA信号实时处理、CPU主控、高速SSD实时存储架构开发的一款高度集成的信号处理组合模块,采用6U VPX架构,模块装上外壳即为独立整机,方便用户二次开发。

UD VPX-404模块的国产率可达到100%,这一组合模块可完成高速ADC/光纤信号的实时采集、实时处理、实时存储、DAC/光纤实时回放,用户也可对FPGA进行二次开发、也可调用上位机API库完成界面的开发。

模块采用飞腾的CPU、复旦微的FPGA和SSD盘,实时存储的读写带宽为4.8GB/s,存储容量支持8TB/16TB/32TB/64TB配置(国产版本最大容量为32TB),并且内部采用标准文件管理方式,可通过千兆/万兆网口提供FTP或网盘访问功能。

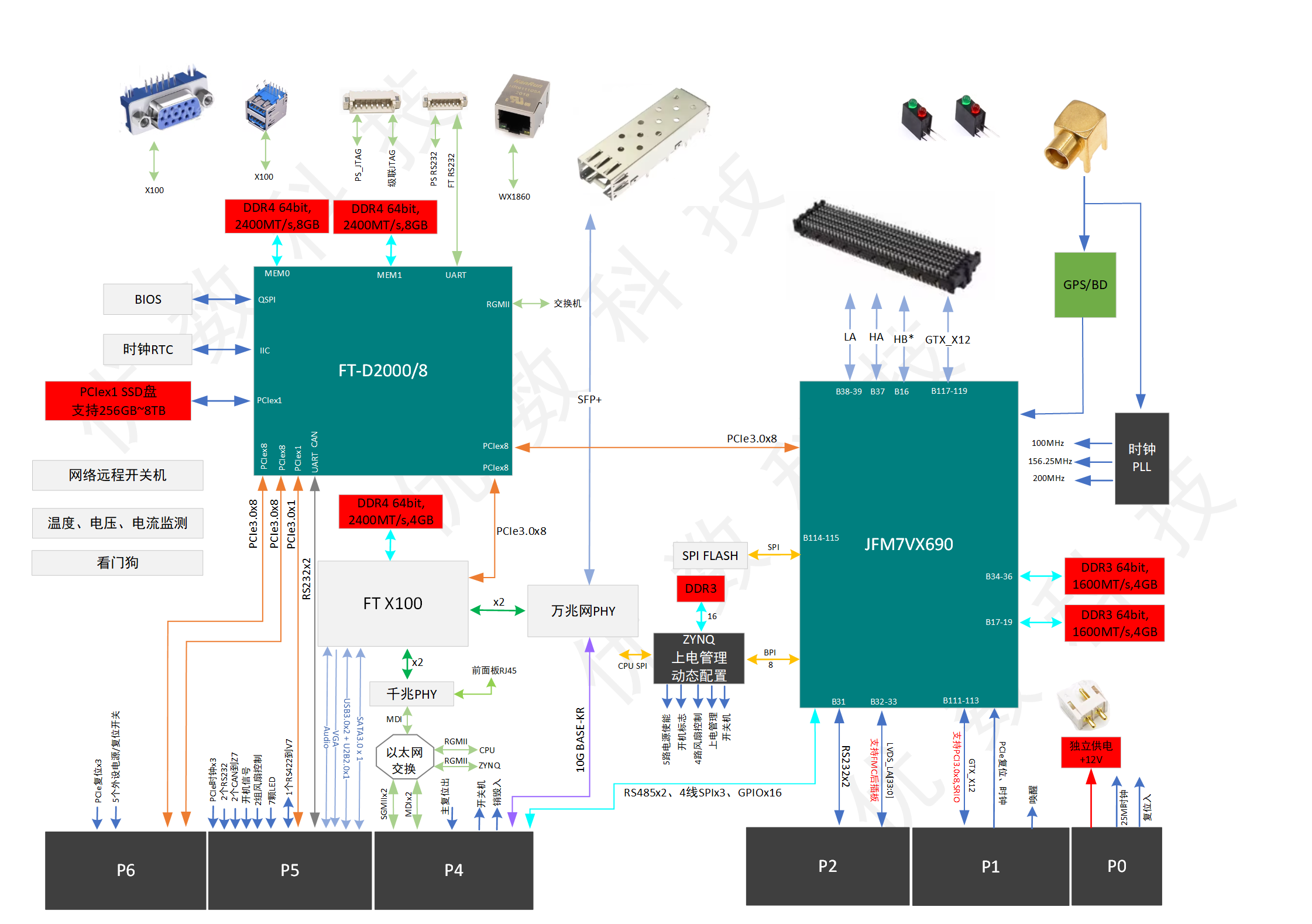

搭建存储平台,只需要1张主控板+1张存储板即可。主控板的原理框图如下:

操作系统支持麒麟V10和 ubantu18.04。

主控板 也可以作为690T的VPX信号处理板用。