带sdf 的post sim 小结

1.SDF文件主要内容

Delays(module,device,interconnect,port)

Timing checks(setup,hold,setuphold,recovery,removal,recrem)

Timing constrains(pathconstraint,skewconstraint,sum,diff)

Timing environment(arrival,departure,slack,waveform)

包括design,时间,工艺,版本,电压,温度,延时信息,基本单元延时信息等。

2. 若SDF文件很大,可以进行预编译,dut.sdf文件变为dut.sdf_c

+csdf+precomp+file+dut.sdf +csdf+precomp+dir+my_dir3. sdf反标要留意error和warning,+sdfverbose打印出来尽量消除。有些warning是必须要消除的,比如:

(1)Warning-[SDFCOM_NL] Negative Limit Not Allowed/Warning-[SDFCOM_CFTC] Cannot find timing check

可能的原因:你的 sdf 里是 recrem, 但库的 Verilog model 不是。看库文件里是不是要加什么宏定义,比如+define+NTC +define+RECREM

(2)Warning-[SDFCOM_TANE] TIMINGCHECK Annotation Not Enabled/Warning-[SDFCOM_IANE] IOPATH Annotation Not Enabled

可能的原因:netlist逻辑与sdf文件不一致,反标失败,timing check失败。

4. timing violation中确认可以忽略的加no timing check,比如打两拍中的第一拍的寄存器。关闭no timing check的两种方式:

(1)+optconfigfile+notiming.list

instance{top.dut.reg}{noTiming};(2)ucli

tcheck {top.dut.reg} SETUPHOLD -msg -disable5.在仿真过程中,经常会遇到传输延迟和惯性延迟,用来模拟实际的互联线延迟和模块间延迟。分布式延迟在仿真时一般都作为惯性延迟处理。

5.1 传输延迟

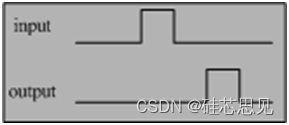

传输延迟一般为输入信号变化到对应输出信号变化经过的时间,不会对输入信号进行滤除处理,所以传输延迟是一种绝对延迟,这种延迟类似于物理传输线的延迟,在仿真中用于模拟连线延迟。如下图所示,输入一般不会被滤除。

5.2 惯性延迟

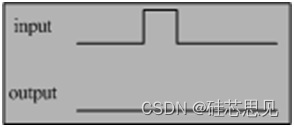

惯性延迟考虑了电路中存在大量的分布电容,信号在电路中传输存在对电容充放电效应,当输入较小宽度的脉冲将会被滤除,即不允许所有宽度小于指定延迟的脉冲通过电路单元,那么能够让对应输出有变化的最小脉冲宽度即为惯性延迟,是所有的电子器件均存在的一种延迟特性,因此为了使器件对输入信号的变化产生响应,信号变化后要维持足够长的时间,在仿真过程中,该延迟用于模拟元件延迟。一般原语、门单元、开关单元、连续赋值等中的延迟在模拟时均为惯性延迟。

如下图所示,输入较小脉冲宽度的信号被滤除:

在仿真elaboration时,增加如下仿真参数:“+transport_path_delays +pulse_r/<滤除百分比> +pulse_e/<滤除百分比>”等可在仿真阶段实现传输延迟的模拟,并且配置不同的滤除百分比,输出的结果也会有差异,一般输出结果为三种情况:滤除、通过、不定态

其中“+pulse_r”和“+pulse_e”后指定的参数表示允许通过和滤除的信号的宽度占指定延迟的百分比。例如,如果指定延迟为5ns,参数为“+pulse_r/40”和“+pulse_e/80”(其中的40和80为百分比),那么小于2ns(5x(40%))的信号将被滤除,大于等于4ns(5x(80%))的信号将可以通过,介于两者之间的信号将输出不定太,如下例中data_in的第一个脉冲信号小于2ns被滤除,不能输出至data_out。第二、三个脉冲信号宽度均大于或等于4ns,所以均有效输出,第四个脉冲宽度为3ns,介于2ns和4ns之间,所以不能被有效输出,此时输出为不定态。