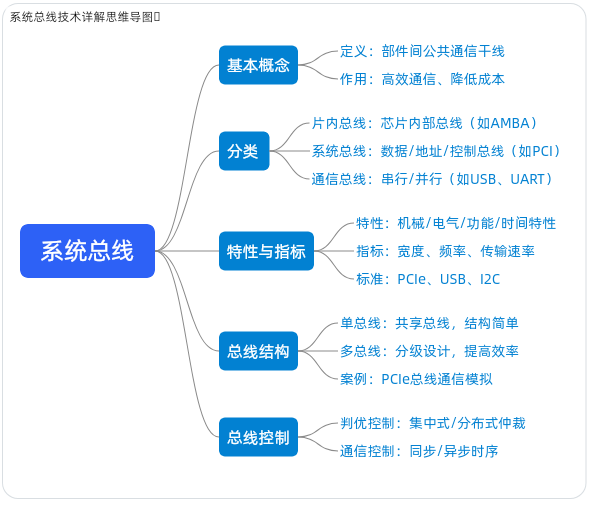

《计算机组成原理》第 3 章 - 系统总线

目录

3.1 总线的基本概念

3.2 总线的分类

3.2.1 片内总线(On-Chip Bus)

3.2.2 系统总线(System Bus)

3.2.3 通信总线(Communication Bus)

3.3 总线特性及性能指标

3.3.1 总线特性

3.3.2 总线性能指标

3.3.3 总线标准

3.4 总线结构

3.4.1 单总线结构

3.4.2 多总线结构

3.4.3 总线结构举例(PCIe 总线)

3.5 总线控制

3.5.1 总线判优控制

3.5.2 总线通信控制

3.6总结

3.1 总线的基本概念

总线(Bus) 是计算机系统中各部件之间传输信息的公共通信干线,由导线组成。它就像计算机的 “血管”,负责在 CPU、内存、输入输出设备等部件之间传输数据、地址和控制信号。

核心作用:实现部件间的高效通信,避免复杂的直接连接,降低硬件成本并提高系统扩展性。

3.2 总线的分类

3.2.1 片内总线(On-Chip Bus)

- 定义:芯片内部的总线,用于连接芯片内的各个功能模块(如 CPU 内部的 ALU、寄存器等)。

- 特点:速度极快,与芯片工艺深度绑定。

- 案例:ARM 处理器内部的 AMBA 总线(AXI、AHB 协议)。

3.2.2 系统总线(System Bus)

- 定义:计算机主机内连接各插件板的总线,分为三类:

- 数据总线(Data Bus):传输数据信息,宽度决定 CPU 一次能处理的数据量(如 32 位 / 64 位)。

- 地址总线(Address Bus):传输存储单元或 I/O 端口地址,宽度决定系统最大寻址空间(如 32 位地址总线可寻址 4GB)。

- 控制总线(Control Bus):传输控制信号(如读 / 写命令、中断请求等)。

- 案例:PCI 总线(Peripheral Component Interconnect)。

3.2.3 通信总线(Communication Bus)

- 定义:用于计算机系统之间或计算机与外部设备之间通信的总线。

- 分类:

- 串行总线:逐位传输(如 USB、UART)。

- 并行总线:多位同时传输(如 IEEE 1284 并口)。

- 案例:USB 4.0 总线(传输速率高达 40Gbps)。

3.3 总线特性及性能指标

3.3.1 总线特性

- 机械特性:物理连接方式(如插头插座的引脚数、排列方式)。

- 电气特性:信号的电压范围、传输方向、时序关系。

- 功能特性:每根信号线上的信号功能(如地址、数据、控制)。

- 时间特性:信号的时序关系(可用时序图描述)。

3.3.2 总线性能指标

| 指标 | 含义 |

|---|---|

| 总线宽度 | 数据总线的位数(如 32 位、64 位) |

| 时钟频率 | 总线的工作频率(单位:MHz) |

| 传输速率 | 每秒传输的数据量(MB/s),公式:(总线宽度/8) × 时钟频率 |

| 负载能力 | 总线上能挂接的设备数量 |

计算案例:

若总线宽度为 64 位,时钟频率为 100MHz,则传输速率为:

(64/8) × 100MHz = 800MB/s

3.3.3 总线标准

- 定义:为协调总线设计制定的规范(如电气特性、时序协议等)。

- 常见标准:

- PCIe(Peripheral Component Interconnect Express):高速串行总线,用于显卡、SSD 等。

- USB(Universal Serial Bus):通用串行总线,用于外设连接。

- I2C(Inter-Integrated Circuit):低速串行总线,用于芯片间通信(如传感器)。

3.4 总线结构

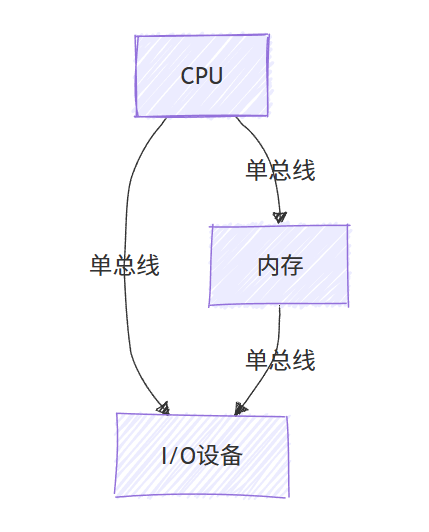

3.4.1 单总线结构

- 原理图:

- 特点:

- 所有部件共享一条总线,结构简单但效率低(存在总线竞争)。

- 适用于小型系统(如早期微型计算机)。

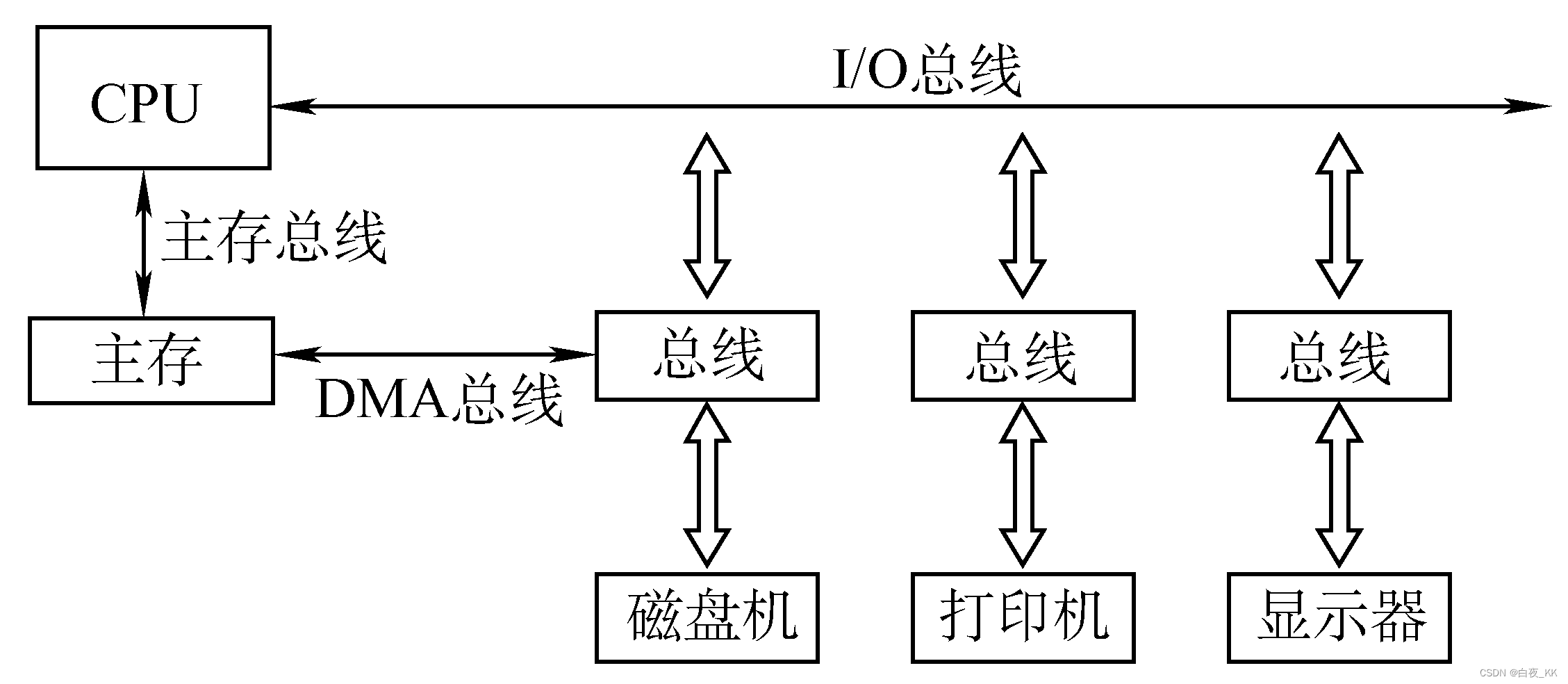

3.4.2 多总线结构

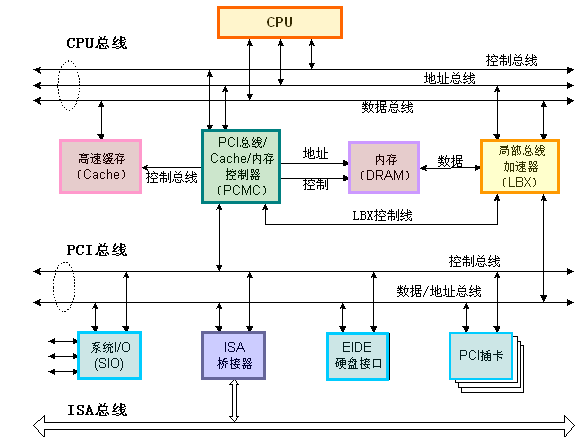

- 三总线结构示意图:

- 特点:

- 按速度分级设计总线,提高系统效率。

- 典型案例:现代 PC 的总线结构(包含 PCIe、USB 等多总线)。

3.4.3 总线结构举例(PCIe 总线)

Java 代码模拟 PCIe 设备通信:

/*** PCIe总线通信模拟* 功能:主设备(CPU)向从设备(显卡)发送数据*/

public class PCIeSimulation {// 模拟PCIe总线宽度(64位)private static final int BUS_WIDTH = 64;// 模拟总线时钟频率(1GHz)private static final int CLOCK_FREQ = 1_000_000_000;public static void main(String[] args) {// 主设备(CPU)发送数据byte[] dataToSend = {0x01, 0x02, 0x03, 0x04, 0x05}; // 示例数据(5字节)int deviceAddress = 0x1000; // 设备地址// 模拟总线传输过程sendDataOverPCIe(deviceAddress, dataToSend);System.out.println("数据传输完成!");}/*** 通过PCIe总线发送数据* @param address 目标设备地址* @param data 待发送数据*/private static void sendDataOverPCIe(int address, byte[] data) {// 解析总线宽度对应的单次传输最大字节数(64位=8字节)int maxTransferSize = BUS_WIDTH / 8;int totalBytes = data.length;System.out.println("开始通过PCIe总线传输数据...");System.out.println("总线宽度:" + BUS_WIDTH + "位,时钟频率:" + CLOCK_FREQ/1000000 + "MHz");System.out.println("目标设备地址:0x" + Integer.toHexString(address));// 分块传输数据(模拟实际突发传输)for (int i = 0; i < totalBytes; i += maxTransferSize) {int end = Math.min(i + maxTransferSize, totalBytes);byte[] chunk = Arrays.copyOfRange(data, i, end);// 模拟时序控制(简化版)simulateClockCycle();System.out.println("传输第 " + (i/maxTransferSize + 1) + " 块数据:" + Arrays.toString(chunk));}}/*** 模拟总线时钟周期(简化时序逻辑)*/private static void simulateClockCycle() {try {// 模拟时钟周期耗时(1ns)Thread.sleep(0, 1);} catch (InterruptedException e) {e.printStackTrace();}}

}

3.5 总线控制

3.5.1 总线判优控制

- 作用:解决多个设备同时请求总线时的竞争问题。

- 分类:

- 集中式控制:由中央仲裁器统一管理(如链式查询、计数器定时查询)。

- 分布式控制:各设备自带仲裁逻辑,无中央仲裁器。

链式查询算法模拟:

"""

链式查询总线仲裁模拟

设备优先级:设备0 > 设备1 > 设备2

"""

class ChainArbiter:def __init__(self, num_devices):self.devices = [False] * num_devices # 设备请求状态(False=未请求,True=请求中)self.grant_line = 0 # 授权信号当前位置(从0开始)def request_bus(self, device_id):"""设备发起总线请求"""if 0 <= device_id < len(self.devices):self.devices[device_id] = Trueprint(f"设备{device_id}发起总线请求")else:print("无效设备ID")def grant_access(self):"""仲裁器按优先级分配总线"""for i in range(len(self.devices)):if self.devices[i]:# 授权给当前设备self.grant_line = iself.devices[i] = False # 清除请求print(f"总线授权给设备{self.grant_line}")returnprint("无设备请求总线")# 测试案例

if __name__ == "__main__":arbiter = ChainArbiter(3)arbiter.request_bus(2) # 低优先级设备请求arbiter.request_bus(0) # 高优先级设备请求arbiter.grant_access() # 应授权给设备0arbiter.grant_access() # 设备2此时请求已被设备0覆盖,无请求则提示

3.5.2 总线通信控制

- 作用:协调总线上设备的通信时序,确保数据正确传输。

- 通信方式:

- 同步通信:由统一时钟信号控制传输节奏(如 PCI 总线)。

- 异步通信:用应答信号控制传输(如 USB 总线)。

同步通信时序模拟(Java 代码):

/*** 同步总线通信时序模拟* 功能:主设备与从设备通过时钟信号同步传输数据*/

public class SynchronousCommunication {private static int clockCycle = 0;public static void main(String[] args) {int[] data = {0xA1, 0xB2, 0xC3}; // 待传输数据communicateWithClock(data);}private static void communicateWithClock(int[] data) {for (int d : data) {clockCycle++;System.out.println("时钟周期 " + clockCycle + ":");System.out.println("- 主设备发送地址和数据:0x" + Integer.toHexString(d));System.out.println("- 从设备在时钟上升沿接收数据");System.out.println("---------------------------");}}

}

3.6总结

系统总线是计算机硬件的核心组成部分,理解总线分类、结构和控制机制对掌握计算机体系结构至关重要。通过本文的代码案例,读者可动手模拟总线通信过程,加深对理论知识的理解。实际开发中,总线协议(如 PCIe)的实现更为复杂,需结合具体硬件文档进行开发。