AG32VH 系列应用指南

AG32VH 系列应用指南

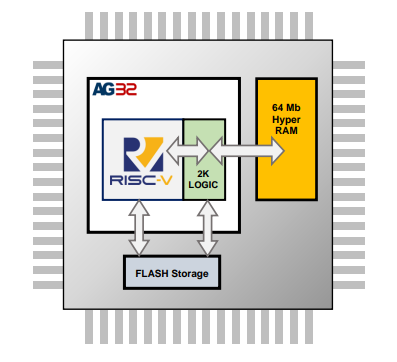

AG32VH 系列 MCU,是 AGM AG32 产品系列中,嵌入大容量 PSRAM(HyperRAM)作为 应用缓存的产品系列。在 AG32 处理器内核的基础上,利用片上 FPGA 的部分逻辑资源,实现 HyperBus 接口,连接并使用 64 Mbit PSRAM。器件示意图如下:

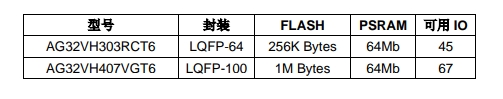

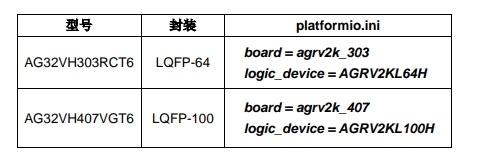

订货型号

HyperRAM 信息

嵌入 PSRAM 为 Winbond 64 Mb HyperRAM,型号:W956A8。具有以下特性:

- 接口:HyperBus

- 供电:2.7v ~ 3.6V

- 最大时钟频率:200 MHz

- 双倍数据速率(DDR)最大:400 MT/s

- 8 位数据总线

- 运行温度:-40 ~ 85 ℃

关于 HyperBus

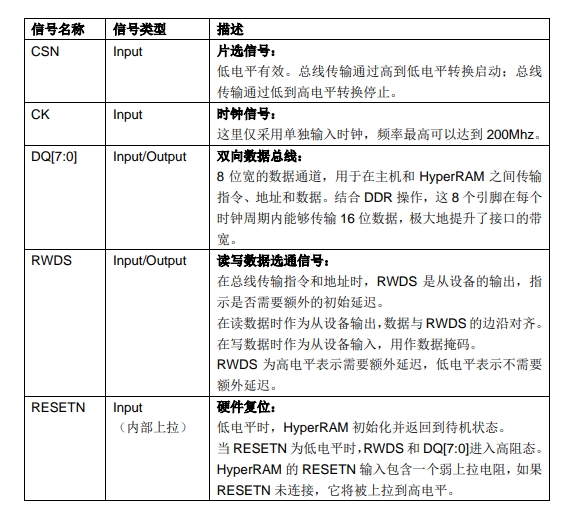

HyperBus 接口是一种高性能、低引脚数的 DDR(双倍数据速率)接口,旨在为主机控制 器和外设(如闪存、SRAM 等)之间提供高效的数据传输。该接口采用 12 个信号引脚,包括一 个差分时钟对(或单端)、一个读写数据选通(RWDS)信号、一个片选(CS#)信号以及 8 个双向数据(DQ)信号。

AG32 MCU 通过自定义 HyperBus 接口连接到 W956A8 上,连接信号列表如下:

AG32 与 HyperRAM 的连接

AG32VH 系列器件,AG32 MCU 的 IO 在器件内部连接以上 HyperRAM 接口。其中 RWDS 接口要从外部 2 个管脚连通(通过 PCB 布线连接)。具体管脚请参考后面 Pin-out 部分。

另外,电源管脚 VDD33 要单独用磁珠与 PCB 上其它电源做隔离,以确保高频设计的稳定

性。

软件设计

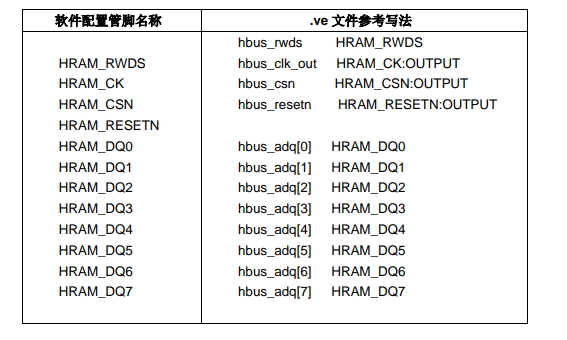

在 AG32VH 的软件设计中,管脚配置文件.ve 要按照 HyperRAM 接口定义好的名称进行 分配,参考下表:

软件中的 platformio.ini 文件,要按如下设置:

参考设计

在 AG32 SDK 中,集成了关于 AG32VH 系列的参考设计,在 Example 目录中。

文件

- ahb2hbus.v:将 AHB 总线转换为 HyperBus 总线。

- hram_ip.v:将 ahb2hbus 模块与 MCU 内核集成。

- hram.ve:时钟定义和引脚分配。

- hram.sdc:时序约束文件,对实现最高 Fmax 至关重要。

- 必须通过锁相环(PLL)为 HyperRAM 提供 2 路时钟:

- HyperBus 时钟:频率必须等于或高于 MCU 系统时钟,最大频率为 200MHz。

- 移相 90 度的 HyperBus 时钟。

- 支持 2 种访问方式:

- 直接读写:使用更便捷,但数据速率仅为 20-30MB/s。

- 使用 DMA(直接内存访问):便捷性较低,但数据速率可达 200MB/s 以上。该 DMA 功能包含在参考设计中,并非 MCU 内核中的系统 DMA 控制器。

- w 2K FPGA 逻辑资源占用 600 多 LEs;双向 2 个 FIFO 缓存,占用 2 个 M9K RAM; 同时和 MCU 共用 1 个 PLL。

在此基础上,我们还提供了 RGB 显示屏驱动的参考设计,支持 RGB888/RGB565 接 口,并集成了 LVGL 嵌入式图像库 demo。

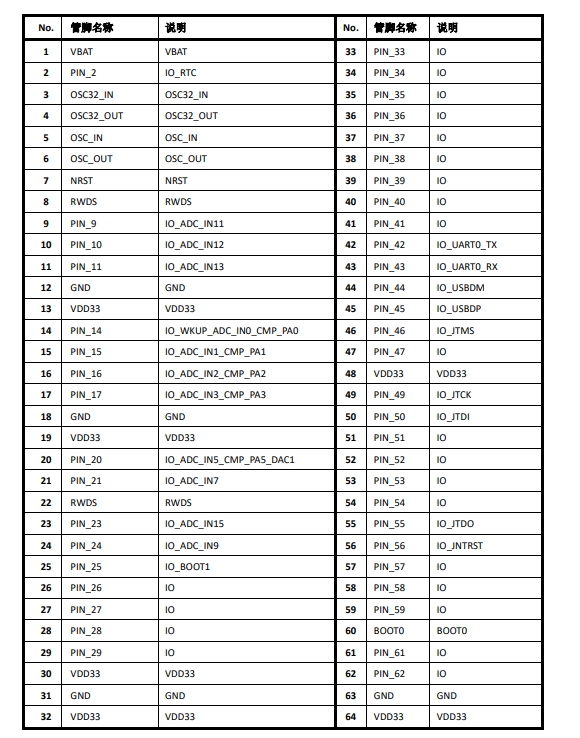

AG32VH303RCT6 Pin-Out

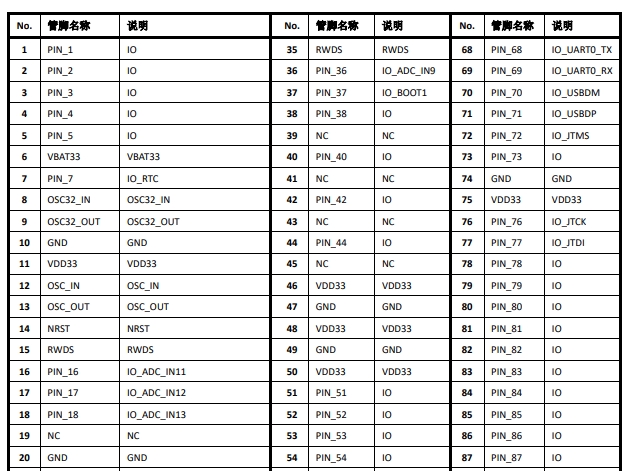

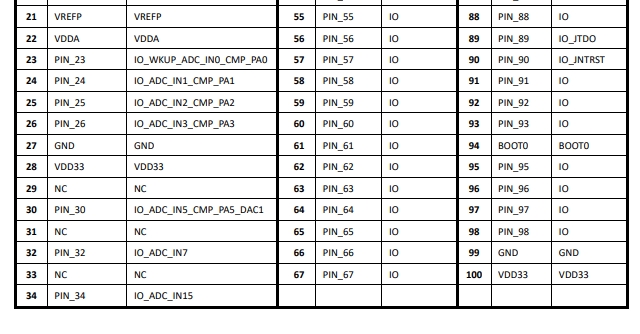

AG32VH407VGT6 Pin-Out

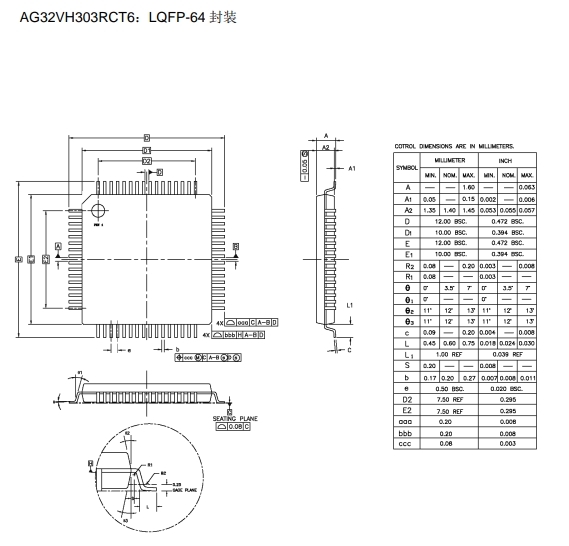

AG32VH 系列封装图

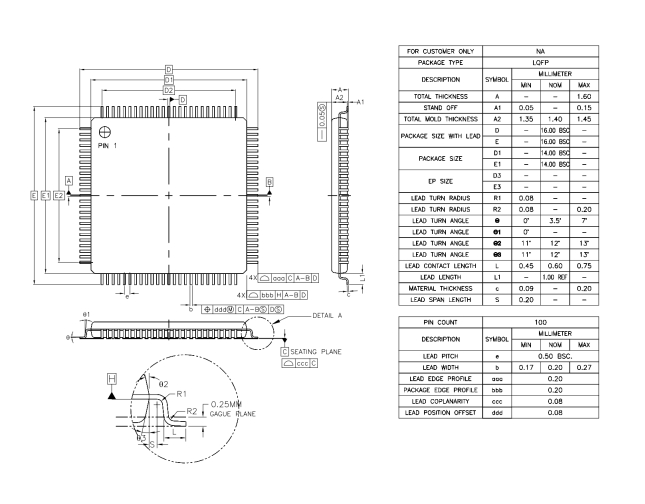

AG32VH407VGT6:LQFP-100封装

上海易硅智能科技是AGM Micro官方指定的授权代理商,旨在推广AGM各系列芯片,我们有专业的技术人员,可为客户提供本地化的服务。

指导设计选型、程序移植、方案定制,必要时可提供【代开发】服务。