SAR ADC 的常见架构

SAR ADC 架构有很多,像noise sharping SAR ADC、Pipeline SAR ADC、2bit/cycle SAR ADC、二进制冗余SAR ADC、非二进制冗余SAR ADC等,这里只讲普通的SAR ADC 架构(不涉及DAC分段架构、DAC全部是电容组成)

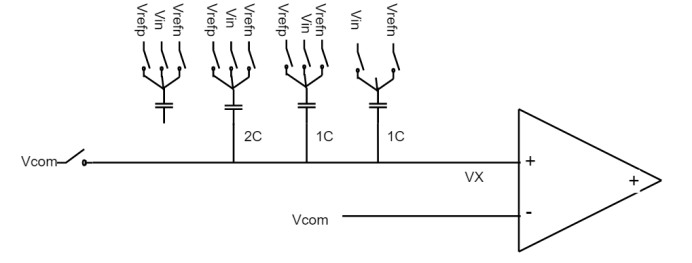

架构一:底板采样+单端SAR ADC+逻辑1:先置位再比较

采样阶段:接Vin的开关闭合,接Vcom的开关闭合

转换阶段:接Vin的开关断开,同时最高位接Vrefp,其它位接Vrefn,另外,接Vcom的开关断开,DAC输出浮空为Vx

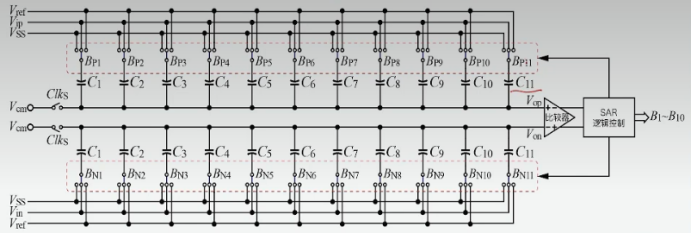

架构二:底板采样+差分SAR ADC+逻辑1:先置位再比较

采样阶段:电容下极板接Vip/Vin,上极板接Vcom

转换阶段:对于正端电容阵列,先猜测Bi=1,下极板接Vref,其它接0,上极板浮空形成Vop;对于负端电容阵列,先猜测bi=0,下极板接0,其它接vref,上极板浮空形成Von

架构三:底板采样+差分Split SAR ADC+逻辑2:先比较再置位,但电容不减半