《微机原理与接口技术》第 8 章 常用接口芯片

8.1 可编程定时/计数器8253/8254

8.1.1 8253的外部引脚及内部结构

8.1.2 8253的工作方式

8.1.3 8253的方式控制字和读/写操作

8.1.4 8253的初始化编程及应用

8.1.5 可编程定时/计数器8254

……

8.2 可编程并行接口8255

8.2.1 并行通信的概念

(1)并行通信与串行通信

数据通信:随着多计算机系统的应用和计算机网络的发展,计算机与外部设备之间,计算机与计算机之间常常要进行数据交换,这些数据交换可称为数据通信。

数据通信方式有两种:并行通信、串行通信。

并行通信:指数据的各位同时进行传送的通信方式,可以字或字节为单位并行进行。

并行通信速度快,但所用的通信线多、成本高,故不宜进行远距离通信。计算机内部各种总线都是以并行方式传送数据的。(近距离、大量、快速数据通信)

串行通信:指数据逐位顺序传送的通信方式。

串行传送的速度低,但只需要很少的通信线,适用于长距离而速度要求不高的场合。在网络中传送数据纯大多数采用串行方式。

(2)并行接口

无论是并行通信还是串行通信,它们在I/O接口与CPU之间的通信而言,均是以并行通信方式传送数据的。

并行通信由并行接口完成,它以字节(或字)为单位与I/O设备或被控对象进行数据交换,以同步方式传输。

例如打印机接口,A/D、D/A转换器接口,IEEE 488接口,开关量接口,控制设备接口等。

从并行接口的电路结构来看,它有硬连线接口和可编程接口之分。

硬连线接口的工作方式及功能用硬连线的不同方式来设定,不能用软件编程的方法加以改变;

可编程接口的工作方式及功能可以用软件编程的方法加以改变。

本节将对可编程并行接口8255进行讨论。

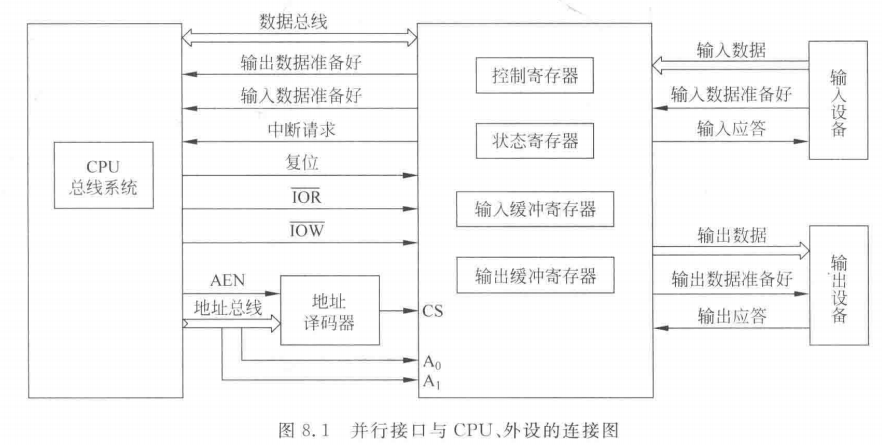

一个并行接口中包括状态信息、控制信息和数据信息,这些信息分别存放在状态寄存器、控制寄存器和数据缓冲寄存器中。

① 状态寄存器

状态寄存器用来存放外设的信息,CPU通过访问这个寄存器来了解某个外设的状态,进而控制外设的工作,以便与外设进行数据交换。

② 控制寄存器

并行接口中有一个控制寄存器和一个状态寄存器,CPU对外设的操作命令都寄存在控制寄存器中,状态寄存器主要是用来提供外设的各种状态位,以供CPU来查询。

③ 数据缓冲寄存器

在并行接口中还设置了输入缓冲寄存器和输出缓冲寄存器,缓冲器是用来暂存数据的。这是因为外设与CPU交换数据时,CPU的速度远远高于外设的速度。例如,打印机的打印速度与CPU的速度相差的远不止一个数量级。在并行接口中设置缓冲器,把要传送的数据先放入缓冲器中,打印机按照安排好的打印队列进行打印,这样可以保证输入、输出数据的可靠性。

图8.1是一个典型的并行接口与CPU、外设的连接图。

(3)数据输入过程

数据输入过程是指外设向CPU输入数据的过程。

① 当外设将数据通过数据输入线送给接口时,先使状态线“输入数据准备好”为高电平,然后通过接口把数据送到输入缓冲寄存器中,同时把“输入应答”信号置成高电平1发给外设。

② 外设接到应答信号后,将撤销“输入数据准备好”信号。在接口收到数据后,它会在状态寄存器中设置“准备好输入”状态位,以便CPU对其进行查询。

③ 接口向CPU发出一个中断请求信号,这样CPU可以用软件查询方式或中断的方式将接口中的数据输入到CPU中。

④ CPU在接收到数据后,将“准备好输入”的状态位自动清除,并使数据总线处于高阻状态,准备外设向CPU 输入下一个数据。

(4)数据输出过程

数据输出过程是指CPU向外设输出数据的过程。

① 当外设从接口接收到一个数据后,接口的输出缓冲寄存器“空”,使状态寄存器的“输出数据准备好”状态位置成高电平1,这表示CPU可以向外设接口输出数据,这个状态位可供 CPU查询。

② 此时接口也可向CPU发出一个中断请求信号,同上面的输入过程相同,CPU可以用软件查询方式或中断的方式将CPU中的数据通过接口输出到外设中。当输出数据送到接口的输出缓冲寄存器后,再输出到外设。

③ 与此同时,接口向外设发送一个启动信号,启动外设接收数据。外设接收到数据后,向接口回送一个“输出应答”信号。

④ 接口接收到该信号后,自动将接口状态寄存器中的“准备好输出”状态位重新置为高电平1,通知CPU可以向外设输出下一个数据。

8.2.2 8255外部引脚及内部结构

8255是Intel公司生产的一种通用的可编程并行I/O接口芯片,它有3个并行I/O口,又可通过编程设置多种工作方式,价格低廉,使用方便,可以直接与Intel系列的芯片连接使用,在中小系统中有着广泛的应用。

在IBM-PC/XT系列微机中,8255接口用于接收键盘输入的扫描码和系统配置的 DIP开关状态,以及用于扬声器控制和存储器奇偶校验。

(1)8255内部结构

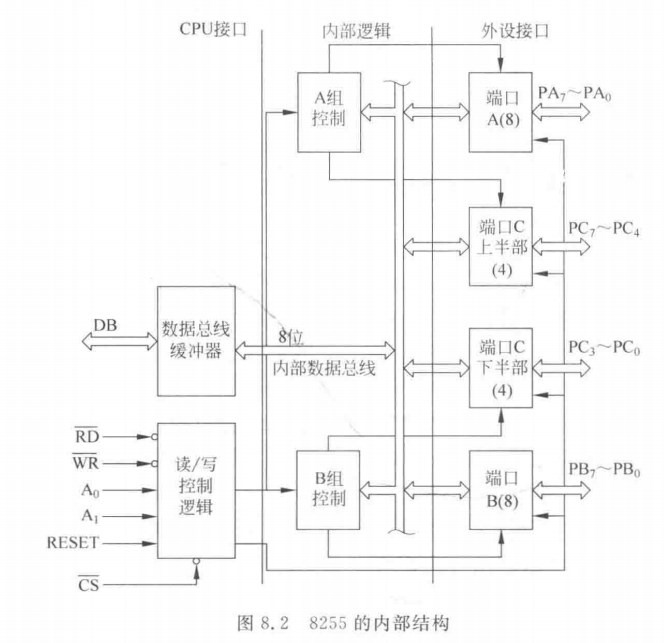

8255是一个40根引脚的双列直插式组件,内部结构:

① 3个8位I/О数据端口:A口、B口、C口。

② 1个8位的控制端口。

8255的内部结构如图8.2所示:

① 面向CPU的接口电路

a. 数据总线缓冲器:数据总线缓冲器是一个三态双向的8位缓冲器,是8255与系统数据总线的接口。与此关联的接口信号线是数据线D7~D0,它直接与CPU数据总线相连,以实现CPU与8255接口之间的信息传递。CPU向8255写入控制字或从8255中读状态信息,,以及所有数据的输入和输出,都需要通过数据缓冲器来进行传递。

b. 读/写控制逻辑:读/写控制逻辑是8255内部完成读/写控制功能的部件,它接收来自CPU的地址和控制信号,并依据这些信号,通过内部控制逻辑向8255的各功能部件发出读/写控制命令,用于管理数据、控制字或状态字的传送。与此部分有关的有6根信号线:片选信号~CS,读信号~RD,写信号~WR,端口选择信号A1、A0,以及 RESET复位信号。

② 面向外设的接口电路

8255提供了3个输入/输出通道可与外部设备相连接。每一个通道有一个8位的数据端口用于输入和输出,其工作方式可由编程设定,具体介绍如下。

a. 端口A:包含一个8位的数据输出锁存/缓冲器和一个8位的数据输入锁存器,与之关联的接口线是PA7~PA0。

b. 端口B:包含一个8位的数据输入/输出、锁存/缓冲器和一个8位的数据输入缓冲器,与之关联的接口线是PB7~PB0。

c. 端口C:包含一个8位的数据输出锁存/缓冲器和一个8位的数据输入锁存器。必要时端口C可分成两个4位端口,分别与端口A和端口B配合工作,以输出控制信号,或者接收从外设输入的状态信号,与之关联的接口线是PC7~PC0。

③ 内部控制逻辑

内部控制逻辑:A组控制部件、B组控制部件。

A组控制部件:控制端口A和端口C的高4位(PC7~PC4);

B组控制部件:控制端口B和端口C的低4位(PC3~PC0)。

控制逻辑内部设置了一个控制寄存器,接收来自CPU的控制字(一个字节),根据控制字的内容决定各数据端口的工作方式。也可以根据控制字对端口C的每一位进行置位和复位。控制寄存器的内容只能写入而不能读出。

(2)8255的引脚功能

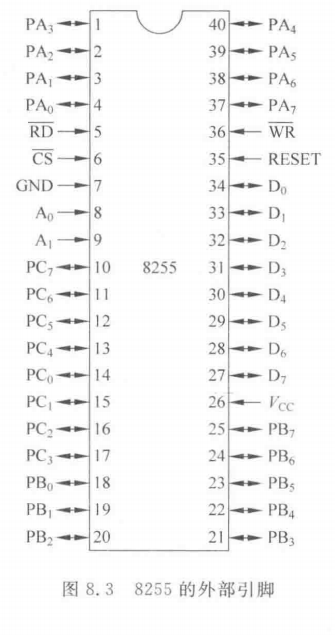

8255芯片有40根引脚,各引脚信号如图8.3所示。

8255的各引脚功能定义如下。

D7~D0(输入/输出、三态):双向三态数据线,用来传送数据、控制字和状态字等信息,直接与系统数据总线相连。

RESET(输入):复位信号,高电平有效。当它有效时,所有寄存器,包括控制寄存器的内容全部清零,A口、B口、C口均被设定为输入方式。

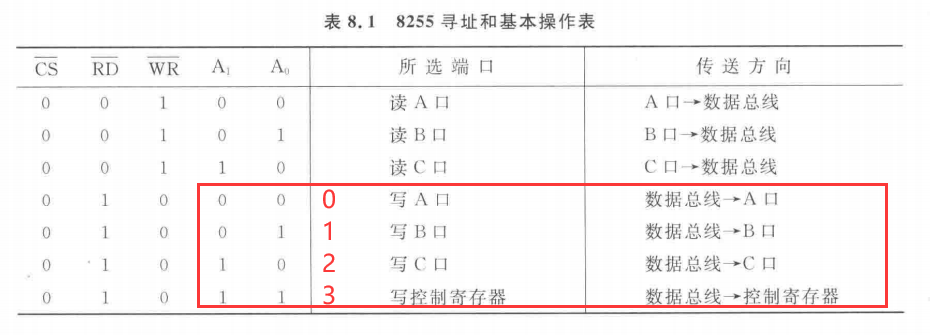

A1、A0(输出):端口选择信号。8255内部共有4个端口,即3个数据端口(A口、B口、C口)和一个控制端口(控制寄存器),它们可由程序寻址。A1、A0的不同编码可分别寻址上述4个端口,它们与片选信号~CS一起决定8255各端口的地址,规定A1A0为00、01、10、11时,分别选中端口A、端口B、端口C、控制端口。A1、A通常与系统总线的低位地址线相连。

~RD(输入):读信号,低电平有效。当它为低电平时,CPU 从 8255中读取数据或状态信息。通常接系统总线的~IOR信号。

~WR(输入):写信号,低电平有效。当它为低电平时,CPU将数据或命令字写入8255。通常接系统总线的~IOW信号。

~CS(输入):片选信号,低电平有效。当它为低电平时,选中8255芯片。通常由系统总线的高位地址线经译码得到。

A1A0和~RD、~WR、~CS信号相配合可对各端口进行输入/输出访问,其组合逻辑功能如表8.1所示。

PA7~PA0(输入/输出、三态):A口的8根输入/输出信号线。可用软件编程决定这8条线是工作于输入、输出还是双向方式。

PB7~PB0(输入/输出、三态):B口的8根输入/输出信号线。可用软件编程指定这8条线作输入还是输出。

PC7~PC0(输入/输出、三态):C口的8根输入/输出信号线。这8条线根据其设定的工作方式可作输人或输出线使用,也可用作控制信号的输出或状态信号的输入。

8.2.3 8255的工作方式

8255提供如下3种工作方式。

(1)方式0———基本输入/输出方式

(2)方式1———选通输入/输出方式

(3)方式2———双向传送方式。

端口A:可工作于3种工作方式(方式0、方式1、方式2);

端口B:可工作于两种工作方式(方式0、方式1);

端口C:可工作于方式0。

端口C常常根据控制命令分成两个4位端口,每个4位端口包含一个4位的输入缓冲器和一个4位的输出锁存器,它们分别配合A口和B口输出控制信号和输入状态信号。

(1)工作方式0(基本输入/输出方式)

它适用于简单的无条件输入/输出数据或查询式输入/输出数据的场合。

① 无条件数据的传送过程中:输入/输出数据随时都处于准备好状态,8255与CPU及外设之间无须交换应答(握手)信号;

② 查询式数据的传送过程中:需要有应答信号,通常A口与B口作为输入/输出数据端口,而C口分为两个4位端口分别作为控制信号输出口和状态信号输入口,用于配合A口和B口的查询式数据传送。

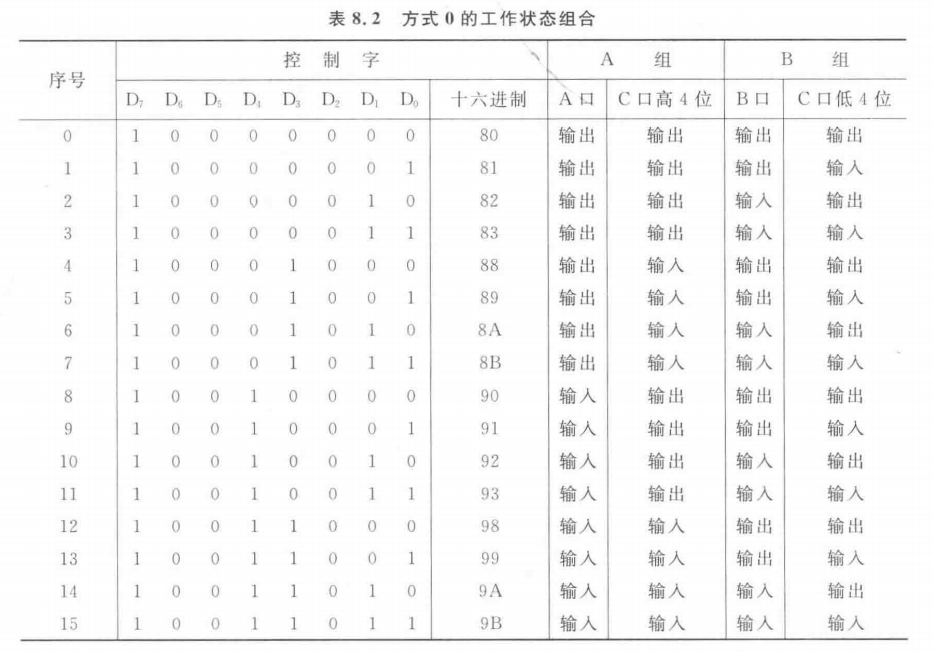

当A口、B口、C口都工作于方式0时,8255各口的输入/输出有16种组合,如表8.2所示。

(2)工作方式1(选通输入/输出方式)

……

(3)工作方式2(双向输入/输出方式)

……

8.2.4 方式控制字及状态字

(1)8255的控制字

8255有3种基本工作方式,而且对C口各位又可以进行按位操作。

CPU通过向8255内部的控制寄存器写入不同的控制字来选择不同的工作方式和位操作。

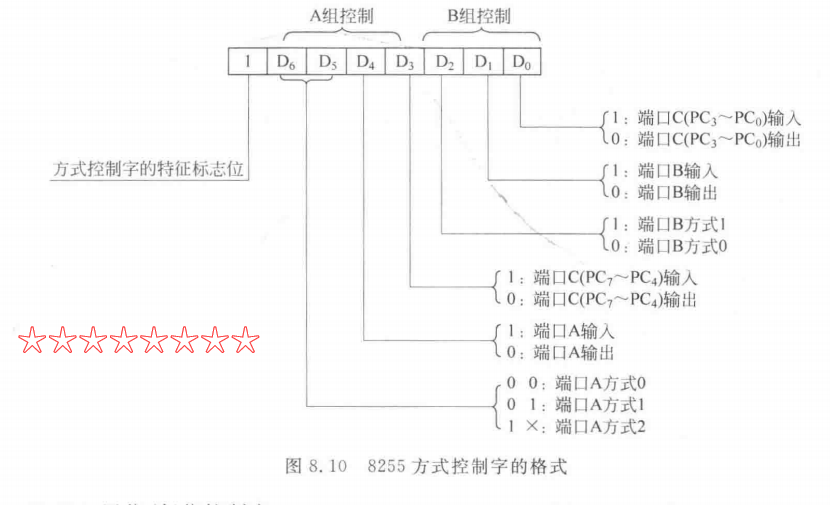

① 方式控制字

方式控制字用来决定8255的工作方式。它将3个通道分为两组:即A口和C口的高4位作为一组(A组),B口和C口的低4位作为一组(B组)。

方式控制字的格式如图8.10所示。

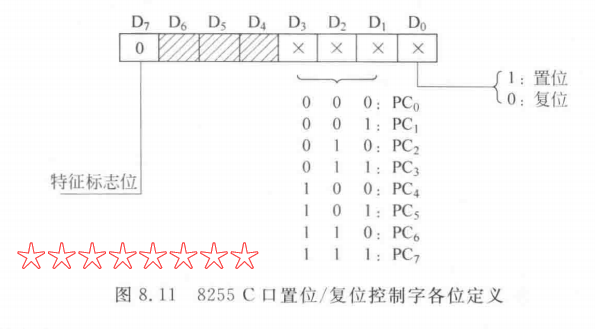

② C口置位/复位控制字

置位/复位控制可对C口中的任意一位进行置位或者复位操作。该控制字各位定义如图8.11所示。

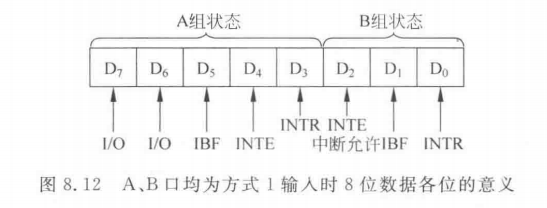

(2)8255的状态字

8255的状态字为查询式输入/输出数据提供了外设的工作状态,如IBF、~OBF、INTR等。根据8255工作在不同的工作方式下,以及各端口作输入、输出的不同情况,状态字的格式有所不同。值得注意的是,C口的状态字与C口各位对外的引脚状态不完全一致。

当8255的A口、B口工作在方式1或A口工作在方式2时,通过读C口的状态,可以检测A口和B口的状态。

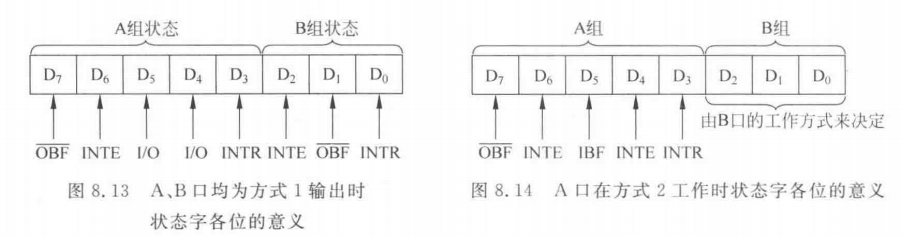

当8255的A口和B口均工作在方式1的输入时,由C口读出的8位数据各位的意义如图8.12所示。

当8255的A口和B口均工作在方式1的输出时,由C口读出的状态字各位的意义如图8.13所示。

当8255的A口工作在方式2时,状态字各位的意义如图8.14所示。

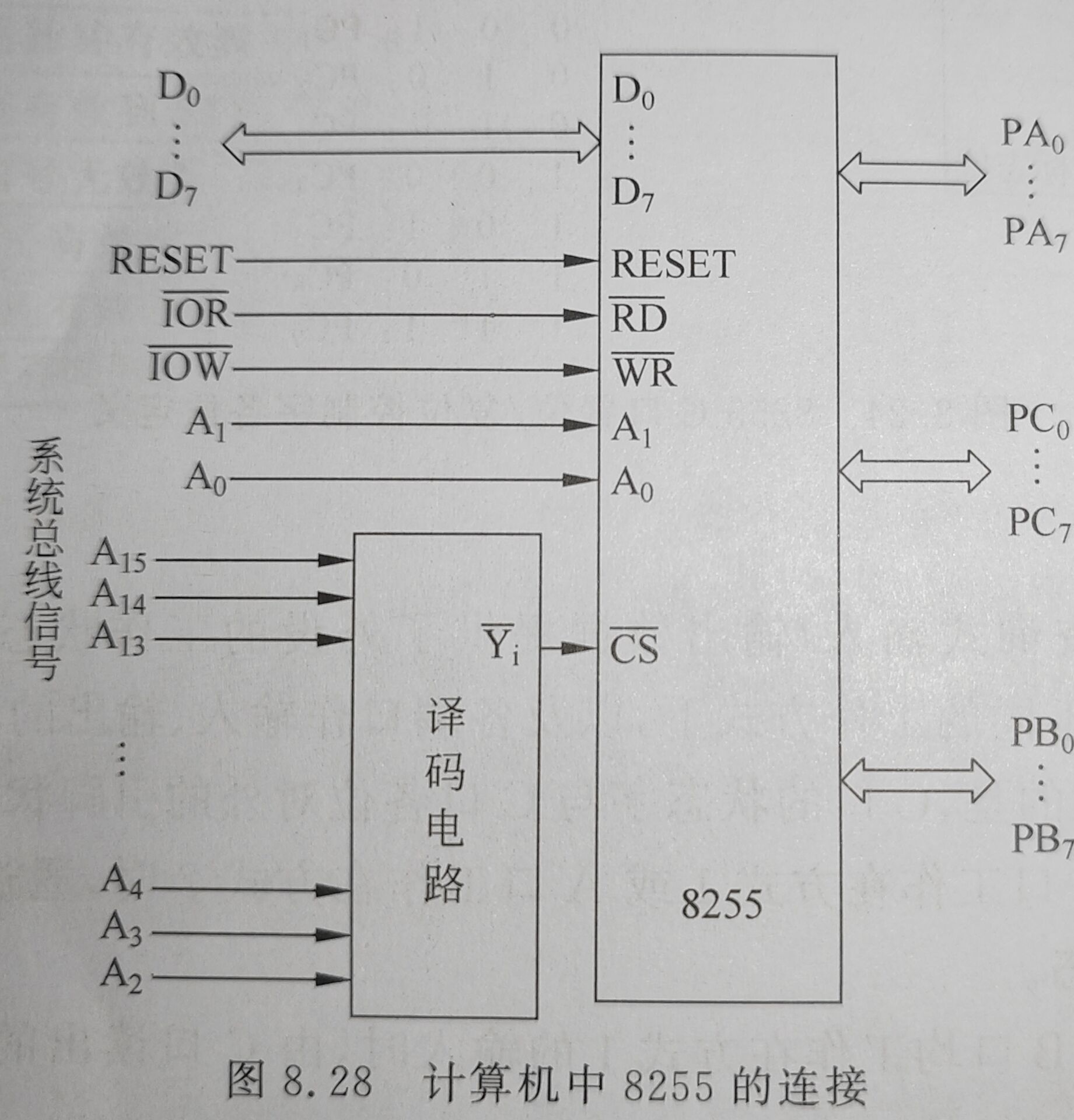

8.2.5 8255与CPU的连接

8255占用4个I/O端口地址,即A口、B口、C口和控制寄存器。

在8255的连接使用中:

① 它的8根数据线D7~D0与系统数据总线相连。

② A1、A0分别接地址总线的A1和A0。

③ 地址总线高位A15~A2经译码器译码后接片选信号~CS。

④ 控制信号线RESET、~RD、~WR分别与系统控制总线的RESET、~IOR、~IOW信号相连,如图8.15所示。

8.2.6 8255应用举例

8255A初始化时,先要写入控制字,以指定它的工作方式,然后才能通过编程,将总线上的数据从8255A输出给外设,或者将外部设备的数据通过8255A送到CPU中。

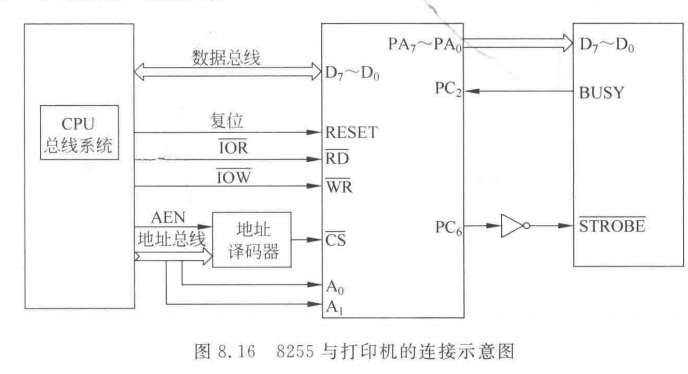

【例8.1】利用8255方式0实现打印机的接口

打印机可以打印计算机送来的 ASCII码字符。因为ASCII码为8位,所以我们利用8255A口的工作方式0来实现打印机与CPU之间的并行输出接口,8255与打印机的连接示意图如图8.16所示。

假设,8255由地址译码决定的A口、B口、C口及控制寄存器的端口地址分别为380H、381H、382H、383H。用A口的 PA7~PA0与打印机的D7~D0相连,作为打印字符的输出数据线。

当接口将数据送至打印机的输入线D7~D0上时,利用一个负的锁存脉冲~STROBE将数据锁存于打印机内部,并开始打印处理。同时,打印机送出高电平的BUSY信号,表示打印机正忙,一旦 BUSY变为低电平,则表示打印机又可以接收新的数据了。

在实现打印机接口时,可以设置A组、B组均工作在方式0下,使A口的PA7~PA0与打印机的D7~D0相连,并利用C口的PC6作为输出信号接打印机的选通端~STROBE,PC2作为输入信号接打印机的忙信号BUSY。

由此可以作如下的初始化:A口为输出,C口的高4位为输出、低4位为输入,B口保留,A、C口均工作于方式0。

初始化程序如下:

MOV AL,1 00 00 001B ;将控制字送AL中1 00 00 001B

MOV DX,0383H ;将控制寄存器端口地址送DX中

OUT DX,AL ;设置控制寄存器内容——决定工作方式MOV AL, 00001101B ;将PC6设置为1

OUT DX, AL ;设置控制寄存器内容——决定C口的内容

若要将BL中的字符送到打印机输出,则可用下面程序来完成。

MOV DX,0382H ;将C口地址送DX中

PWAIT:IN AL, DX ;输入C口数据AND AL,04H ;测试 PC2JNZ PWAIT ;忙则等待MOV AL,BL ;将BL中的打印字符送回AL中MOV DX, 0380H ;将A口地址送DX中OUT DX, AL ;将AL字符送出打印MOV AL,0CHMOV DX,383HOUT DX,AL ;设置C6为0INC ALOUT DX,AL ;设置C6为1

利用下面一段程序,可以完成一批字符数据的打印输出。假设要打印的字符串位于当前数据段从DATA 开始的内存区域中,字符串长度在 BLAK单元中。

PRINT: MOV AL,BLAKMOV CL,ALMOV SI,OFFSET DATA

GOON: MOV DX,0382H

PWAIT:IN AL, DXAND AL,04HJNZ PWAITMOV AL,[SI]MOV DX, 0380HMOV DX, ALMOV AL,00HMOV DX,0382HMOV DX,ALNOPNOPMOV AL,40HMOV DX,ALINC SIDEC CLJNZ GOONRET

【例8.2】……

【例8.3】……

8.3 可编程串行接口8251

8.3.1 串行通信概述

8.3.2 8251的外部引脚及内部结构

8.3.3 8251的控制字及其工作方式

8.3.4 8251串行接口应用举例

……

8.4 模拟I/O接口

8.4.1 DAC及其与CPU的接口

8.4.2 ADC及其与CPU的接口

……

8.5 例题解析

……

8.6 本章实验项目

……