数字电子技术基础(五十九)——脉冲触发的触发器

目录

1 脉冲触发的触发器

1.1 脉冲触发的主从SR触发器

1.2 脉冲触发的JK触发器

1.3 脉冲触发的D触发器

1.4 脉冲触发器的动作特点

1 脉冲触发的触发器

脉冲触发的触发器(Pulse-Triggered Flip-Flop)是一种数字电路中的时序元件,它检测到输入时钟的特点脉冲边沿(上升沿或者下降沿)时才会发生改变。例如对于上升沿触发的触发器,时钟信号从低电平到高电平的转换时刻(上升沿)采样输入。

1.1 脉冲触发的主从SR触发器

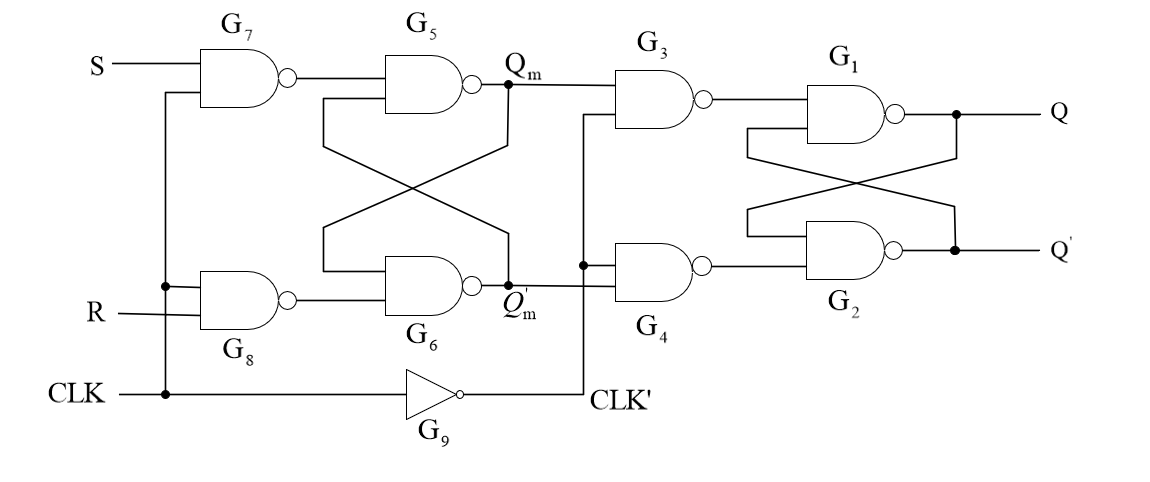

主从SR触发器是一种脉冲触发的时序逻辑电路,由两个SR锁存器级联构成。脉冲触发的SR触发器的电路图如下所示:

对于上图的SR触发器

(1)当CLK=1时,“主”按S、R翻转,“从”保持。

(2)当CLK的下降沿到达时,主“保持”。

在上升沿,主触发器开启,从触发器关闭;而在下降沿,此时主触发器关闭,从触发器开启。输入信号是在CLK为高电平时进入,而Q和Q'是在CLK的下降沿发生变化。

“从”根据“主”状态翻转,所以每个CLK周期,输出状态只可能保持一次。

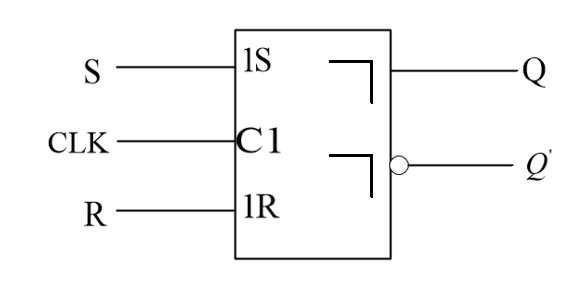

脉冲触发的SR触发器的图形符号如下所示:

真值表如下所示:

(上表中×表示最后结果“0”和“1”不能确定)

1.2 脉冲触发的JK触发器

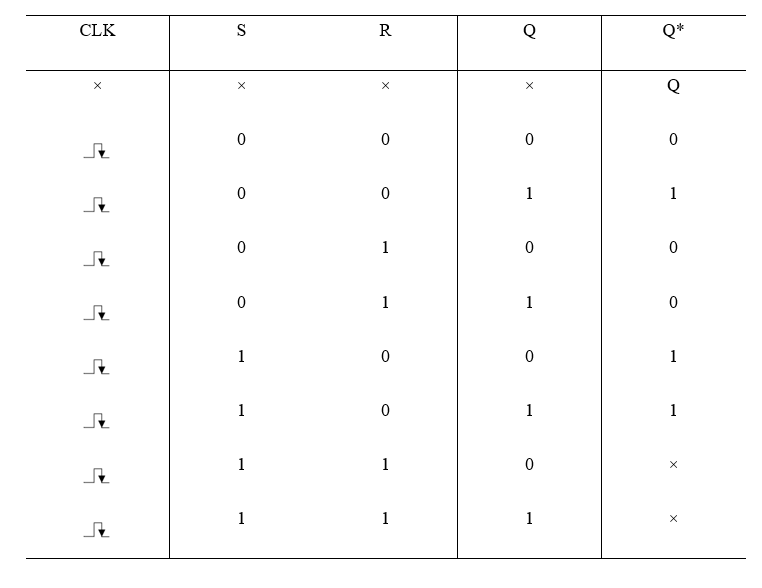

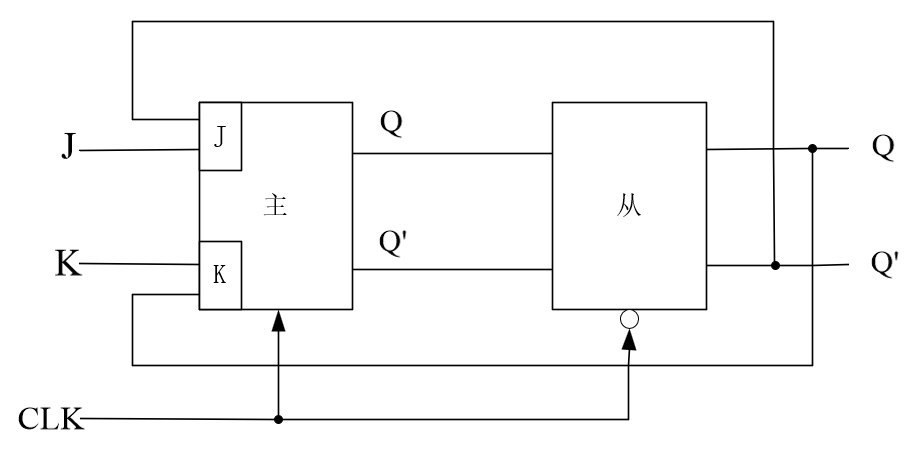

脉冲触发的JK触发器是一种改进型的主从结构触发器,它在SR触发器的基础上解决了 S=R=1 时的不确定状态问题,并引入了翻转功能。脉冲触发的JK触发器的电路图如下所示:

可以将上图简化为:

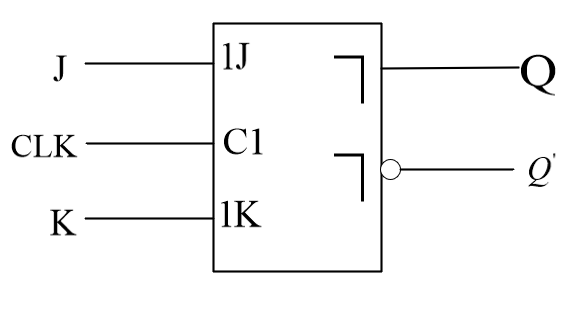

脉冲触发的JK触发器的图形符号如下所示:

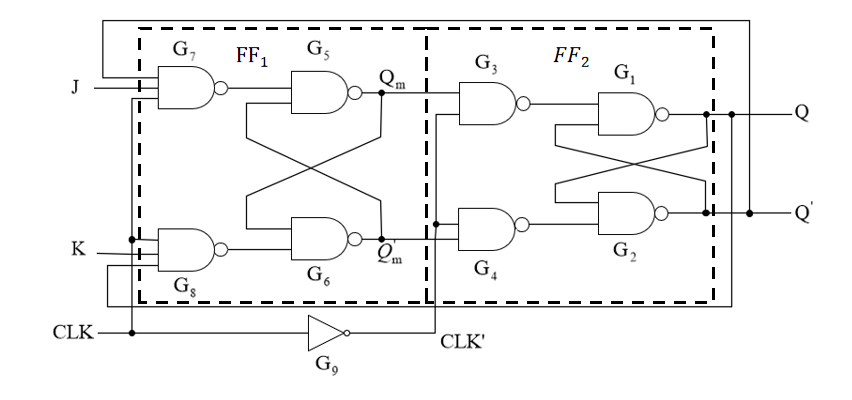

下面开始分析上面电路各个状态下的输出状态:

- 当J=1、K=0时,则CLK=1时主触发器置1(原来是0置成1,原来是1保持);当CLK=0以后,从触发器随主触发器置1。

- 当J=0、K=1时,则CLK=1时主触发器置0;当CLK=0以后,从触发器随着主触发器置0。

- 当J=K=0时,由于门

、

被封锁,触发器保持的状态不变,即Q*=Q。

- 当J=K=1时,分为两种情况。第一种情况是Q=0,此时

被Q端的低电平封锁,CLK=1时仅

输出低电平信号,所以主要触发器置1,当CLK=0时,从触发器也跟着置0;另一种情况Q=1,这时候门

被Q'端的低电平所封锁,因此当CLK=1时仅

能给出低电平信号,所以主触发器被置0.当CLK=0以后从触发器也跟着置0,故Q*=0。因此,可以总结为当J=k=1时,CLK下降沿到达后触发器将翻转为初态相反的状态。

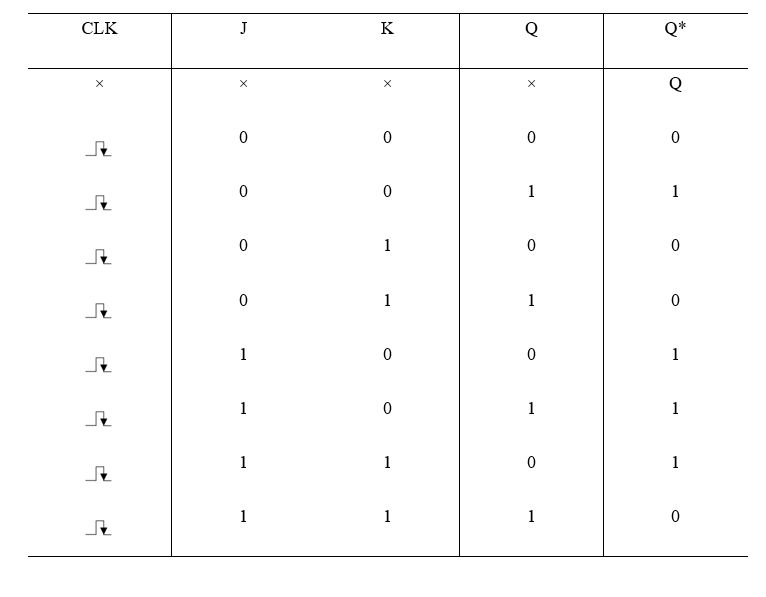

因此脉冲触发的JK触发器如下所示:

可以看到, 脉冲触发的JK触发器是一种改进的主从结构触发器,它对于脉冲出发点SR触发器解决了S=R=1时不确定的状态,并且引用了翻转的状态。

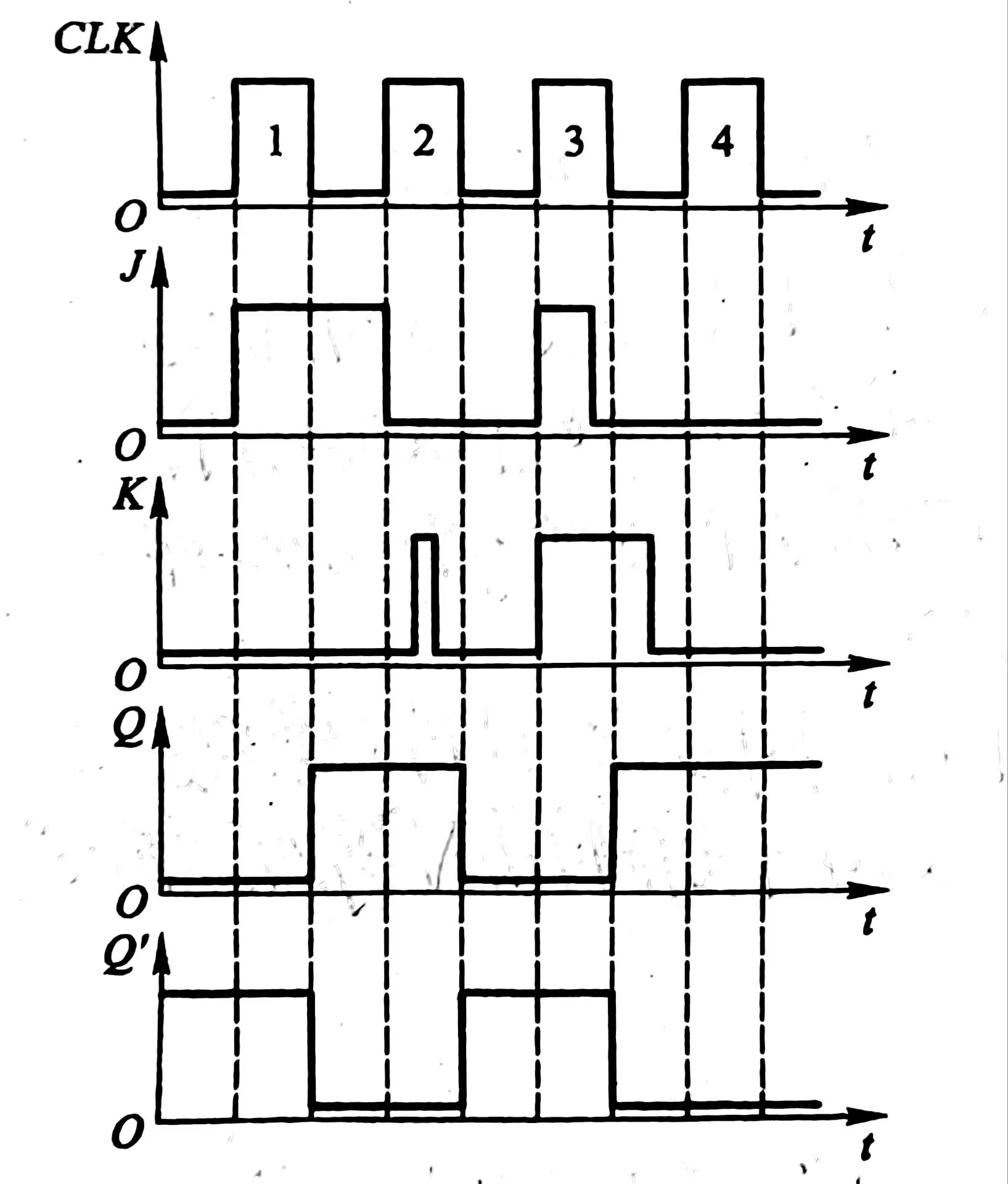

脉冲触发的JK触发器的波形图如下所示:

在第一个CLK时钟周期内,CLK为低电平,JK触发器内部不发生变化;在第二个CLK时钟周期内,CLK为高电平,J=1、K=0,此时JK触发器的主触发器发生改变,从触发器保持,到了下一个CLK下降沿到达的时候触发器置1;在第二个CLK为高电平的时钟周期内出现了J=0、K=1的情况,此时主触发器便被置0,所以虽然CLK下降沿到达时输入状态回到了J=K=0,但从触发器仍按主触发器的状态被置0,即Q*=0。

第三个CLK为高电平时钟内,首先出现了J=k=1的状态,CLK下降沿达到之前主触发器被置1,然后出现了J=0、K=1,但是一个CLK周期内仅仅只能变化一次,后面的变化是无效的,因此CLK下降沿到达之后从触发器被置1。这种情况可以总结为:主从结构触发器,在时钟信号等于1期间只能变一次,只能发生一次变化

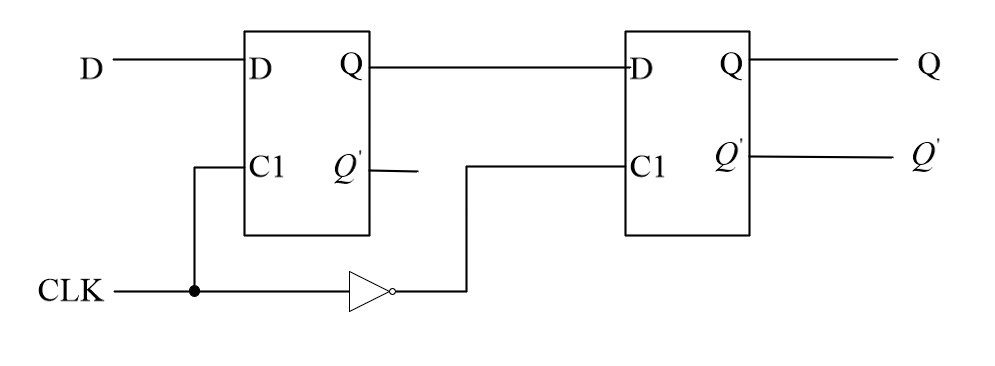

1.3 脉冲触发的D触发器

与脉冲触发的SR触发器和JK触发器相类似,脉冲触发的D触发器是一种常见的时序逻辑电路元件,它在数字系统中广泛用于数据存储和同步。脉冲触发的D触发器在时钟脉冲的特定边沿(通常是上升沿)对输入数据进行采样和存储。电路图如下所示:

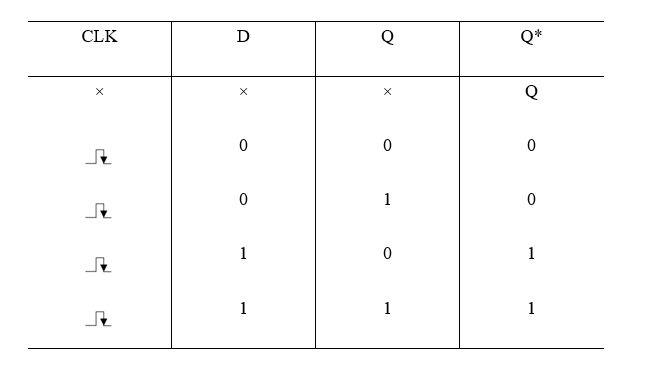

脉冲触发的D触发器的真值表如下所示意:

1.4 脉冲触发器的动作特点

脉冲触发器的特点包括如下内容:

(1)分两步动作。首先第一步,当CLK=1时,主触发器接受信号,从触发器保持。第二步,当CLK=0时,从触发器按照主触发器的状态进行翻转。

(2)因为主触发器本身就是一个电平触发SR触发器,所以在CLK=1的全部时间里输入信号都将对主触发器起控制作用。